Fターム[5B125BA12]の内容

リードオンリーメモリ (43,397) | メモリ種別 (5,638) | マスクROM (109) | 配線接続 (41)

Fターム[5B125BA12]に分類される特許

1 - 20 / 41

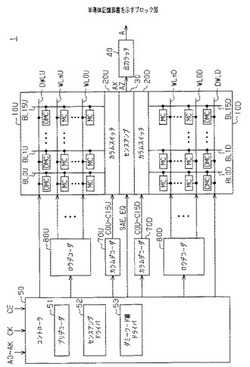

半導体記憶装置及びデータ読み出し方法

【課題】レイアウト面積の増大を抑制することができる半導体記憶装置を提供する。

【解決手段】半導体記憶装置1は、2つのメモリセルアレイ10U,10Dと、それら2つのメモリセルアレイ10U,10Dで共有されるセンスアンプ30と、メモリセルアレイ10U,10Dからのデータ読み出しを制御する制御回路50とを有している。メモリセルアレイ10Uは、m本のワード線WL0U〜WLmUと、n本のビット線BL0U〜BL15Uと、これらワード線WL0U〜WLmUとビット線BL0U〜BL15Uの交差点に設けられたメモリセルMCと、ビット線BL0U〜BL15Uとダミーワード線DWLUとの交差点に設けられたダミーセルDMCとを有している。制御回路50は、一方のメモリセルアレイからデータを読み出す場合に、他方のメモリセルアレイのダミーワード線を活性化してダミーセルによりセンスアンプ30のリファレンスレベルを生成する。

(もっと読む)

半導体記憶装置

【課題】ゲート面積に依存するトランジスタばらつきを抑制し、読み出し動作を高速化した半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、ロウ方向に延びるワード線WL、カラム方向に延びる複数のビット線BL0,BL1,BL2で構成されたビット線グループ、並びに、トランジスタからなりワード線及びビット線グループの交差部に設けられたメモリセル、を有するメモリセルアレイと、ビット線を介してメモリセルからデータを読む読み出し回路とを備え、メモリセルは、トランジスタのソース又はドレインを、ビット線グループに属する複数のビット線BL0,BL1,BL2のいずれとも接続しないか又はいずれか1本とだけ接続するかの異なる接続状態を有し、トランジスタのゲートとなるアクティブ領域AAは、ビット線グループの複数のビット線BL0,BL1,BL2の配置領域及び各ビット線間のスペースに連続的に形成されている

(もっと読む)

多値ROMセル及び半導体装置

【課題】集積度が高く、製造ばらつきの影響が小さく、製造歩留まりの高い多値ROMセルを提供する。

【解決手段】多値ROMセルは、ROMセルトランジスタTrと、複数のビット線BT1〜BT3と、第1金属配線31〜44とを具備している。ROMセルトランジスタTrは、基板表面の領域に設けられている。複数のビット線BT1〜BT3は、基板表面の上方に設けられ、Y方向に伸び、Z方向に並んで配置されている。第1金属配線31〜44は、ROMセルトランジスタTrのソース・ドレイン22の一方に接続され、複数のビット線BT1〜BT3の各々の近傍にまで連なる。第1金属配線31〜44は、複数のビット線BT1〜BT3のうちのいずれかに接続されているか、又は、いずれにも接続されていない。

(もっと読む)

半導体記憶装置

【課題】電力消費をより低減可能な新たなビット線階層化方式を備えた半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、行列状に設けられた複数のメモリブロックBと、複数のメモリブロックBに対応して設けられた複数の主ビット線GLとを具備する。メモリブロックBは、行列状に設けられた複数のメモリセルCと、列ごとに設けられた複数の副ビット線BLと、列及び行ごとに設けられ、複数のメモリブロックBに共通である複数のワード線WLと、対応する主ビット線GLを複数の副ビット線BLのいずれかに接続するスイッチ回路SCとを備える。読出し対象の対象セルC1の読出し動作時に、対象セルC1に対応する主ビット線GL1を選択し、対象セルC1の列に対応する副ビット線BL1をスイッチ回路SC1により選択し、複数のワード線WLのうち、対象セルC1の列及び行に対応するワード線WL1を選択する。

(もっと読む)

記憶装置、集積回路装置及び電子機器

【課題】製造コストの増加を抑止して不揮発性メモリーセルとマスクROMメモリーセルとを混在できる記憶装置、集積回路装置及び電子機器等を提供すること。

【解決手段】記憶装置は、複数のメモリーセルME1、ME2、MR1、MR2と、複数のワード線WL1、WL2と、複数のビット線BL1、BL2と、複数のソース線SL1、SL2とを含む。複数のメモリーセルのうちの第1のグループのメモリーセルは、電気的にデータの書き込み及び消去が可能な不揮発性メモリーセルME1、ME2である。複数のメモリーセルのうちの第2のグループのメモリーセルは、マスクによりデータが設定されるマスクROMメモリーセルMR1、MR2である。マスクROMメモリーセルMR1、MR2は、ソースと対応するソース線SL2とを電気的に接続するためのコンタクトCN1、CN2の有無によってデータが設定される。

(もっと読む)

複数ビット値を格納するための読み出し専用メモリセル

【課題】複数ビット値を格納するための読み出し専用メモリセルを開示する。

【解決手段】該読み出し専用メモリセルは、少なくとも3本の出力線であって、該少なくとも3本の出力線のそれぞれは、異なる複数ビット値を表す、少なくとも3本の出力線と、該3本の出力線のうちの1本と電圧源との間に接続される切り替え装置とを含む。該切り替え装置は、切り替え信号に応答して、該電圧源と該3本の出力線のうちの1本との間の電気接続を提供し、該接続された出力線の電圧は、既定の電圧への接続に応答して値を切り替え、それによって、該出力線によって表される該複数ビット値が選択される。該選択された複数ビット値を出力するための、出力装置も提供する。

(もっと読む)

不揮発性半導体記憶装置

【課題】製造技術の限界によりトランジスタの最小サイズが決まるため、ROMの高容量化にも限界があるという課題があった。

【解決手段】本発明の不揮発性半導体記憶装置は、EEPROMとマスクROMとを一体とした不揮発性半導体記憶装置であり、メモリトランジスタの電荷蓄積膜に蓄える電荷の有無によりデータを記憶するEEPROMと選択コンタクトホールの有無によりデータを記憶するマスクROMとを同一平面上に構成する。これにより、トランジスタサイズを小さくすることなく、ROM容量を増やすことが可能となる。

(もっと読む)

半導体集積回路

【課題】マスクROMを内蔵した半導体集積回路において、トランジスタのリーク電流の増加や不純物拡散領域の抵抗値の増加等を招くことなく、メモリセルアレイのレイアウト面積を削減する。

【解決手段】この半導体集積回路は、マスクROMを内蔵した半導体集積回路であって、該マスクROMが、第1の方向において隣接する2つのNチャネルトランジスタのソースが共通化され、第1の方向と直交する第2の方向において隣接する複数のNチャネルトランジスタのソースが分離されているようにした複数のメモリセルと、各々のポリシリコンが第2の方向に並んだ1行のメモリセルに含まれている全てのNチャネルトランジスタのゲートを構成すると共に、所定の位置において第1の方向及び第1の方向と反対の方向に凸部を有するようにした複数のワード線とを具備する。

(もっと読む)

メモリ

【課題】スタンバイ時に導電層からダイオードを介してビット線に電流がリークするのを抑制することが可能なメモリを提供する。

【解決手段】このクロスポイント型のダイオードROM(メモリ)は、複数のワード線WLに交差するように配置される複数のビット線BLと、ワード線WLに沿って延びるように設けられる導電層2cと、導電層2cとビット線BLとが交差する位置に配置され、導電層2cにカソードが接続されるダイオード3を含むメモリセル4と、メモリセル4に記憶されるデータが読み出されるソース線S0(S1〜S3)とを備え、スタンバイ時に導電層2cまたはビット線BLの一方がフローティング状態になるように構成されている。

(もっと読む)

メモリ

【課題】スタンバイ時のリーク現象を評価するための試験を行う際の時間を短縮することが可能なメモリを提供する。

【解決手段】このクロスポイント型のダイオードROM(メモリ)は、導電層2cと、導電層2cにカソードが接続されるダイオード3を含むメモリセル4と、メモリセル4に記憶されるデータが読み出されるソース線S0(S1〜S3)と、ソース/ドレイン領域の一方がビット線BLに接続され、ソース/ドレイン領域の他方がHレベルの電位(VDD)に接続され、スタンバイ時のリーク現象を評価するための試験を行う際にオン状態となるnチャネルトランジスタ5とを備える。

(もっと読む)

半導体記憶装置

【課題】高速動作に有利な半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、複数のワード線と複数のビット線との交差位置にマトリクス状に配置される複数のメモリセルを有するメインメモリセルアレイ11Mと、前記複数のワード線とダミービット線との交差位置に配置される複数のダミーメモリセルを有するダミーカラム11Dとを備えるメモリセルアレイ11と、前記ダミーメモリセルのダミー読み出し電流の電流値を、前記メモリセルの第1,第2状態の読み出し電流の電流値の間となるように制御するダミー読み出し電流制御部15と、入力を前記第1,第2状態の読み出し電流および前記ダミー読み出し電流とし、これらの電流を比較して出力するセンスアンプ14SAを備えるセンス部14とを具備する。

(もっと読む)

半導体記憶装置

【課題】シングルエンドセンスアンプにより高速読み出しを可能とし、関連技術で設けられていたダミーメモリセルを不要とし、回路面積を縮減し、消費電力を低減する。

【解決手段】ビット線をグランド電位に放電するディスチャージ回路102と、シングルエンド入力構成のセンスアンプ108と、電源とセンスアンプの入力ノードSAin間に接続され、前記センスアンプの入力ノードからオン状態のカラム選択トランジスタ(N0、N1、・・・)を介してビット線を充電する充電用のトランジスタ106と、を備え、読み出し時、選択されたメモリセルが接続するビット線からグランドへの電流パスがオフ状態とされる場合、前記充電用のトランジスタ106により、前記センスアンプの入力ノードが充電されて電位が上昇し前記カラム選択トランジスタをオフさせた状態で前記センスアンプの入力ノードをさらに充電した後、読み出し動作が行われる。

(もっと読む)

新規ROMセルアレイ構造

【課題】メモリセルのセンスマージン低下を防止するメモリセルアレイ構造を提供する。

【解決手段】半導体メモリセルアレイは、長尺状に連続する活性領域220と、活性領域220に形成され、第1のメモリセル210[i]を構成する第1トランジスタと、活性領域220に形成され、第2のメモリセル210[i+1]を構成する第2トランジスタとを備える。第2のメモリセル210[i+1]は、活性領域220の長尺方向に沿って第1のメモリセル210[i]に最も近接する。半導体メモリセルアレイはさらに、第1及び第2トランジスタ間において活性領域220上に形成された分離ゲート235を備える。分離ゲート235は第1及び第2トランジスタのゲートとほぼ同じ構造を有し、所定電圧の供給を受けることにより、活性領域220において分離ゲート235の下方の部分を流れる活性電流を遮断する。

(もっと読む)

メモリ

【課題】消費電流(消費電力)が増加するのを抑制することが可能なメモリを提供する。

【解決手段】このメモリ(ダイオードROM)は、複数のワード線8と、複数のビット線11と、ワード線8に対して平行に延びるように設けられた導電層9と、導電層9とビット線11とが交差する位置に配置されるメモリセル12と、所定の数のメモリセル12ごとに設けられ、ワード線8と導電層9とを接続する複数のトランジスタ10とを備えている。そして、隣接するトランジスタ10によって挟まれる所定の数のビット線11がそれぞれ配置される第1ブロックおよび第2ブロックにおいて、データの読み出し時に同時に選択される第1ブロックのビット線11の第1ブロックの端部を基準とする位置と、第2ブロックのビット線11の第2ブロックの端部を基準とする位置とが異なるように構成されている。

(もっと読む)

メモリ

【課題】消費電流(消費電力)が増加するのを抑制することが可能なメモリを提供する。

【解決手段】このメモリ(ダイオードROM)は、複数のワード線7と、複数のビット線10と、ワード線7に対して平行に延びるように設けられた導電層8と、導電層8とビット線10とが交差する位置に配置されるメモリセル11と、所定の数のメモリセル11ごとに設けられ、ワード線7と導電層8とを接続する複数の裏打ち配線9とを備えている。そして、隣接する裏打ち配線9によって挟まれる所定の数のビット線10がそれぞれ配置される第1ブロックおよび第2ブロックにおいて、データの読み出し時に同時に選択される第1ブロックのビット線10の第1ブロックの端部を基準とする位置と、第2ブロックのビット線10の第2ブロックの端部を基準とする位置とが異なるように構成されている。

(もっと読む)

メモリ

【課題】消費電流(消費電力)が増加するのを抑制するとともに、メモリセルのアクセス時間が長くなるのを抑制することが可能なメモリを提供する。

【解決手段】このメモリ(ダイオードROM)は、複数のワード線WLと、複数のワード線WLに交差するように配置される複数のビット線BLと、複数のワード線WLの各々に接続され、対応するワード線WLが選択されることによりオン状態になる選択トランジスタ2と、選択トランジスタ2のソース/ドレイン領域の一方にカソードが接続されるダイオード3をそれぞれ含む複数のメモリセル4と、選択トランジスタ2のソース/ドレイン領域の他方側に接続されるソース線S0〜S3と、ソース線S0〜S3に接続され、選択されたメモリセル4から読み出されるデータを判別するためのデータ判別回路11とを備え、ビット線BLの駆動能力は、ビット線BLが配置される位置によって異なるように構成されている。

(もっと読む)

半導体集積回路装置

【課題】不揮発性メモリを内蔵する半導体集積回路装置において、高速動作が可能であり、かつ、メモリの集積度を上げることができる技術を提供する。

【解決手段】ワード線WLと、ビット線BLT,BLBから成る相補ビット線と、コモンソース線CS,CS1,CS2と、ワード線WL及び前記相補ビット線に接続されたメモリセルMCとを有し、メモリセルMCは、MOSトランジスタM1,M2を備え、MOSトランジスタM1,M2のゲート電極は、ワード線WLに接続され、MOSトランジスタM1のドレイン電極は、相補ビット線BLTに接続され、MOSトランジスタM2のドレイン電極は、相補ビット線BLBに接続され、MOSトランジスタM1,M2の各ソース電極が、コモンソース線CS,CS1,CS2のいずれか1つに接続され、またはフローティング状態とされることにより、メモリセルMCに記憶情報が記憶される。

(もっと読む)

半導体記憶装置

【課題】回路規模を殆ど増加させずに、誤動作を防止できるNAND型のマスクROMを提供する。

【解決手段】制御回路30A内に遅延素子とANDゲートからなるタイミング回路を設け、プリチャージ信号PCが“H”になったときには一定の遅延時間が経過した後で“H”になり、このプリチャージ信号PCが“L”になったときには直ちに“L”になる遅延プリチャージ信号PCDを生成する。そして、遅延プリチャージ信号PCDが“L”の期間に、デコーダ80Aによりビット線BLを強制的に接地電位GNDに接続させ、遅延プリチャージ信号PCDが“H”となったときに、データ読み出し回路20からプリビット線PBLにプリチャージ電圧VDDを印加する。これにより、プリチャージの直前にビット線BLとプリビット線PBL上の電荷が放電され、読み出し誤りが防止できる。

(もっと読む)

半導体装置

【課題】ROMを含んだ半導体装置において、安定した読み出し動作を実現する。

【解決手段】例えば、各メモリセル(例えばMC0)を2個のNMOSトランジスタ(MN40t,MN40b)で構成し、MN40tのドレインを相補ビット線の一方となるビット線BLTmに接続し、MN40bのドレインを相補ビット線の他方となるビット線BLBmに接続する。そして、MN40tのソースをコモンソース線CSmに接続し、MN40bのソースを電源電圧VDDに接続する。例えば、MC0を読み出す際には、BLTm,BLBmがプリチャージ状態で、ワード線WL0を活性化し、コモンソース線CSmをVDDレベルからVSSレベルに駆動する。これに伴いBLTmがVSSに、BLBmがVDDに接続され、これらを差動増幅することで、ノイズマージンが大きい安定した読み出し動作が可能となる。

(もっと読む)

半導体記憶装置

【課題】読み出し動作を安定させることで、回路定数の再調整や物理データの再設計を不要とし、製品コストの増大を回避可能な半導体記憶装置を提供する。

【解決手段】ワード線WLと、ビット線BLと、ワード線WL及びビット線BLに接続されたメモリセルMCと、ワード線WL及びビット線BLをそれぞれ選択するロウデコーダ13及びカラムデコーダ12とを具備する半導体記憶装置であって、ロウデコーダ13によってワード線WLが選択されるタイミングで、制御信号を生成する制御信号生成回路21aと、ビット線BLの電位を検知し、検知された電位がハイレベルの場合に制御信号に応じた電流をビット線BLに供給することで、ビット線BLの電位をハイレベルに保持する保持回路22とを備える。

(もっと読む)

1 - 20 / 41

[ Back to top ]