Fターム[5B125CA27]の内容

リードオンリーメモリ (43,397) | 目的、効果 (6,321) | 劣化対処、ストレス緩和 (354)

Fターム[5B125CA27]に分類される特許

1 - 20 / 354

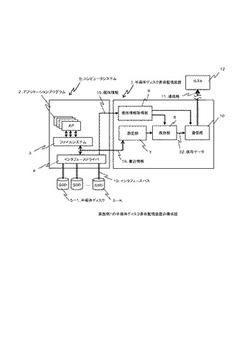

半導体ディスク寿命監視装置

【課題】不揮発性の半導体ディスクの寿命を監視する半導体ディスク寿命監視装置を提供する。

【解決手段】半導体ディスク5−1〜5−Kの書込み制御を行うファイルシステム3と、当該ファイルシステム3と前記半導体ディスク5−1〜5−Kを接続するインタフェースドライバ4を備え、当該インタフェースドライバ4により書込みが行われる半導体ディスク5−1〜5−Kの寿命を予測する半導体ディスク寿命監視装置1であって、前記ファイルシステム3からの書込みを書込情報として測定する測定部7と、前記測定結果を累積し第1の保存データ32として保存する保存部8と、前記保存した累積書込情報に基づいて、半導体ディスク5−1〜5−Kの寿命を予測する。

(もっと読む)

不揮発性半導体記憶装置

【課題】読出動作の精度を向上させた不揮発性半導体記憶装置を提供する。

【解決手段】メモリストリングは、半導体基板の上方に設けられ、複数のメモリセルを含む。制御回路は、複数のメモリセルのうち、選択メモリセルに保持されたデータを読み出す読出動作を実行する。メモリストリングは、半導体層、電荷蓄積層、及び導電層を有する。半導体層は、半導体基板に対して垂直方向に延びメモリセルのボディとして機能する。電荷蓄積層は、半導体層の側面に設けられ、電荷を蓄積可能とされる。導電層は、半導体層と共に電荷蓄積層を挟むよう設けられメモリセルのゲートとして機能する。制御回路は、読出動作の実行前に、選択メモリセル及び非選択メモリセルを導通状態としてメモリストリングの一端から他端へと電流を流すリフレッシュ動作を実行する。

(もっと読む)

不揮発性半導体記憶装置および不揮発性半導体メモリの情報書き換え方法

【課題】不揮発性半導体メモリの書き換え時に、適切なパルス電圧および適切なパルス幅を備える信号を印加可能な不揮発性半導体記憶装置を提供することである。

【解決手段】本発明にかかる不揮発性半導体記憶装置は、記録されている情報を所定のパルス電圧および所定のパルス幅を備える信号を印加することで書き換え可能な不揮発性半導体メモリ11と、不揮発性半導体メモリ11の書き換えを制御する書き換え制御部12と、を備える。書き換え制御部12は、不揮発性半導体メモリの総書き換え回数に基づき仮のパルス電圧および仮のパルス幅の少なくとも一つを決定する。更に、決定された仮のパルス電圧および仮のパルス幅の少なくとも一つを不揮発性半導体メモリ11の温度に基づいて補正することで、書き換え時に不揮発性半導体メモリ11に印加する信号のパルス電圧およびパルス幅の少なくとも一つを決定する。

(もっと読む)

不揮発性メモリ装置のデータリード方法、及びそれを行う装置

【課題】新たなリードパラメータで不揮発性メモリ装置をリードするリードリトライを行う方法、該方法を行う装置を提供する。

【解決手段】リードリトライ動作及び/またはその部属的なリードリトライ動作は、リードリトライ動作が保証(warranted)されるか否かを判断する前に初期化されるか、完了することができる。例えば、NANDフラッシュメモリ装置のページは、新たなリード電圧レベルをページのワードラインに印加して、リードリトライ動作でリードされうる。例えば、リードリトライ動作は、エラー訂正動作でターゲットページのデータの以前リードページのエラーを訂正不能と判断される前に、ターゲットページで行われる。

(もっと読む)

不揮発性半導体記憶装置

【課題】メモリセルの劣化による影響を考慮した読み出し動作を実行できる不揮発性半導体記憶装置を提供する。

【解決手段】一の実施の形態に係る不揮発性半導体記憶装置は、メモリセルアレイと、読み出し動作及び書き込みベリファイ動作を制御する制御回路とを備える。制御回路は、第1の場合に、選択ワード線に印加する電圧を第1の書き込みベリファイ電圧又は第1の読み出し電圧に設定して、動作を行う。制御回路は、第1の場合よりもメモリセルの劣化が進んだ第2の場合に、選択ワード線に印加する電圧を第2の書き込みベリファイ電圧又は第2の読み出し電圧に設定して、動作を行う。制御回路は、第1の書き込みベリファイ電圧の最大値と第1の読み出し電圧の最大値との差を、第2の書き込みベリファイ電圧の最大値と第2の読み出し電圧の最大値との差よりも大きい値に設定する。

(もっと読む)

半導体集積回路及びその制御方法

【課題】デカップリング容量素子の信頼性と、フラッシュメモリの動作モードに対応した供給電流の補償を損なわずに、フラッシュメモリの面積増加を抑制する。

【解決手段】本発明に係る半導体集積回路10は、フラッシュメモリ部12と、フラッシュメモリ部12に電圧を供給する昇圧回路13と、昇圧回路13の出力に一端が接続されたデカップリング容量素子15と、フラッシュメモリ部12の動作モードに応じて、デカップリング容量素子15の他端の電位を制御する制御回路14とを備える。

(もっと読む)

半導体記憶装置

【課題】動作信頼性を向上出来る半導体記憶装置を提供すること。

【解決手段】実施形態の半導体記憶装置1は、メモリセルMTと、複数のワード線WLと、ドライバ回路12と、制御回路15とを備える。メモリセルMTは、半導体基板20上に積層されると共に、電流経路が直列接続され、電荷蓄積層25bと制御ゲート23a〜23dとを含む。ワード線WLは、制御ゲートにそれぞれ接続される。ドライバ回路12は、選択ワード線に第1電圧VPGMを印加すると共に、第1非選択ワード線に第2電圧VPASSAを印加し、第2非選択ワード線に第3電圧VPASS、VISOを印加するプログラム動作を繰り返すことにより、選択ワード線に接続されたメモリセルMTにデータを書き込む。制御回路15は、プログラム動作が繰り返される過程において、第1電圧VPGMを上昇させ、第2電圧VPASSAを低下させる。

(もっと読む)

半導体記憶装置

【課題】書き込み/消去の繰り返しによる信頼性の低下を抑制することが可能な半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、ウェル上にトンネル絶縁膜を介して形成された浮遊ゲートに蓄積する電荷量を制御することにより電気的にデータを書き換え可能な複数のメモリセルを備える。半導体記憶装置は、前記ウェル、及び前記浮遊ゲート上に絶縁膜を介して形成された制御ゲートに、電圧を印加する制御回路を備える。

前記メモリセルの消去動作において、前記制御回路は、第1の消去電圧が階段状に上昇する第1のパルス波を、前記ウェルに印加し、その後、第2の消去電圧の第2のパルス波を、前記ウェルに印加する。

(もっと読む)

メモリシステム

【課題】高品質なメモリシステムを提供する。

【解決手段】メモリシステム1は、データ保持可能な不揮発性の半導体記憶部2と、半導体記憶部2の温度を計測する温度計測部9a、9bと、半導体記憶部2の温度を変化させる温度可変部8と、ホスト機器11から受信したデータを半導体記憶部2に転送する転送部、温度計測部9a、9bからの温度情報を記憶する温度記憶部、及び温度記憶部に記憶された温度情報に基づいて、温度可変部8を制御する温度制御部を具備する制御回路5と、を具備する。

(もっと読む)

不揮発性半導体記憶装置

【課題】メモリセルに保持されたデータの信頼性を向上させることを可能にした不揮発性半導体記憶装置を提供する。

【解決手段】一態様に係る不揮発性半導体記憶装置は、メモリセルアレイ、及び制御回路を有する。メモリセルアレイは、複数の閾値電圧分布を保持可能に構成された複数のメモリセル、及び複数のメモリセルのゲートに共通接続された複数のワード線を含む。制御回路は、メモリセルに少なくとも一部が負の閾値電圧分布を与え、これによりメモリセルのデータを消去する消去動作の実行後、メモリセルに正の複数通りの閾値電圧分布のうち最も低い閾値電圧分布を与える複数回の第1書込動作を実行する。制御回路は、複数回の第1書込動作の実行時に消去動作及び第1書込動作を除くその他の動作を実行させる第1実行命令をコントローラから受け付けた場合、複数回の第1書込動作の間にその他の動作を実行する。

(もっと読む)

カップリングチャネルを使用したアンチヒューズメモリ及びその操作方法

【課題】カップリングチャネルを使用したアンチヒューズメモリ及びその操作方法を提供する。

【解決手段】カップリングチャネルを使用したアンチヒューズメモリは、第1導電型の基板と、第2導電型のドープ領域と、カップリングゲートと、ゲート誘電層と、アンチヒューズゲートと、アンチヒューズ層と、を含む。基板中に隔離構造を有する。ドープ領域が基板中に設置され、且つドープ領域及び隔離構造の間にチャネル領域を定義する。カップリングゲートがドープ領域及び隔離構造の間の基板上に設置され、且つカップリングゲートとドープ領域と隣り合う。ゲート誘電層がカップリングゲート及び基板の間に設置される。アンチヒューズゲートがカップリングゲート及び隔離構造の間の基板上に設置され、アンチヒューズゲート及びカップリングゲートの間に間隔を有する。アンチヒューズ層がアンチヒューズゲート及び基板の間に設置される。

(もっと読む)

熱アシスト誘電体電荷トラップメモリ

【課題】

誘電体電荷トラップメモリの動作速度及び/又は耐久性を向上させる技術を提供する。

【解決手段】

メモリデバイスは、ワードライン及びビットラインを含む誘電体電荷トラップ構造メモリセルのアレイを含む。該アレイに、読み出し、プログラム及び消去の動作を制御するように構成された制御回路が結合される。コントローラは、該アレイのメモリセル内の誘電体電荷トラップ構造を熱アニールする支援回路を備えるように構成される。熱アニールのための熱を誘起するために、ワードラインドライバ及び前記ワードライン終端回路を用いて、ワードラインに電流を誘起することができる。熱アニールは、サイクルダメージからの回復のために、通常動作とインターリーブされて適用されることが可能である。また、熱アニールは、消去のようなミッション機能中に適用されることもでき、それにより該機能の性能を向上させ得る。

(もっと読む)

ダイオードストラッピングを備えた熱アシストフラッシュメモリ

【課題】フラッシュメモリの動作速度及び耐久性を向上させる技術の提供。

【解決手段】メモリが、行及び列を含むメモリセルのアレイを有している。該メモリは、アレイ内の単数又は複数のワード線上の第1の離隔位置のセットに第1のバイアス電圧を印加するとともに、単数又は複数のワード線上の第2の離隔位置のセットに第1のバイアス電圧とは異なる第2のバイアス電圧を印加する、ワード線に結合された回路部を有し、第1の離隔位置のセットにおける位置は、第2の離隔位置のセットの位置の間に介在しており、それにより、第1の離隔位置のセットにおける位置と第2の離隔位置のセットにおける位置との間に、単数又は複数のワード線の加熱をもたらす電流の流れが誘導される。

(もっと読む)

記録再生装置

【課題】フラッシュメモリの劣化をより迅速に検出できる。

【解決手段】速度導出部180は、SSD136に対するデータの読み書き速度を導出する。速度保持部138は、速度導出部が導出した読み書き速度を保持する。劣化判定部182は、任意の時点のSSDに対するデータの読み書き速度の、速度保持部に保持されている任意の時点より前の読み書き速度に対する変化率を導出し、導出された変化率が所定の閾値以下となると、SSDが劣化していると判定する。報知部184は、劣化判定部が、SSDが劣化していると判定した場合、その旨報知する。

(もっと読む)

半導体記憶装置

【課題】読み出しストレス(Read Stress)を減少でき、読み出し不良(Read Disturb不良)の減少に有利な半導体記憶装置を提供する。

【解決手段】実施形態によれば、半導体記憶装置は、電流経路が直列に接続される複数のメモリセルと、その両端に接続される選択トランジスタにより構成されるセルユニットを備えるメモリセルアレイ1と、前記メモリセルアレイに与える電圧を発生させる電圧発生回路7と、前記メモリセルアレイおよび前記電圧発生回路を制御する制御回路4とを具備する。前記メモリセルのデータ読み出し動作において、前記制御回路4は、前記セルユニットの非選択ワード線に与えられる電圧を、第1読み出しパス電圧に達するまでの第1傾きθVR1が、前記選択トランジスタの選択電圧に達するまでの傾きθVSGよりも小さくなるように、かつ、前記非選択ワード線が、前記選択電圧よりも遅く立ち上げられるように制御する。

(もっと読む)

半導体装置及びその動作方法

【課題】プログラム動作の時にトンネル絶縁膜にトラップされた電子を短時間で容易に除去すること。

【解決手段】メモリセルのコントロールゲートにはプログラム電圧を印加し、半導体基板内に形成されたウェルにはデートラップ電圧を印加して前記メモリセルをプログラムする段階と、前記メモリセルを検証する前に、前記デートラップ電圧が前記ウェルに印加される間に前記コントロールゲートに前記デートラップ電圧より低い電圧を印加して、前記メモリセルのトンネル絶縁膜にトラップされた電子を除去する段階と、を含むことを特徴とする半導体装置の動作方法。

(もっと読む)

不揮発性半導体記憶装置

【課題】消去動作及びソフトプログラム動作の際のメモリセルの劣化の影響を抑制することのできる不揮発性半導体記憶装置を提供する。

【解決手段】一の実施の形態に係る不揮発性半導体記憶装置は、制御部を備える。制御部は、データ消去のため所定範囲のメモリセルに対し消去電圧を印加する消去動作、データ消去が完了したか否かを確認する消去ベリファイ動作、及びデータ消去が完了しなかった場合に消去電圧を所定のステップアップ値だけ上昇させるステップアップ動作を繰り返す制御を司る。制御部は、一連の消去動作時に消去電圧を印加した回数が第1の回数より大きく、第2の回数(第1の回数<第2の回数)未満の場合、所定範囲のメモリセルを過消去状態から第1の閾値電圧分布状態に設定するソフトプログラム動作を実行し、消去電圧を印加した回数が第1の回数以下、又は第2の回数以上の場合、ソフトプログラム動作を実行しないように構成されている。

(もっと読む)

不揮発性半導体記憶装置

【課題】書き込み時間の増大を抑制しつつ、しきい値分布の広がりを抑えることが可能な不揮発性半導体記憶装置を提供する。

【解決手段】消去回数カウント部7aは、メモリセルの消去回数をブロックB1〜Bn単位でカウントし、ステップアップ電圧変更部7bは、メモリセルの消去回数に基づいて、書き込み電圧VPGMをステップアップさせるステップアップ電圧ΔVPGMを変更する。

(もっと読む)

メモリシステム

【課題】1つの実施形態は、例えば、不揮発性メモリデバイスの信頼性を改善できるメモリシステムを提供することを目的とする。

【解決手段】1つの実施形態によれば、不揮発性メモリデバイスとモニタ部と変更部とを有することを特徴とするメモリシステムが提供される。不揮発性メモリデバイスは、データを記憶する。モニタ部は、前記不揮発性メモリデバイスに対するデータの書き込み処理及び消去処理による前記不揮発性メモリデバイスの特性をモニタする。変更部は、前記モニタされた前記不揮発性メモリデバイスの特性に応じて、前記書き込み処理に要する時間が目標値に一致するように、書き込み動作とベリファイ動作とが交互に繰り返される前記書き込み処理における書き込み開始電圧の値と書き込み電圧の増加幅との少なくとも一方を変更する。

(もっと読む)

半導体記憶装置

【課題】1つの実施形態は、例えば、出荷後においてメモリセルの動作特性を変更できる半導体記憶装置を提供することを目的とする。

【解決手段】1つの実施形態によれば、メモリセルアレイと記憶部と選択部と起動処理部と動作制御部とを有することを特徴とする半導体記憶装置が提供される。メモリセルアレイでは、複数のメモリセルが配列されている。記憶部は、選択される候補となる複数の動作パラメータを予め記憶する。選択部は、ユーザからの変更指示に応じて、前記複数の動作パラメータのうち前記メモリセルを動作させるために使用すべき動作パラメータを選択する。起動処理部は、ユーザからの起動指示に応じて、電源を起動するとともに、前記選択部により選択された動作パラメータを前記記憶部から読み出して使用可能な状態に設定する。動作制御部は、前記起動処理部により使用可能な状態に設定された動作パラメータを使用して、前記メモリセルを動作させる。

(もっと読む)

1 - 20 / 354

[ Back to top ]