Fターム[5B125EB09]の内容

リードオンリーメモリ (43,397) | EEPROMセルへの電荷注入、放出構成 (1,604) | 負電圧を利用するもの (175)

Fターム[5B125EB09]に分類される特許

1 - 20 / 175

不揮発性半導体メモリ素子、および不揮発性半導体メモリ装置

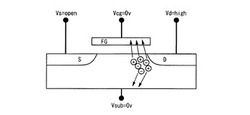

【課題】フローティングゲートへの電荷の蓄積と消去を容易に行え、またフローティングゲートの電荷を消去する場合にメモリセルの閾値を容易に制御できる、不揮発性半導体メモリ素子を提供する。

【解決手段】フローティングゲートへの電荷の蓄積時に、フローティングゲートとドレイン(またはソース)間に電圧を印加し、バンド・バンド間によるホットエレクトロンを半導体基板中に発生させ、フローティングゲートに電荷を注入する。また、フローティングゲートの電荷の消去時には、フローティングゲートとドレイン(またはソース)間に電圧を印加し、バンド・バンド間によるホットホールを発生させ、該ホットホールにより蓄積された電荷を消去する。また、フローティングゲートの電荷の消去時には、メモリセルのコントロールゲートとソース間の閾値が所望の値になるように制御しながら、電荷を消去する。

(もっと読む)

メモリのプログラミング方法及びメモリアレイ

【課題】クリティカル・ディメンションの変動に鈍感であり且つ高速なメモリプログラミング方法等を提供する。

【解決手段】メモリの複数のメモリセルの夫々は、ウェルと、ソース及びドレイン領域と、記憶レイヤと、ゲートとを有する。メモリセルはマトリクス状である。同じ列ドレイン領域は同じビットラインへ接続し、同じ行ゲートは同じワードラインへ接続し、同じ列ソース領域は同じソースラインへ接続する。メモリは、いずれかのメモリセルへ電気的に接続されたワードラインへ第1の電圧を印加し、そのメモリセルへ電気的に接続されたビットラインへ少なくともプログラミング閾値だけ第1の電圧と異なる第2の電圧を印加し、そのメモリセルへ電気的に接続されたソースラインへ少なくともプログラミング閾値だけ第1の電圧と異なる第3の電圧を印加し、複数のメモリセルへ基板電圧を印加することによって、プログラミングされる。

(もっと読む)

半導体装置

【課題】データ書き替えの繰り返しによってメモリセルの閾値電圧が下がりくくなることを防止する。

【解決手段】半導体装置1の各メモリセルMCは、共通の浮遊ゲートFGを有する第1のトランジスタ(読出用)TRAと第2のトランジスタ(書込用)とを含む。制御回路11は、一方のトランジスタに通電したときにメモリセルに流れる電流と、両方のトランジスタに通電したときにメモリセルに流れる電流とを比較することによって、第1および第2のトランジスタにそれぞれ接続されるサブビット線SBL_R,SBL_P間のショートを検出する。

(もっと読む)

不揮発性半導体記憶装置及びICカード

【課題】ピーク電流を低減する。

【解決手段】不揮発性半導体記憶装置10は、不揮発性メモリ11と、電圧発生回路24と、検知回路25とを含む。電圧発生回路24は、チャージポンプ30と、チャージポンプ30を動作させるクロックを生成するオシレータ32とを有し、かつ不揮発性メモリ11に電圧を供給する。検知回路25は、外部からの電源電圧を監視し、電源電圧が特定のレベルより低くなったことを検知する。電圧発生回路24は、電源電圧が特定のレベルより低くなった場合に、クロックの周波数を低くする。

(もっと読む)

半導体装置

【課題】メモリセルの劣化がある程度進行している状態と、要求仕様を満たさなくなるまで劣化が進行した状態とを外部で認識できるようにする。

【解決手段】半導体装置1において、メモリセルMCは、閾値電圧の相違を利用してデータを不揮発的に記憶する。制御回路11は、データ消去時、メモリセルの閾値電圧が第1ベリファイ電圧以下でない場合にはメモリセルに閾値電圧を小さくするための消去電圧を印加する。制御回路は、消去電圧の印加時間が第1の判定値を超えると第1の劣化状態を表わす信号を出力し、消去電圧の印加時間が第1の判定値より大きい第2の判定値を超えると第2の劣化状態を表わす信号を出力する。

(もっと読む)

不揮発性半導体記憶装置

【課題】メモリ容量を容易に調整することが可能な不揮発性半導体記憶装置を提供する。

【解決手段】このフラッシュメモリでは、Y方向に配列された4つのP型ウェルPWのうちの端の1つのP型ウェルPWに複数のメモリブロックMB0〜MB3を設け、残りの3つのP型ウェルPWにそれぞれ3つのメモリブロックMB10〜MB12を設ける。また、それぞれメモリブロックMB0〜MB3,MB10〜MB12のX方向に隣接してロウデコーダRD0〜RD3,RD10〜RD12を設ける。メモリブロックMB10〜MB12を削除してメモリ容量を減らす場合でも、周辺回路の再レイアウトが不要となる。

(もっと読む)

不揮発性半導体記憶装置及びそのデータ消去方法

【課題】消去時間を短縮する。

【解決手段】不揮発性半導体記憶装置10は、共通の半導体領域に設けられた複数のページを有し、複数のページの各々は電気的に書き換え可能な複数のメモリセルを有する、メモリセルアレイ11と、選択ページに対して消去動作を行う制御回路23と、消去動作後に、メモリセルアレイ11に対して消去し過ぎたメモリセルが存在するか否かを判定するベリファイ回路18とを含む。ベリファイ回路18は、選択ページの全メモリセルが閾値OEV1以上であるか否かを判定し、非選択ページのうち消去状態のメモリセルが閾値OEV1より低い閾値OEV2以上であるか否かを判定する。

(もっと読む)

不揮発性半導体記憶装置

【課題】メモリセルごとの消去回数を低減することで、フラッシュメモリの寿命を延ばす。

【解決手段】不揮発性半導体記憶装置3は、複数の半導体領域202の各々に設けられ、かつ直列に接続されたメモリトランジスタ及び選択トランジスタを有する複数の不揮発性メモリセルがマトリクス状に配置されたメモリセルブロックと、同一行にあるメモリトランジスタを共通接続するようにして、複数のメモリトランジスタのコントロールゲートに接続された複数のワード線WLと、同一行にある選択トランジスタを共通接続するようにして、複数の選択トランジスタのゲートに接続された複数の選択ゲート線SGとを含む。ロウデコーダ20は、消去動作時に、半導体領域に消去電圧を印加した状態で、データが消去される選択ワード線に負の第1の電圧を印加し、データが消去されない非選択ワード線に正の第2の電圧を印加する。

(もっと読む)

半導体メモリおよびシステム

【課題】 プリチャージ動作を不要にすることで、読み出しアクセス時間を短縮する。

【解決手段】 メモリセルは、第1電圧線と第2電圧線の間に接続ノードを介して直列に接続され、相補の論理を記憶する一対のセルトランジスタを有する。第1制御回路は、読み出し動作時に、一対のセルトランジスタのコントロールゲートを活性化レベルに設定する。第2制御回路は、読み出し動作時に、第1電圧線を第1電圧に設定し、第2電圧線を第1電圧より高い第2電圧に設定する。読み出し回路は、読み出し動作時に、接続ノードに生成される電圧に応じて、メモリセルに保持されている論理を判定する。これにより、読み出し動作において、メモリセルに保持されている論理に応じて、接続ノードを第1電圧または第2電圧に設定できる。

(もっと読む)

フラッシュEEPROM(FLASHEEPROMMEMORY)の消去方法

【課題】電荷の蓄積を制御することによりメモリセルを消去するフラッシュEEPROMの消去方法を提供する。

【解決手段】フラッシュメモリの消去方法は、F/Nトンネリング期間において、ウェル電極と第二半導体領域に対し正極性の第一電圧バイアスを印加し、且つコントロールゲート電極に対し負極性の第二電圧バイアスを印加するステップと、F/Nトンネリング期間のあとのトラップ減少期間において、ウェル電極と第二半導体領域に対し正極性の第三電圧バイアスを印加し、且つコントロールゲート電極に対し第一ゼロ電圧バイアスを印加するステップと、トラップ減少期間のあとのトラップアシストトンネリング期間において、コントロールゲート電極に対し負極性の第四電圧バイアスを印加し、且つウェル電極と第二半導体領域に対し第二ゼロ電圧バイアスを印加するステップと、を有する。

(もっと読む)

負電圧発生器、負電圧を利用するデコーダー、不揮発性メモリ装置及びメモリシステム

【課題】負電圧を発生し、負電圧を利用してプログラム動作及び読出し動作を遂行できる負電圧発生器、負電圧を利用するデコーダー、不揮発性メモリ装置及びメモリシステムを提供する。

【解決手段】ワードラインに負電圧を提供でき、ワードラインに負電圧が提供される時、負電圧を提供するための回路が形成されたウェルにも負電圧を提供する不揮発性メモリ装置。不揮発性メモリ装置は負電圧を発生し、負電圧を利用してプログラム動作及び読出し動作を遂行できる。

(もっと読む)

昇圧回路

【課題】寄生トランジスタに流れる電流を低減し、消費電流の増大を抑制することが可能な昇圧回路を提供すること。

【解決手段】本発明にかかる昇圧回路は、低電位側電源端子GNDと出力端子Voutとの間に設けられたダイオード素子D1,D2と、ダイオード素子D1,D2と出力端子Voutとの間に設けられ、ダイオード素子D1,D2よりも順方向降下電圧の小さいダイオード素子D3と、ダイオード素子D1,D2,D3の間の各接続点に一端が接続され、他端にクロック信号CLK1,CLK2が供給される容量素子C1,C2と、を備える。

(もっと読む)

半導体記憶装置

【課題】各データの閾値電圧の分布幅を狭くする必要があり、書き込み速度を高速化する

ことが困難であった。

【解決手段】半導体基板と、ワード線、及びビット線に接続され、直列接続された複数の

メモリセルがマトリックス状に配置されて構成されたメモリセルアレイと、前記ワード線

を選択する選択トランジスタと、入力データに応じて前記ワード線、ビット線の電位を制

御し、前記メモリセルに対するデータの書き込み、読み出し及び消去動作を制御する制御

回路とを具備し、前記選択トランジスタは、前記半導体基板のウェル上に形成され、書き

込み動作時に、前記ウェルには第2負電圧が入力され、所定の非選択ワード線には第3電

圧(第3電圧≧第2負電圧)が入力される。

(もっと読む)

不揮発性半導体メモリ

【課題】データ書込み時における電流量の変化を抑制し、メモリセルへのデータ書込みを高精度に行うことができる不揮発性半導体メモリを提供する。

【解決手段】複数のメモリセルと、複数のメモリセルに接続されたワード線と、複数のメモリセルの各々に接続されたビット線と、を含み、ビット線から少なくとも2つを選択し、選択されたビット線に接続されたメモリセルに対して、電源供給ラインから同時に電流を供給してデータを書込む不揮発性半導体メモリであって、複数のメモリセルの各々に蓄積された電荷量を測定する電荷量測定部と、ビット線の各々に接続された電流路切替回路と、を有し、選択されたビット線に接続された電流路切替回路は、電荷量測定部による電荷量の測定値に応じて、メモリセル又は所定端子のいずれかに対して選択的に電源供給ラインから電流を供給すること。

(もっと読む)

不揮発性メモリー装置、そのプログラム方法、不揮発性メモリー装置を含むメモリーシステム、電子装置及びシステム

【課題】カップリングノイズ、Vpass障害、及びVpgm障害による閾値電圧の変化を減らすことができる不揮発性メモリー装置、そのプログラム方法、不揮発性メモリー装置を含むメモリーシステム、電子装置及びシステムを提供する。

【解決手段】本発明の不揮発性メモリー装置は、複数の物理ページで構成されるメモリーセルアレイと、複数の物理ページが一次的にプログラムされた後に複数の物理ページが二次的にプログラムされるようにプログラム順序を定めるためのプログラムシーケンサーと、を備え、一次的なプログラム動作のプログラム状態P0は、二次的なプログラム動作のビットラインセットアップ区間で複数の物理ページに印加されるワードライン電圧より低いことを特徴とする。

(もっと読む)

不揮発性半導体メモリ、及び不揮発性半導体メモリへの書込み方法

【課題】不揮発性半導体メモリの周辺回路を小さくし、集積回路の縮小化に寄与する。

【解決手段】p型基板10に形成され、ソース線430と接続するn型拡散層50と、p型基板10上に設けられ、ワード線400と接続するワード電極200と、p型基板10とワード電極200の間に設けられたワード絶縁層と、n型拡散層50上、及びワード電極200の側壁に設けられたトンネル絶縁層と、トンネル絶縁層上に設けられた電荷蓄積層と、電荷蓄積層上に設けられたコントロール絶縁層と、コントロール絶縁層上に設けられ、コントロール線420と接続するコントロール電極300と、を備え、制御部は、メモリ素子600に書込みを行うときに、ソース線430に正電圧を印加し、ワード線400に負電圧を印加し、かつコントロール線420に正電圧を印加する不揮発性半導体メモリ。

(もっと読む)

不揮発性半導体記憶装置

【課題】ホットキャリア注入によって書き換えを行うスプリットゲート型MONOSメモリにおいて、リテンション特性を向上させる。

【解決手段】メモリセルM00の選択ゲート電極は選択ゲート線SG0に接続され、メモリゲート電極はメモリゲート線MG0に接続される。また、ドレイン領域はビット線BL0に接続され、ソース領域はソース線SL0に接続される。さらに、メモリセルM00が形成されたp型ウエル領域にはウエル線WL0が接続される。メモリセルM00に書き込みを行うときは、ウエル線WL0を通じてp型ウエル領域に負電圧を印加しながら、ソースサイド注入方式による書込みを行う。

(もっと読む)

不揮発性半導体記憶装置およびその読み書き制御方法

【課題】 ソース−ドレイン間の電位差を小さくしてメモリセルのゲート長を短くすることができるようにするとともに、メモリセルに対してビットデータの書き込み(プログラム)を行った後、そのベリファイを行う際に比較的大きな電荷の充放電が生じるという問題を解消してデータの読み書きの高速化および低消費電力化を図った不揮発性半導体記憶装置およびその読み書き制御方法を提供する。

【解決手段】 プログラム動作時のt7で、選択メモリセルのセルウェルに4V、ドレインに0V、ゲートに10V、ソースにVCCをそれぞれ印加し、続くベリファイ時のt13において、セルウェルの電圧を4Vにしたまま、選択ワード線WLを−5Vにする。また、このときWLは通常の読み出し時の電圧より絶対値が高い電圧(−5V)に設定しておく。

(もっと読む)

不揮発性フラッシュメモリ

【課題】低消費電力、低減されたリーク問題、および単純なプロセスを伴った新規なフラッシュメモリ、新規なプログラミング方法、およびそのセンシングスキームを提供する。

【解決手段】ワード線218、第1のビット線204、および第2のビット線206を備えた不揮発性メモリセル200を動作させる方法は、メモリセル200をプログラミングする工程を有し、そのプログラミングする工程が、高い正電圧のバイアスを第1のビット線に印加し、接地バイアスを第2のビット線に印加し、高い負電圧のバイアスをワード線に印加することを備え、正帯電ホールが誘電体層212を介してトラッピング層214に突き抜けるようにする。

(もっと読む)

不揮発性半導体記憶装置

【課題】書き込み/消去におけるディスターブを抑制し、かつ面積の増大を抑えた不揮発性半導体記憶装置を提供する。

【解決手段】複数のメモリセルMCを含む第1セルアレイ32が形成された第1導電型の第1のウェル領域と、複数のメモリセルMCを含む第2セルアレイ32が形成された第1導電型の第2のウェル領域と、第1、第2のウェル領域を含む第2導電型の第3のウェル領域とを備える。さらに、第1セルアレイ32が含むメモリセルと第2セルアレイ32が含むメモリセルとに共通に接続されたビット線BLと、ビット線BLに接続されたカラムデコーダ13とを備える。

(もっと読む)

1 - 20 / 175

[ Back to top ]