Fターム[5B125EC08]の内容

リードオンリーメモリ (43,397) | ワード線、ソース線まわり (979) | ソース線まわり (243)

Fターム[5B125EC08]の下位に属するFターム

Fターム[5B125EC08]に分類される特許

1 - 20 / 34

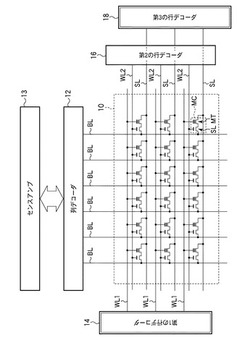

不揮発性半導体記憶装置

【課題】高速で動作し得る不揮発性半導体記憶装置を提供する。

【解決手段】選択トランジスタとメモリセルトランジスタMTとを有するメモリセルMCがマトリクス状に配列されて成るメモリセルアレイ10と、ビット線BLの電位を制御する列デコーダ12と、第1のワード線WL1の電位を制御する電圧印加回路14と、第2のワード線WL2の電位を制御する第1の行デコーダ16と、ソース線SLの電位を制御する第2の行デコーダ18とを有し、列デコーダは電圧印加回路及び第2の行デコーダより耐圧の低い回路により構成されており、第1の行デコーダは電圧印加回路及び第2の行デコーダより耐圧の低い回路により構成されている。ビット線と第2のワード線とが高速で制御され得るため、メモリセルトランジスタに書き込まれた情報を高速で読み出すことができる。

(もっと読む)

半導体メモリ

【課題】 低消費電力、高集積化を図ることができる不揮発性メモリ装置を提供する。

【解決手段】 行列状に配置されたメモリセルを含み、メモリセルのゲートにワード線が接続され、ドレインにローカルビット線LBLdが接続され、ソースに第1または第2のローカルビット線LBLSが接続される。メモリセルMC2の読み出しを行うとき、ビット線選択トランジスタTRd1によって選択されたローカルビット線LBLd1に読出し電圧Vreadを印加し、第1の選択トランジスタTRs0によって選択された第1のローカルビット線LBLs0に0vを印加する。隣接するメモリセルMC3のソースは、第2の選択トランジスタTRs4によって一定電位にクランプされ、隣接するメモリセルMC1のソースは、ビット線選択トランジスタTRd0によって0vに印加される。

(もっと読む)

不揮発性半導体記憶装置

【課題】低消費電流で正確なデータ読出を行なうことが可能な不揮発性半導体記憶装置を提供する。

【解決手段】このフラッシュメモリでは、クロック信号CLKの立ち上がりエッジに応答して外部アドレス信号ADD0〜ADDiに従ってメモリセルMCを選択し、通常の読出モード時は、クロック信号CLKの立ち上がりエッジに応答してメモリセルMCからデータを読み出し、通常の読出モードよりも低消費電力で読出動作を行なう低速読出モード時は、クロック信号CLKの立下りエッジに応答してメモリセルMCからデータを読み出す。したがって、低速読出モードにおいてクロック信号CLKの立ち上がりエッジに応答してノイズが発生してもクロック信号CLKの立下りエッジではノイズレベルが低下しているので、正確にデータ読出を行なうことができる。

(もっと読む)

不揮発性半導体記憶装置

【課題】消去動作を高速に実行可能にした不揮発性半導体記憶装置を提供する。

【解決手段】消去動作を行う場合において、選択ソース線SL0に消去電圧Vera1を印加する一方その他のソース線SL1〜3には接地電圧VSSを印加し、続いてソース側選択ゲート線SGS0に電圧Vera1よりも小さい電圧Vera2を所定時間遅れて印加する。一方、消去対象のメモリトランジスタMTrに接続されるワード線WL1に接地電圧VSSを印加する一方、それ以外のワード線WL0、2、3をフローティング状態とする。

(もっと読む)

不揮発性半導体記憶装置

【課題】チップサイズの増分を抑えて、隣接するグローバルビット線GBL間容量による誤読み出しを防止する。

【解決手段】ビット線を選択する両端の選択ゲートトランジスタの間に直列に接続されてなる各メモリセルトランジスタにしきい値を設定することによりデータを記録する不揮発性のメモリセルアレイと、上記メモリセルトランジスタからビット線並びに、複数のビット線に共通に接続されたグローバルビット線を介してデータの読み出しを制御する制御回路11とを備えた不揮発性半導体記憶装置において、上記グローバルビット線の途中の位置において、グローバルビット線と所定の電源線とを接続する接地トランジスタ23を備え、上記制御回路11は、データの読み出しを行うグローバルビット線に隣接する、データの読み出しを行わないグローバルビット線に接続された上記接地トランジスタ23をオンする。

(もっと読む)

不揮発性半導体記憶装置

【課題】データ読み出し動作を高速化することのできる不揮発性半導体記憶装置を提供する。

【解決手段】不揮発性半導体記憶装置は、メモリセルアレイ11と、センスアンプ12と、センスアンプ12による読み出し動作を制御する制御信号発生回路16と、メモリセルのデータを読み出す間に複数のメモリセルユニットに接続された共通ソース線CELSRCのセルソース電圧Vcsを検出するとともに、検出したセルソース電圧Vcsと基準電圧Vrefとを比較して読み出し制御信号を出力するセルソースモニター回路21とを備える。制御信号発生回路16は、読み出し制御信号に基づいて、第1のデータ読み出しサイクルでデータ読み出し動作を終了するか、又は第2のデータ読み出しサイクルを実行するかを制御する。

(もっと読む)

不揮発性半導体記憶装置

【課題】占有面積の増大を抑制したNAND型フラッシュメモリの不揮発性半導体記憶装置を提供する。

【解決手段】メモリストリングMSは、各々のメモリブロックMB毎に、カラム方向にm列配列されている。ワード線導電層31a〜31dは、n層積層されている。ワード接続層51は、カラム方向に配列され、ワード線導電層31a〜31dのロウ方向の一端近傍へと片側から延びるように形成され、ワード線導電層31a〜31dにコンタクトプラグ511を介して接続され,(数式1)の関係を満たす。m≧n・・・(数式1)

(もっと読む)

半導体記憶装置

【課題】EEPROM等におけるメモリセルのドレイン電圧の立ち上がり時間を十分に確保しつつ、低消費電力で、メモリセルに十分な大きさのドレイン電圧を供給する。

【解決手段】

トランジスタ(40)は、メモリセル(11)のソースをフローティング状態及び接地状態のいずれか一方に設定する。ドレイン電圧発生回路(50)は、第1の電源電圧と当該ドレイン電圧発生回路の出力端との間に接続された第1のスイッチング素子(51)、第1のスイッチング素子(51)に並列に接続され、第1のスイッチング素子(51)よりも電流能力が小さい第2のスイッチング素子(52)、及び第2のスイッチング素子(52)をオンにした後に第1のスイッチング素子(51)をオンにする制御回路(53)を有し、メモリセル(11)のドレインに供給すべき電圧を生成する。

(もっと読む)

三次元積層不揮発性半導体メモリ

【課題】BiCSメモリの周辺回路の面積増大を抑える。

【解決手段】本発明の例に係る三次元積層不揮発性半導体メモリは、第一方向に並んで配置される第一及び第二ブロックBK<i>, BK<i+1>から構成されるメモリセルアレイと、メモリセルアレイの第一方向に直交する第二方向の一端に配置されるドライバ33Lとを備える。第一ブロックBK<i>内の複数の第一セレクトゲート線SGD<0>, …SGD<5>と第二ブロックBK<i+1>内の複数の第一セレクトゲート線SGD<0>, …SGD<5>とは、メモリセルアレイの第二方向の一端において一対一に共通接続されたうえでドライバ33Lに接続される。

(もっと読む)

三次元積層不揮発性半導体メモリ

【課題】BiCSメモリのメモリセルとドライバとを接続する配線の複雑化を抑える。

【解決手段】本発明の例に係る三次元積層不揮発性半導体メモリは、第一方向に並んで配置される第一及び第二ブロックから構成されるメモリセルアレイと、メモリセルアレイの第一方向に直交する第二方向の一端に配置されるドライバ33とを備える。ドライバ33上には、第一及び第二ブロック内の3以上の導電層と同じ構造を持つ3以上の導電層が配置され、第一及び第二ブロック内の第一セレクトゲート線SGD<5>は、ドライバ33上の3以上の導電層を介してドライバ33に接続される。

(もっと読む)

半導体記憶装置

【課題】メモリセルアレイの寄生容量を低減して、回路規模の縮小や特性の向上を実現することが可能な半導体記憶装置を提供する。

【解決手段】半導体記憶装置において、複数のメモリセルを配列して成るメモリセルアレイは、ビットライン方向、またはワードライン方向の少なくとも一方に沿って複数のグループ1a、1bに分割されており、各グループ毎に個別のソースラインSL(a)、SL(b)が共通接続されている。

(もっと読む)

不揮発性記憶装置、不揮発性記憶システムおよび不揮発性記憶装置の制御方法

【課題】消費電流の低減やアクセス時間の短縮化を図ることが可能な不揮発性記憶装置および不揮発性記憶装置の制御方法を提供すること。

【解決手段】不揮発性記憶装置1は、ブースタコントローラ回路10、ブースタ回路20、レベルシフト回路30、Yデコーダ40、本体回路50を備える。ブースタコントローラ回路10に備えられるナンドゲートND1、ノアゲートNR1、ノアゲートNR2からは、キック信号KICK0ないしKICK2が出力される。ブースタ回路20は昇圧系統B0ないしB2を備え、それぞれキック信号KICK0ないしKICK2が入力される。コラムアドレスcoladdの7番地から8番地への遷移に応じて、ナンドゲートND1およびノアゲートNR1から出力されるキック信号KICK0およびKICK1がハイレベルへ遷移するため、昇圧系統B1に加えて、昇圧系統B0が活性化される。

(もっと読む)

半導体記憶装置及びその製造方法

【課題】チップ面積を縮小することができる、メモリ素子を3次元に配置した不揮発性半導体記憶装置を提供すること。

【解決手段】本発明の不揮発性半導体記憶装置は、抵抗変化素子及びダイオードが直列に接続されたメモリ素子を複数有する複数のメモリ素子群と、メモリ素子群の複数のメモリ素子それぞれの一端にそれぞれ接続された複数のソース線と、を有する。複数のメモリ素子群の前記複数のソース線は、それぞれ、2次元的に広がる板状の導電体層である。

(もっと読む)

半導体記憶装置及び電子機器

【課題】メモリセルアレイ中の複数のメモリセルのデータ0とデータ1のセル電流値の分布の隙間が極端に狭かったり、あるいは、それらの分布が重なってしまうようなことがあっても、メモリセルの情報を高精度に判別することができる半導体記憶装置を提供すること。

【解決手段】第1メモリセルMC11と第2メモリセルMC2が隣接し、第1メモリセルMC11の第1入出力端子が接続される第1ビット線BL1と、第2メモリセルMC12の第2入出力端子が接続される第2ビット線BL2とが、それぞれ、センスアンプSA1の各入力に接続されている。上記第1メモリセルMC11の第2入出力端子および上記第2メモリセルMC12の第1入出力端子がコモン線COMに接続されている。

(もっと読む)

不揮発性半導体記憶装置およびその制御方法

【課題】プログラムベリファイ時に多数ビットを同時にベリファイ可能にして書き込み動作の高速化を図る。

【解決手段】メモリセルアレイ11のNウェルに形成したメモリセルTrmのソース線SLを、ブロック内ソース線であるカラムソース線CSLおよびブロックソース線BSLで共通に接続するとともにブロックソースセレクトゲートBSSGを介してブロック外ソース線MSLに接続する。このブロック外ソース線MSLは最上層のメタル層でY軸(ビット線方向)に延びるように配線する。プログラムベリファイ時にカラムラッチの出力でビット線から書き込み完了のメモリセルを介して流れるセル電流をこのブロック外ソース線MSLでバイパスさせる。

(もっと読む)

半導体集積回路装置

【課題】 ページフラグデータを高速に読み出すことができる不揮発性半導体メモリを有した半導体集積回路装置を提供する。

【解決手段】 複数のページ(PAGE)は各々、ユーザによるデータの書き換えが可能なユーザ領域7と、当該ページの現状態を示すページフラグデータが書き込まれるページフラグ9領域とを含み、ページバッファ3は、ユーザデータを一時的に保持するユーザ用ページバッファ部11と、ページフラグデータを一時的に保持するページフラグ用ページバッファ部13とを含み、ページフラグデータはページフラグ領域9に配置された不揮発性半導体メモリセルに二値で記録し、ユーザデータはユーザ領域7に配置された不揮発性半導体メモリセルに多値で記録する。

(もっと読む)

共通ビットラインを有するNAND構造の不揮発性メモリ素子

【課題】共通ビットラインを有するNAND構造の不揮発性メモリ素子を提供する。

【解決手段】両端が共通ビットライン及び共通ソースラインに連結された第1ストリング及び第2ストリングを備えるNAND構造の不揮発性メモリ素子である。第1ストリング及び第2ストリングは、互いに直列に連結されたストリング選択トランジスタ、複数の単位素子及びソース選択トランジスタをそれぞれ備える。複数のワードラインは、同じ行に配置された複数の単位素子の制御ゲートにそれぞれ連結される。第1ストリング選択ライン及び第2ストリング選択ラインは、第1ストリング及び第2ストリングのストリング選択トランジスタのゲートにそれぞれ連結される。第1ソース選択ライン及び第2ソース選択ラインは、第2ストリング及び第1ストリングのソース選択トランジスタのゲートにそれぞれ連結される。

(もっと読む)

半導体記憶装置

【課題】 規模の大きいメモリコアにおいてもビット線に接続されるメモリセルのオフリーク電流を低減し、1本のワード線あたりに接続されるメモリセル数を増やしてメモリコア全体での面積削減によるチップコストの削減を実現し、またメモリセルアレイ部のマスク作成時のパターニングを容易にする。

【解決手段】 ソース電位配線13からソース制御電位をソースノードに供給するソース電位接続トランジスタ12をメモリセルアレイ1内に分散配置し、ソース電位制御回路5はロウデコーダブロック2内に配置する。これにより、1本のワード線7に接続されるセル数を増やすことが可能となり、メモリコアの面積削減を実現できる。また、ソース電位接続トランジスタを構成する拡散層の形状をメモリセルトランジスタの拡散層の形状と同一パターンにすることで、マスク作成の容易化を実現できる。

(もっと読む)

不揮発性半導体記憶装置

【課題】 非選択セルのドレインに高電圧が印加される時間を短縮して非選択セルが受けるストレスを軽減させることにより、メモリセルに蓄積された電荷の減少を抑えることが可能な不揮発性半導体記憶装置を提供する。

【解決手段】 センスラッチ単位回路7AはメモリセルMC0Aへのデータの書込が終了すると、グローバルビット線GBL0への4.5Vの電圧の印加を終了して0Vの電圧を印加し、グローバルビット線GBL1に2Vの電圧(書込阻止電圧)を印加する。メモリセルMC0Aへのデータ書込期間にはローカルビット線LBL0にドレインが接続されるメモリセルMC0A以外のメモリセル(書込非選択セル)のドレインにも4.5Vの電圧が印加される。メモリセルMC0Aにデータ書込が行なわれていない期間にはローカルビット線LBL0の電圧は0Vになる。

(もっと読む)

半導体集積回路装置

【課題】 実用に適した回路構成を持つ、倍ピッチセルを備えた不揮発性半導体記憶装置を有する半導体集積回路装置を提供する。

【解決手段】 第1メモリセルユニット(MU1)の電流通路の一端、及び第2メモリセルユニット(MU2)の電流通路の一端に共通接続された第1ビット線(BL1)と、第3メモリセルユニット(MU3)の電流通路の一端に接続された第2ビット線(BL2)と、第1メモリセルユニット(MU1)の電流通路の他端に接続された第1ソース線(SL1)と、第2メモリセルユニット(MU2)の電流通路の他端、及び第3メモリセルユニット(MU3)の電流通路の他端に共通接続された第2ソース線(SL2)とを具備する。

(もっと読む)

1 - 20 / 34

[ Back to top ]