Fターム[5B125EC09]の内容

リードオンリーメモリ (43,397) | ワード線、ソース線まわり (979) | ソース線まわり (243) | ソース線の電圧制御 (180)

Fターム[5B125EC09]に分類される特許

1 - 20 / 180

不揮発性半導体メモリ素子、および不揮発性半導体メモリ装置

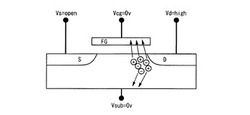

【課題】フローティングゲートへの電荷の蓄積と消去を容易に行え、またフローティングゲートの電荷を消去する場合にメモリセルの閾値を容易に制御できる、不揮発性半導体メモリ素子を提供する。

【解決手段】フローティングゲートへの電荷の蓄積時に、フローティングゲートとドレイン(またはソース)間に電圧を印加し、バンド・バンド間によるホットエレクトロンを半導体基板中に発生させ、フローティングゲートに電荷を注入する。また、フローティングゲートの電荷の消去時には、フローティングゲートとドレイン(またはソース)間に電圧を印加し、バンド・バンド間によるホットホールを発生させ、該ホットホールにより蓄積された電荷を消去する。また、フローティングゲートの電荷の消去時には、メモリセルのコントロールゲートとソース間の閾値が所望の値になるように制御しながら、電荷を消去する。

(もっと読む)

不揮発性半導体記憶装置

【課題】不揮発性半導体記憶装置においてリーク電流を抑制し読み出し動作を正確に実行する。

【解決手段】この不揮発性半導体記憶装置は、1導電型の半導体層と、第1方向に並ぶように前記第1半導体層上に形成される複数の第2導電型のウエルを有する。この複数のウエルの各々に、メモリブロックが配列される。複数のメモリブロックは、それぞれ複数のメモリセル及び選択トランジスタを直列接続してなる複数のNANDセルユニットを配列してなる。複数のワード線が、1つのメモリブロック中の複数のNANDセルユニットに共通に接続される。複数のビット線は、第1方向に延びて複数のメモリブロックに存在するNANDセルユニットの一端に接続される。ソース線は、NANDセルユニットの他端に接続される。ウエルドライバは、第1電圧、又は第1電圧よりも大きい第2電圧を選択的に複数の前記ウエルの各々に与える制御を行う。

(もっと読む)

半導体記憶装置

【課題】動作信頼性を向上出来る半導体記憶装置を提供すること。

【解決手段】実施形態の半導体記憶装置1は、メモリセルアレイ10と、ビット線BLと、ソース線SLと、センス回路13とを備える。メモリセルアレイ10は、半導体基板40上に積層されたメモリセルMTが直列接続されたメモリストリング16を有する。ビット線BLは、いずれかのメモリストリング16に接続され、データを転送可能である。ソース線SLは、いずれかのメモリストリング16に接続され、データの読み出し時において、ビット線BLから読み出し電流が流れ込む。センス回路13は、ビット線BLに接続され、読み出しデータをセンスする。センス回路13の動作タイミングは、ソース線SLに流れる電流に基づいて決定される。

(もっと読む)

不揮発性半導体記憶装置

【課題】選択メモリセルトランジスタに電荷を蓄積する際の電圧を従来よりも自由に設定し得る不揮発性半導体記憶装置を提案する。

【解決手段】不揮発性半導体記憶装置1では、選択メモリセルトランジスタ115に電荷を蓄積させる際、電圧の高い書き込み禁止電圧をP型MOSトランジスタ9bから印加し、電圧の低い書き込み電圧をN型MOSトランジスタ15aから印加して、選択メモリセルトランジスタ115又は非選択メモリセルトランジスタ116へ電圧を印加する役割分担を、P型MOSトランジスタ9b及びN型MOSトランジスタ15aに分けたことで、P型MOSトランジスタ9b及びN型MOSトランジスタ15aそれぞれのゲート電圧やソース電圧を個別に調整でき、最終的にゲート基板間電圧を例えば4[V]等に設定し得る。

(もっと読む)

不揮発性半導体記憶装置

【課題】高集積化を図ることができる不揮発性半導体記憶装置を提供する。

【解決手段】実施形態に係る不揮発性半導体記憶装置は、セルの書き込みにおいて、制御装置は複数の第2の選択ゲートトランジスタに第1電位を与えた後、第1電位よりも低い第2電位を与える。複数のビット線のうち、書き込み不十分のセルに第3電位を与え、書き込み終了に間近のセルに第3電位より高い第4電位を与え、書き込みが終わったセルに第4電位より高い第5電位を与える。制御装置は、第2電位を与えた後、複数のワード線のうち選択されたワード線に書き込み電位を与え、第1電位は、第2の選択ゲートトランジスタをオンすることにより第3電位をNANDストリングに転送する電位であり、第2電位は、第3電位をNANDストリングに転送した後、前記第2の選択ゲートトランジスタをオフする電位である。

(もっと読む)

不揮発性半導体記憶装置

【課題】消去動作の実行単位を小さくすると共に正確な読出動作を実現可能な不揮発性半導体記憶装置を提供する。

【解決手段】一態様に係る不揮発性半導体記憶装置は、複数のメモリストリング、複数のメモリブロック、複数のソース線、及び制御回路を有する。複数のメモリストリングは、積層された複数のメモリトランジスタを含む。複数のメモリブロックは、複数のメモリストリングを含む。複数のソース線は、複数のメモリストリングそれぞれに接続される。制御回路は、複数のソース線に供給する信号を制御する。複数のメモリストリングは、各々、半導体層、電荷蓄積層、及び導電層を有する。制御回路は、メモリトランジスタに対する動作の種類に基づいて、複数のソース線を電気的に共通接続するか否かを切り替える。

(もっと読む)

半導体記憶装置

【課題】メモリセルトランジスタからのデータの読み出しを高速化する。

【解決手段】メモリセルアレイ121は、メモリセルトランジスタ131及びローカルビット線LBLを含む第1回路部と、ローカルビット線LBLをグローバルビット線GBLに接続してメモリセルトランジスタ131に対する書き込み及び読み出しを行う第2回路部を含む。この第2回路部の、グローバルビット線GBLの電圧が印加されるnMOSトランジスタ151,152,154等に、耐圧を電源電圧としたものを用い、読み出しの高速化を図る。書き込みは、グローバルビット線GBLに電源電圧以下の電圧を印加し、ソース線SLに電源電圧よりも高い電圧を印加することで行う。

(もっと読む)

不揮発性半導体記憶装置

【課題】読み出し動作を正確に実行する。

【解決手段】 制御回路は、メモリトランジスタの読み出し動作を実行する際、選択メモリトランジスタに接続される選択ワード線には、第1の電圧を印加する。選択メモリトランジスタを除く非選択メモリトランジスタに接続される非選択ワード線には、メモリトランジスタの保持データに拘わらずメモリトランジスタを導通させる第2の電圧を印加する。ビット線には、第3の電圧を印加する。ソース線のうち、選択メモリブロック中の前記選択メモリトランジスタが含まれるメモリストリングに接続される選択ソース線には第3の電圧より小さい第4の電圧を印加する。ソース線のうち、選択メモリブロック中の非選択のメモリストリングが接続される非選択ソース線には第3の電圧と略同一の第5の電圧を印加する。

(もっと読む)

不揮発性半導体記憶装置

【課題】チップ面積を削減することのできる不揮発性半導体記憶装置を提供する。

【解決手段】一の実施形態に係る不揮発性半導体記憶装置は、半導体基板と、半導体基板上に積層され、垂直方向に直列接続された複数のメモリセルを含むメモリセルアレイと、半導体基板上に設けられ、所望の電圧をメモリセルアレイに供給する電源回路とを備える。電源回路は、電圧を生成するポンプ回路と、ポンプ回路の出力端子に接続され、出力端子の電圧値が所定の値を下回った場合にポンプ回路へ制御信号を出力するリミッタ回路と、出力端子に一端が接続され、出力端子の電圧を調整するように構成されたキャパシタと、キャパシタの他端に接続され、制御信号に基づき所定の電流値の定電流を用いてキャパシタを充電するブースト回路と、ブースト回路の充電動作を停止させるスイッチとを備える。キャパシタは、メモリセルアレイの直下に設けられる。

(もっと読む)

不揮発性半導体メモリ

【課題】消費電力および消費電流を低減することが可能な不揮発性半導体メモリを提供する。

【解決手段】複数のメモリセルを含むメモリセルアレイと、入出力パッドと、メモリセルから読み出したデータを、入出力パッドを介して外部に出力し、且つ、外部から書き込みデータおよびコマンドを、入出力パッドを介して入力するためのI/O回路と、メモリセルの、書き込み、読み出し、又は消去動作に必要な第1の電源電圧が印加される第1の電源電圧パッドと、第1の電源電圧よりも低く且つI/O回路に供給するための第2の電源電圧が印加される第2の電源電圧パッドと、第1の電源電圧を降圧し、第2の電源電圧よりも高い第1の降圧電圧を出力する第1の降圧回路と、第2の電源電圧を降圧し、第1の降圧電圧よりも低い第2の降圧電圧を出力する第2の降圧回路と、第1の降圧電圧が供給される第1の内部回路と、第2の降圧電圧が供給される第2の内部回路を備える。

(もっと読む)

不揮発性半導体記憶装置

【課題】消去動作及びソフトプログラム動作の際のメモリセルの劣化の影響を抑制することのできる不揮発性半導体記憶装置を提供する。

【解決手段】一の実施の形態に係る不揮発性半導体記憶装置は、制御部を備える。制御部は、データ消去のため所定範囲のメモリセルに対し消去電圧を印加する消去動作、データ消去が完了したか否かを確認する消去ベリファイ動作、及びデータ消去が完了しなかった場合に消去電圧を所定のステップアップ値だけ上昇させるステップアップ動作を繰り返す制御を司る。制御部は、一連の消去動作時に消去電圧を印加した回数が第1の回数より大きく、第2の回数(第1の回数<第2の回数)未満の場合、所定範囲のメモリセルを過消去状態から第1の閾値電圧分布状態に設定するソフトプログラム動作を実行し、消去電圧を印加した回数が第1の回数以下、又は第2の回数以上の場合、ソフトプログラム動作を実行しないように構成されている。

(もっと読む)

プログラム電流クランプを有する不揮発性メモリ素子及び関連する方法

【課題】 本発明は、プログラム電流クランプを有する不揮発性メモリ素子及び関連する方法を提供する。

【解決手段】 選択トランジスタとメモリ・トランジスタとを有する不揮発性メモリ・セルをプログラミングする方法が提供される。当該方法は:前記メモリ・セルの第1の入力に予め設定された制限電流を印加する段階;前記メモリ・セルの第2の入力に電気的に接続された電流制限回路に制限電圧を印加する段階;前記メモリ・セルの電圧降下を安定化させるために制限電圧を印加する段階;前記電流制限回路により決定された予め設定された制限された電流で前記メモリ・セルをプログラミングするために、前記メモリ・セルに傾斜したゲート電圧を印加する段階;を有する。

(もっと読む)

不揮発性半導体記憶装置

【課題】メモリセルごとの消去回数を低減することで、フラッシュメモリの寿命を延ばす。

【解決手段】不揮発性半導体記憶装置3は、複数の半導体領域202の各々に設けられ、かつ直列に接続されたメモリトランジスタ及び選択トランジスタを有する複数の不揮発性メモリセルがマトリクス状に配置されたメモリセルブロックと、同一行にあるメモリトランジスタを共通接続するようにして、複数のメモリトランジスタのコントロールゲートに接続された複数のワード線WLと、同一行にある選択トランジスタを共通接続するようにして、複数の選択トランジスタのゲートに接続された複数の選択ゲート線SGとを含む。ロウデコーダ20は、消去動作時に、半導体領域に消去電圧を印加した状態で、データが消去される選択ワード線に負の第1の電圧を印加し、データが消去されない非選択ワード線に正の第2の電圧を印加する。

(もっと読む)

半導体メモリおよびシステム

【課題】 プリチャージ動作を不要にすることで、読み出しアクセス時間を短縮する。

【解決手段】 メモリセルは、第1電圧線と第2電圧線の間に接続ノードを介して直列に接続され、相補の論理を記憶する一対のセルトランジスタを有する。第1制御回路は、読み出し動作時に、一対のセルトランジスタのコントロールゲートを活性化レベルに設定する。第2制御回路は、読み出し動作時に、第1電圧線を第1電圧に設定し、第2電圧線を第1電圧より高い第2電圧に設定する。読み出し回路は、読み出し動作時に、接続ノードに生成される電圧に応じて、メモリセルに保持されている論理を判定する。これにより、読み出し動作において、メモリセルに保持されている論理に応じて、接続ノードを第1電圧または第2電圧に設定できる。

(もっと読む)

ワードライン昇圧回路、記憶装置、集積回路装置、及び電子機器

【課題】極低電圧でもワードラインを十分に昇圧することができるワードライン昇圧回路、記憶装置、集積回路装置、及び電子機器等を提供する。

【解決手段】メモリーセルMCを選択するためのサブワードラインSWLに供給される昇圧電圧を生成するワードライン昇圧回路140は、サブワードラインSWLに昇圧電圧を供給するp型の第1の駆動トランジスターTr10と、第1の駆動トランジスターTr10のソース電圧を第1の電源電圧VWLに基づいて生成するp型の第1の電圧供給トランジスターTr11と、第1の駆動トランジスターTr10のソースと第1の電圧供給トランジスターTr11のドレインを接続する第1の電源ラインSPL1と、第1の基準電圧と第1の電源ラインSPL1との間に挿入された第1の昇圧キャパシターBC1とを含む。

(もっと読む)

不揮発性メモリのビットセルのI−V曲線を取得するためのデジタル方法および装置

【課題】不揮発性メモリビットセルに対する電流−電圧特性情報を生成するための方法および装置を提供する。

【解決手段】基準電流生成回路は、選択されたデジタルレジスタ設定に対応する選択された基準電流を生成する。センスアンプ回路は、遷移ゲート電圧が識別されるまで不揮発性メモリビットセルに掃引ゲート電圧が印加されるとき、前記基準電流を前記不揮発性メモリビットセルによって生成されるドレイン電流と比較する。前記遷移ゲート電圧および前記基準電流を前記不揮発性メモリビットセルに対する電流−電圧特性情報としてメモリに格納する。

(もっと読む)

不揮発性半導体記憶装置

【課題】不揮発性半導体記憶装置の消去時のストレスの増大を抑制しつつ、消去不良を低減する。

【解決手段】消去ベリファイ回数カウント部7cは、消去動作が実行されたメモリセルの消去ベリファイ回数をカウントし、消去ベリファイ回数設定部7dは、消去ベリファイ回数カウント部にてカウントされた今回の消去ベリファイ回数に基づいて、次回以降の最小の消去ベリファイ回数を設定する。

(もっと読む)

不揮発性メモリにおける消去ランプパルス幅制御

【課題】消去閾値電圧分布圧縮時間を減少し、総合消去処理時間を改善するためのシステムおよび方法を提供する。

【解決手段】不揮発性メモリのメモリブロックを消去する方法が、消去パルスのパルス幅(PW)を初期幅に設定するステップ、メモリブロックが消去メトリックを満たすまで、または最大数の消去パルスが印加されるまで、メモリブロックに消去パルスを繰り返し印加するステップ(517)、消去パルスのパルス電圧の大きさを初期パルス電圧レベルから最大パルス電圧レベル(PMAX)に徐々に調整するステップ(519)、パルス電圧の大きさが初期パルス電圧レベルと最大パルス電圧レベルとの間の中間電圧レベルに達したとき、消去パルスの幅を初期幅より狭くなるように減少するステップ(525)を含む。狭いパルスはより高い電圧レベルで印加されて、メモリブロックの過剰消去の量が減少される。

(もっと読む)

半導体記憶システム

【課題】 複数のチップを実装した場合において、複数のチップ間で通信する通信線を設けることなく、ピーク電流を抑制可能な半導体記憶システムを提供する。

【解決手段】 半導体記憶システムによれば、電源配線81は、第1の半導体記憶装置71aと第2の半導体記憶装置71bに共通接続され、第1、第2の半導体記憶装置に電源を供給する。電圧検知回路74a,74b,74cは、第1、第2の半導体記憶装置のそれぞれに設けられ、電源配線の電源電圧を検知する。制御回路7は、第1、第2の半導体記憶装置のそれぞれに設けられ、電圧検知回路により電源電圧の低下が検知された場合、電源電圧が復帰するまで、第1、又は第2の半導体記憶装置の動作を、次の動作に遷移させない。

(もっと読む)

半導体メモリ装置及びその動作方法

【課題】 最上の動作条件を設定し、それによって半導体メモリ装置を動作させることで半導体メモリ装置の動作特性を向上させることができる不揮発性メモリ装置及びその動作方法を提供する。

【解決手段】 ビットラインBLとソースラインSLとの間に連結されるチャンネル層SCを有するメモリストリングMSを含むメモリブロックと、チャンネル層SCにホットホールhを供給し、メモリストリングMSに含まれたメモリセルCの消去動作を行うように構成された動作回路グループと、チャンネル層SCにホットホールhが目標量以上に供給されれば、ブロック消去イネーブル信号BERASE_ENを出力するように構成された消去動作決定回路460と、ブロック消去イネーブル信号BERASE_ENに応答して動作回路グループが消去動作を行う時点を制御するように構成された制御回路450と、を含む。

(もっと読む)

1 - 20 / 180

[ Back to top ]