Fターム[5B125EF02]の内容

リードオンリーメモリ (43,397) | その他の周辺回路 (1,179) | 入力データのバッファ、保持 (224)

Fターム[5B125EF02]に分類される特許

1 - 20 / 224

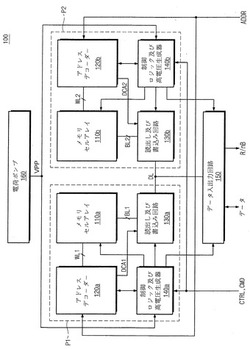

不揮発性メモリ装置及び不揮発性メモリ装置を制御するコントローラの動作方法

【課題】向上された動作速度を有する不揮発性メモリ装置及び不揮発性メモリ装置を制御するコントローラの動作方法を提供する。

【解決手段】本発明の不揮発性メモリ装置は、データのプログラム、読出し又は消去を遂行する第1プレーン、データのプログラム、読出し又は消去を遂行する第2プレーン、及び第1プレーン又は第2プレーンから共通バスを通じて伝送されるデータを外部へ出力し、外部から受信されるデータを、共通バスを通じて第1プレーン又は第2プレーンへ伝送するデータ入出力回路を含む。第1プレーンでプログラム、読出し又は消去が遂行される時、データ入出力回路は共通バスを通じて第2プレーンとデータを交換する。

(もっと読む)

メモリシステム及びそれの動作方法

【課題】動作速度及び電力消耗を減らすことができるメモリシステム及びそれの動作方法が提供される。

【解決手段】本発明の実施形態によるメモリシステムは不揮発性メモリ装置と、前記不揮発性メモリ装置を制御するように構成されたメモリ制御器と、を含み、前記メモリ制御器は前記不揮発性メモリ装置から読み出されたデータのエラーの位置情報を含むエラーフラッグ情報を前記不揮発性メモリ装置へ提供する。

(もっと読む)

半導体記憶装置及びその制御方法

【課題】カラムブロックのデータラッチに対するデータの高速転送を可能にする。

【解決手段】半導体記憶装置1は、メモリセルアレイ2と、データバスDBと、転送制御部TC0〜TC2と、複数のカラムブロックC(0+4×i)〜C(3+4×i)と、カラムセレクタCSとを含む。カラムブロックおよびカラムセレクタはメモリセルアレイより下に形成される。データバスDBは複数のステージS0〜S3に分割される。転送制御部は複数のステージのそれぞれにデータが割り当てられるようにデータをシリアル転送する。カラムブロックは選択された場合にデータを一次記憶する。カラムセレクタCSはカラムブロックの中から、ステージごとにいずれかのカラムブロックを選択し、ステージごとに選択されたカラムブロックとの間でデータをパラレル転送する。データバスDBはカラムブロックの配列方向の一方の端側から他方の端側へ向かい、他方の端側で折り返す。

(もっと読む)

記憶装置及び印刷装置

【課題】効率的なメモリーアクセスができる記憶装置及び印刷装置等を提供すること。

【解決手段】記憶装置100は、バスBSを介して接続されるホスト装置400との通信処理を行う制御部110と、ホスト装置400からのデータがシーケンシャルに書き込まれる記憶部120と、記憶部120のアクセス制御を行う記憶制御部130と、クロック信号が入力されるクロック端子TCKと、データ信号が入力されるデータ端子TDAと、リセット信号が入力されるリセット端子TRSTとを含む。制御部110は、クロック信号及びリセット信号の電圧レベルに基づいて、記憶部120に対するアクセスを制御するモードであるアクセス制御モードが通常モードであるか、或いはスキップモードであるかを判断する。記憶制御部130は、アクセス制御モードがスキップモードである場合には、スキップアドレスを開始アドレスとして記憶部120のアクセス制御を行う。

(もっと読む)

半導体記憶装置

【課題】ライトパラメータを効率よく探索することができる半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、パラメータセットを初期値から変更して生成した新たな2以上のパラメータセットを用いて半導体メモリセルに情報を書き込み、その半導体メモリセルについて変換回路の出力を取得し、変換回路の出力の最大値が得られたパラメータセットと、最小値が得られたパラメータセットとをパラメータ空間上で結ぶ延長上に位置する、他のパラメータセットを、新たな初期値として設定して検証を再実施し、書き込んだ情報と読み出した情報が一致する半導体メモリセルについては、初期値を用いた検証を終了する。

(もっと読む)

不揮発性メモリ装置

【課題】信頼性を向上させることができる不揮発性メモリ装置の提供。

【解決手段】メモリセルアレイの選択されたページからデータを読み出すか、或いはメモリセルアレイの選択されたページへ書き込むように構成されたページバッファ回路と、選択されたページに割り当てられたシードに基づいて、ページバッファ回路へ伝送されるか、或いはページバッファ回路から伝送されるデータをランダム化及びデランダム化するように構成されたランダム化及びデランダム化回路と、を有し、選択されたページは複数のセグメントで構成され、ランダム化及びデランダム化回路は、選択されたページに割り当てられたシードに基づいて選択されたページのアクセス要請されたセグメントの各々に対するランダムシークェンスを生成するように構成され、シードにしたがって反復的に生成されたランダムシークェンスに基づいて各アクセス要請されたセグメントのデータをランダム化及びデランダム化するように構成される。

(もっと読む)

入力回路

【課題】入力信号を的確なタイミングで取り込むことを可能にする。

【解決手段】第1入力回路10は、入力信号IOを検知して入力信号と同相の第1出力信号Dinを出力する。第2入力回路20は、第1ストローブ信号DQSを検知しての第2出力信号/DQSiを出力する。第3入力回路30は、第1ストローブ信号を反転した第2ストローブ信号BDQSを検知して第3出力信号/BDQSiを出力する。データラッチ回路70は、第1ラッチ回路L1及び第2ラッチ回路L2を含み、第1出力信号、第2出力信号及び第3出力信号に基づき、第1ラッチ回路又は第2ラッチ回路のいずれか一方に第1出力信号をラッチさせ、他方への第1出力信号の入力を許容する。

(もっと読む)

不揮発性半導体メモリ

【課題】プログラム後の読み出し不良をプログラム動作の終了前に判定する。

【解決手段】実施形態に係わる不揮発性半導体メモリは、選択ワード線に対する書き込みパルスの印加とベリファイ読み出し動作とを繰り返す第1の手段(ステップST1〜ST5)と、ベリファイ回路によりプログラムデータの記録が完了と判断された後に選択メモリセルに対して読み出し動作を行う第2の手段(ステップST6)と、この読み出し動作により読み出されたデータとプログラムデータとが一致するときに外部コントローラにプログラム動作がパスしたことを示すステータス情報を出力し、両者が一致しないときに外部コントローラにプログラム動作がフェイルしたことを示すステータス情報を出力する第3の手段(ステップST7)とを備える。

(もっと読む)

半導体メモリおよびシステム

【課題】 1つをメモリブロックの書き込み動作中に、別のメモリブロックの読み出し動作を実行することで、アクセス効率を向上する。

【解決手段】 半導体メモリは、複数ビットの書き込みデータおよび書き込みデータのパリティデータをビット毎に保持する複数のメモリ領域を有する複数のメモリブロックを有している。書き込みコマンドに応答して、メモリブロックの1つである書き込みメモリブロックのメモリ領域に、書き込みデータおよびパリティデータが順に書き込まれる。読み出しコマンドに応答して、書き込みメモリブロックを除くメモリブロックの1つにおいて、書き込みデータおよびパリティデータが供給されていないデータ線に対応するメモリ領域からデータが読み出され、書き込み動作により読み出させないデータが再生される。これにより、書き込み動作と並行して読み出し動作を実行できる。

(もっと読む)

複数の独立したシリアルリンクメモリ

【課題】半導体メモリにおけるシリアルデータリンクインターフェイスとメモリバンクとの間のデータ転送を制御する装置、システム、および方法が開示される。

【解決手段】一例では、リンクがバンクと独立している、複数のシリアルデータリンクおよび複数のメモリバンクを備えるフラッシュメモリ装置が開示される。エコー信号ラインを使用して、フラッシュメモリ装置をデイジーチェーン構成においてカスケードし、メモリ装置間で連続的に通信してもよい。さらに、単一リンクを使用して複数のリンクをエミュレートする仮想複数リンク構成が記載されている。

(もっと読む)

不揮発性メモリ用の高速ファンアウトシステムアーキテクチャおよび入出力回路

【課題】 不揮発性メモリ用の高速ファンアウトシステムアーキテクチャおよび入出力回路を提供する。

【解決手段】 さまざまな実施形態において、複数の不揮発性メモリデバイス、例えばNANDフラッシュメモリデバイスが、ファンアウト構造でホストコントローラデバイスに接続され得る。ファンアウト構造によると、各メモリデバイスは読み出し動作および/または書き込み動作を同時に実行できる。各不揮発性メモリデバイスは、高速入力回路および高速出力回路を有し得るので、メモリとの間のデータ転送は、フラッシュメモリ読み書きインターフェースの速度に制限されない。

(もっと読む)

半導体記憶装置

【課題】 各種のデータ転送が可能な半導体記憶装置を提供する。

【解決手段】 メモリセルアレイ10は、複数の不揮発性メモリセルが配置されている。RAM(Random Access Memory)30は、メモリセルアレイ10に書き込まれるデータ、又は読み出されたデータを保持する。制御部4は、RAMを用いた第1の動作モードと、RAMを用いない第2の動作モードを制御する。データ転送部17は、第2の動作モードにおいて、データの書き込み時、データバスDIRを介して入出力部40から供給されたデータをバッファ部12に転送し、バッファ部12に転送されたデータをエラー訂正部20に転送し、エラー訂正部20において、生成されたパリティデータをバッファ部12に転送する。

(もっと読む)

不揮発性半導体記憶装置、及び読み出し電圧検出方法

【課題】読み出し動作の信頼性が高い不揮発性半導体記憶装置、及び読み出し電圧検出方法を提供する。

【解決手段】不揮発性半導体記憶装置100は、自装置の外部から第1データを取得するデータ入力バッファ102と、印加された電圧の電圧値に応じて第2データを出力する複数のメモリセルを有するNANDメモリセルアレイ108と、選択されたページに属するメモリセルに電圧値が順次変化する電圧を印加するワード線電圧制御回路107と、メモリセルから取得した第2データのエラーを検出するエラー検出回路104と、メモリセルから第2データを出力させるための読み出し電圧の最適値をエラーが検出された際にメモリセルに印加されていた電圧の電圧値に基づいて検出するワード線電圧補正回路106と、最適値を表すコードを自装置の外部に出力するデータ出力バッファ111とを備える。

(もっと読む)

不揮発性半導体記憶装置及び方法

【課題】データのばらつきを有効に大きくすることができると共に、無駄なデータランダマイズ処理を防止することができる不揮発性半導体記憶装置を提供すること。

【解決手段】メモリセルアレイに書き込むべきデータのばらつきの度合いを表す指標を演算し、前記指標が所定値以上であるかどうかを判定する判定回路と、前記判定回路による判定の結果、前記指標が前記所定値以上である場合、前記データを前記メモリセルアレイにそのまま出力し、前記指標が前記所定値を下回る場合、前記データをランダマイズして前記メモリセルアレイに出力するランダマイズ回路とを備える。

(もっと読む)

半導体記憶装置、及び記憶方法

【課題】書き込みデータにおける値の偏りを平準化する際に要する時間を短縮する。

【解決手段】半導体記憶装置は、第1の値と、第2の値とのいずれかを示すデータを記憶するメモリセルを複数有するメモリアレイと、メモリアレイに記憶させたデータにおいて、第1の値の数と、第2の値の数とのいずれが多いかを判定する転送済データ判定部と、外部から入力されるデータのデータ量がメモリアレイへの書き込み単位に達するごとに、メモリアレイに書き込むデータにおいて、第1の値と、第2の値とのいずれの値が多く含まれているかを判定する書込データ判定部と、転送データ判定部の判定結果及び書込データ判定部の判定結果に応じて、各ビットの値を反転させた書き込みデータと、書き込みデータとのいずれかを選択してメモリアレイに記憶させる書込データ選択部を備えている。

(もっと読む)

半導体記憶装置

【課題】セットアップ及びホールド時間のマージンを確保する。

【解決手段】半導体記憶装置1は、第1のクロックを受け、かつデータの入出力を行う第1のバッファ12を有する第1のメモリ10と、データの入出力を行う第2のバッファ22を有する第2のメモリ20とを含む。第1のメモリ10は、第1のクロックを用いて第2のメモリ20に第2のクロックを転送する。第1のバッファ12は、第1のクロックに応答して第2のメモリ20にデータを転送する。第2のバッファ22は、第2のクロックに応答してデータを受ける。

(もっと読む)

メモリシステム

【課題】SLCフラッシュメモリとMLCフラッシュメモリとのそれぞれのメリットを状況に応じて得る。

【解決手段】実施の形態によるメモリシステム1は、MLCフラッシュメモリ112と、ブロック管理部102と、転記部(107、108および109)と、を備える。MLCフラッシュメモリ112は、SLCモードおよびMLCモードのいずれでもデータの書込みが可能な複数のブロックを含む。ブロック管理部102は、有効データを格納しないブロックをフリーブロックとして管理する。転記部は、ブロック管理部102が管理するフリーブロックの数が所定の閾値Tbf以下である場合、有効データを格納する1つ以上の使用ブロックを転記元ブロックとして選択し、転記元ブロックに格納されている有効データをフリーブロックにMLCモードで転記する。

(もっと読む)

インターフェース回路及びインターフェース回路を備えるメモリコントローラ

【課題】ロックアップ時間無しでDDRインターフェースを備えたメモリにアクセスすることのできるインターフェース回路及びインターフェース回路を備えるメモリコントローラを提供する

【解決手段】データストローブ信号(DQS)の周期が基本クロックの周期の4n倍(nは1以上の整数)になるようにする。このようにすることにより、データストローブ信号(DQS)がハイレベルの期間又はローレベルの期間は、基本クロックの2n周期分の期間と一致する。そして、データストローブ信号(DQS)の立ち上がりエッジ又は立ち下がりエッジから基本クロックのn周期分に対応する時間が経過した時点を中心として、半周期分未満の時間差で読み出しデータ(DQ)の信号がラッチする。

(もっと読む)

不揮発性メモリ装置の動作方法

【課題】選択ワードラインへの供給動作電圧が、正か負かにより、ワードラインに接続された不揮発性メモリセルが、プログラミングされたか、消去されたかを判断する時間を調節する方法を提供する。

【解決手段】正スレショルド電圧を有し選択ワードラインとビットライン間に接続された不揮発性メモリセルにリード命令動作時、ワードラインに正リード電圧を供給し、ビットラインに接続されたページバッファに第1制御信号を供給する段階と、負スレショルド電圧を有するメモリセルにリード命令動作時、ワードラインに負リード電圧を供給し、ページバッファに第1、第2制御信号を供給する段階とを有し、第1制御信号は、第1ディスチャージ区間、第1プリチャージ区間、第1ディベロップ区間、及び第1感知区間を含む第1リード動作区間を定義し、第2制御信号は、第1リード動作区間より長い第2リード動作区間を定義する。

(もっと読む)

不揮発性半導体記憶装置

【課題】 特定の処理に続けて読み出されるデータを任意に指定することを可能とする不揮発性半導体記憶装置を提供する。

【解決手段】 不揮発性半導体記憶装置は、第1メモリ領域及び第2メモリ領域を少なくとも含むメモリ領域を有する。不揮発性半導体記憶装置は、前記第1メモリ領域に対する処理の実行を指示する特定コマンドに応じて、前記第1メモリ領域に対する処理が行われる場合に、前記第1メモリ領域に対する処理に続けて、前記第2メモリ領域に格納されたデータを読み出すように構成された制御部を備える。前記特定コマンドは、前記第1メモリ領域に対する処理に続けて、前記第2メモリ領域に格納されたデータを読み出すべきことを識別する識別情報を含む。

(もっと読む)

1 - 20 / 224

[ Back to top ]