Fターム[5C094DA09]の内容

要素組合せによる可変情報用表示装置 (81,180) | パネルの全体的構造 (7,880) | パネル上に駆動回路を有するもの (376)

Fターム[5C094DA09]に分類される特許

361 - 376 / 376

電気光学装置、その製造方法および電子機器

【課題】 良好な素子特性を維持しながら、補助容量線の抵抗に起因した表示品位の低下を抑制する。

【解決手段】 本発明の電気光学装置は、互いに交差する方向に延在する走査線21及びデータ線13と、データ線13に一端が接続された二端子型非線形素子であって、第1導電層141と、絶縁層145と、第1導電層141よりも抵抗率が低い材料からなる第2導電層131,142とを積層してなる二端子型非線形素子14と、二端子型非線形素子14の他端に接続され、走査線21に電気光学物質を挟んで対向する画素電極16と、第2導電層131,142と同一の材料からなり、走査線21と交差する補助容量線17と、補助容量線17に接続された第1電極181と画素電極16に接続された第2電極182とが相互に対向してなる補助容量18とを備えている。

(もっと読む)

表示装置

【課題】 消費電力を減少させ且つ高解像度の大画面を実現する表示装置を提供する。

【解決手段】 本発明は、表示装置に関する。スイッチング素子を有する複数の画素と、スイッチング素子に電気的に接続され、順に出力信号を生成する複数のステージを有するシフトレジスタと、複数のクロック信号を伝達する複数のクロック信号線と、制御信号を伝達する少なくとも一つの制御信号線と、クロック信号線及び制御信号線とステージとを接続する複数の端子線とを備える。端子線は、少なくとも二つのステージに共通に接続されている共通端子線を少なくとも一つ有する。共通端子線を備える構成により、二つのステージが一つのゲートオフ電圧端子を共有することによって、ゲート駆動部が占める面積を減らすことができる。これにより、大画面及び高解像度を実現でき、消費電力を減らすことができる表示装置を提供できる。

(もっと読む)

表示装置およびその製造方法

【課題】駆動能力の向上と、光リークの防止とを両立することが容易であり、画像品質を向上する。

【解決手段】表示部12の画素をスイッチング制御する画素トランジスタ16のチャネル領域を、多結晶の半導体により形成し、単結晶の半導体の場合よりも光感度を低くして、光リークを抑制する。そして、表示部12を駆動する駆動部13の駆動トランジスタ18のチャネル領域を単結晶の半導体により形成し、多結晶の半導体の場合よりキャリア移動度を高くして、駆動能力を向上する。

(もっと読む)

アレイ基板とこれを有する表示装置と、その駆動装置及び方法

【課題】 消費電力を低減するための表示パネルのアレイ基板と、これを有する表示装置と、その駆動装置及び方法が開示される。

【解決手段】 アレイ基板は、データラインとスキャンラインにより定義される領域に形成された画素部と、複数のステージが接続され、各ステージの出力信号をスキャンラインに出力するシフトレジスタを含む。4K−3番目ステージの出力端は4K−3番目スキャンラインに接続され(ここで、Kは自然数)、4K−2番目ステージの出力端は4K−1番目スキャンラインに接続され、4K−1番目ステージの出力端は4K−2番目ステージに接続され、4K番目ステージの出力端は4K番目スキャンラインに接続される。従って、4Hのパルス周期を有する共通電圧を用いた1ライン反転方式を適用することで、表示装置の消費電力の消耗を節減できる。

(もっと読む)

表示装置

【課題】表示装置において、駆動用ICの個数を減らしても、従来よりも表示品位の低下を抑止する。

【解決手段】行列状に設けられた複数の画素電極4と、各画素電極4同士の間で行方向に延びる複数のゲート線1と、各画素電極4同士の間で列方向に延びる複数のソース線2と、複数のゲート線1及びソース線2に接続され各画素電極4毎に設けられたTFT3と、画素電極4に対応して規定された絵素ドットとを備えた表示装置であって、ソース線2を介して隣接する1対の絵素ドットは、サブ画素を構成し、サブ画素は、1ゲート線が延びる方向にゲート線1毎に絵素ドット1個分ずれて配列され、サブ画素の各画素電極4は、複数のソース線2の何れか1本からTFT3を介して同一のソース信号が供給されるように構成され、複数のソース線2は、互いに隣り合った2本毎に接続されている。

(もっと読む)

半導体素子の実装構造及び電気光学装置

【課題】 配線パターンの引き回しが容易になったり、基板の小型化を図ったりすることができる半導体素子の実装構造等を提供する。

【解決手段】 基板に対して、フェイスダウンボンディングするためのバンプ電極群を備えた半導体素子と、基板上の配線パターンと、を電気接続した半導体素子の実装構造等であって、バンプ電極群が、半導体素子の一辺に沿って配列された第1のバンプ電極列と、半導体素子の対向する一辺から所定距離だけ離して、実質的に直線状に面内配置された第2のバンプ電極列とを含み、基板上に、第1のバンプ電極列に対応した第1の配線パターンと、第2のバンプ電極列に対応した第2の配線パターンとがそれぞれ形成してあり、かつ、鉛直方向に眺めた場合に、第1の配線パターンが半導体素子の一辺と交差するように引き出して形成してあるとともに、第2の配線パターンが、半導体素子の一辺以外の複数辺と交差するように引き出して形成してある。

(もっと読む)

非矩形表示装置

非矩形表示装置は、第1の組の列導電体ライン(12A)と第2の組の列導電体ライン(12B)とを有する。第1の組の列導電体ラインは、画素のアレイのアドレス指定エッジ部(40)から他のエッジへ直線状に延びる。列駆動回路は、アドレス指定エッジ部(40)の近くに実装される。第2の組の列導電体ラインは、画素のアレイのエッジ間に延びるが、ディスプレイの形状によりアドレス指定エッジ部で終結しない。列バス(60)は、第2のセットの複数の列導電体ライン(12)の各々の一端から列駆動回路に延びる。この列バスは、ディスプレイの形状によりディスプレイのそのエッジ部では終結しない画素の列への接続をなす。このバスは、ディスプレイの周囲の辺りで少ない空間で済むので、設計の自由度が最大になる。  (もっと読む)

(もっと読む)

非長方形表示装置

表示装置は、基板と;前記基板上に行列状に配されている表示ピクセルのアレイであって、1番目の及び最後の行は前記アレイの最上部及び最下部にあり、前記アレイの外形は非長方形である、表示ピクセルのアレイと;各々がピクセルのそれぞれの行に接続されている複数の行導体、及び各々がピクセルのそれぞれの列に接続されており、前記アレイの外側へ延在している複数の列導体と;各々が前記列導体に平行であると共に、それぞれの行導体から延在している複数の行導体のシュプールと;を有し、1番目の行のための前記シュプールは、前記アレイの外側へ延在しており、2番目の前記行から前記中間の行までの行のための前記シュプールは、前記1番目の行のための前記シュプールの一方の側に延在しており、前記中間の行の後の行から前記最後の行までの行のための前記シュプールが、前記1番目の行のためのシュプールの他方の側に延在している。  (もっと読む)

(もっと読む)

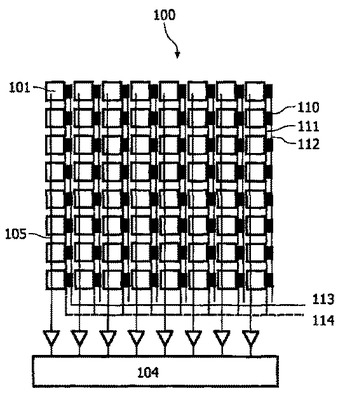

電子ユニットをアドレッシングするための回路

本発明は、例えば、X線検出器のピクセルであり得る電子ユニット(101)のアレイ装置(100)のためのアドレッシング回路に関する。全てのピクセル(101)が空間的に隣り合うシフトレジスタ(110)に接続され、このシフトレジスタ(110)が、直列に列方向に順次接続されると共に、共通のクロックライン(111,114)にも接続されている。外部トリガライン(113)を介して入力されるトリガ信号は、各クロックライン(111,114)のクロック信号ごとに行から行へ、シフトレジスタ(110)によって渡される。このプロセスでは、トリガされたシフトレジスタ(110)が、関連のピクセル(101)を活性化するので、これらのピクセルは、列方向に延在する読み出しライン(105)を介して読み出されることができる。  (もっと読む)

(もっと読む)

アクティブマトリックスディスプレイ

アクティブマトリックスディスプレイに、ディスプレイ基板の上、しかし表示領域(63)の外側で、ディスプレイの端に沿って延びる、導体ライン(62a,62b,62c)が設けられる。これらの導体ラインは、画素のアレイを定義する薄膜層に追加される、少なくとも1つの層(90)を備える。行ドライバ回路および/または列ドライバ回路は、表示領域(63)の外側で共通基板に設けられた、導体ラインに接続する部分(40,50)を有する。専用の処理を、導体ラインのために用いて、低抵抗のラインを形成することができる。これらは、行または列ドライバ回路の、共通基板への集積化または実装を助ける。  (もっと読む)

(もっと読む)

表示装置

【課題】 ドライバーを内蔵したLCDにおいて、周縁シール材によりドライバーが動作不良となることを防ぐ。

【解決手段】 シール材3が水平シフトレジスタ61及びサンプリング部62からなるドレインドライバー上を通過するが、水平シフトレジスタ61上領域においてシール材3の縁線が直線状にされている。シール材3直下ではTFT素子の動作特性が変化するので、シール材3の領域外のTFT素子と動作特性が異なるが、段間で動作特性が異なることが無くなり、表示に悪影響がでることが防がれる

(もっと読む)

表示装置及びその作製方法

【課題】 配線抵抗による電圧降下の影響や画素への信号の書き込み不良や階調不良などを防止し、より高画質のEL表示装置や液晶表示装置を代表とする表示装置を提供することを課題とする。

【解決手段】 本発明はEL表示装置や液晶表示装置を代表とする表示装置に用いられる電極や配線として、Cuを有する配線を設ける。また、該配線のCuを主成分とする導電膜は、マスクを用いたスパッタ法により形成する。このような構成により、電圧降下や信号のなまりを低減することができる。

(もっと読む)

発光装置およびその作製方法

【課題】アクティブマトリクス型の発光装置における光の取り出し効率を向上させる手段を提供する。

【解決手段】アクティブマトリクス型の発光装置において、第1の凹部101a〜第3の凹部101cを有する第1の基板100に金属膜102a〜第3の金属膜102cを形成することや、画素電極145、有機層148、凸部149aの表面を有する陰極149からなる発光素子150を形成することにより、光の損失や隣の画素への光漏れを防ぐことができる。

(もっと読む)

薄膜トランジスタ装置およびその製造方法

【課題】 電気特性の優れた多結晶TFTを提供する。

【解決手段】多結晶膜3を堆積させる工程、堆積した多結晶膜のうち所望の位置4のみを残すようにエッチングする工程、残された部分的な多結晶膜の中で所望の結晶方位の結晶粒5だけを、しかも所望の結晶面(ファセット)6を出した状態になるように異方性エッチングする工程、さらに、こうして得られた結晶核の上に膜を堆積し結晶化させる工程を用いる。

(もっと読む)

EL表示装置及び電気器具

【課題】 鮮明な多階調カラー表示の可能なEL表示装置及びそれを具備する電気器具を提供する。

【解決手段】 画素104に設けられたEL素子109の発光、非発光を時間で制御する時分割駆動方式により階調表示を行い、電流制御用TFT108の特性バラツキによる影響を防ぐ。

(もっと読む)

表示装置付き情報カード

【課題】 この発明は、表示装置付き情報カードに関し、従来から使用されている情報カードの大きさの規格の範囲内で、表示装置を付加することを課題とする。

【解決手段】 情報を記憶する記憶部と、記憶情報を表示するための有機エレクトロルミネッセンス素子からなる表示部と、表示部を駆動する制御部とを備える。

(もっと読む)

361 - 376 / 376

[ Back to top ]