Fターム[5D044GM13]の内容

デジタル記録再生の信号処理 (102,243) | 同期又はクロック (856) | ビット同期又はクロック発生 (416) | 複数のPLLを持つもの (20)

Fターム[5D044GM13]に分類される特許

1 - 20 / 20

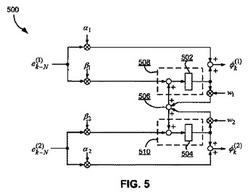

グローバルPLLベース・タイミング・リカバリ・ループの遅延補償方法及びシステム

【課題】 グローバルPLLベース・タイミング・リカバリ・ループの遅延補償方法及びシステムを提供する。

【解決手段】 一実施形態のシステムは、個々のチャネルに関連する誤差信号をそれぞれ受け取る複数の入力を備えたグローバルPLL回路と、前記グローバルPLL回路と結合された遅延補償回路と、を含む。一実施形態の方法は、個々のチャネルにそれぞれ関連する複数の誤差信号を受け取るステップと、前記誤差信号に1つ又は複数の遅延補償信号を適用するステップと、前記チャネルのそれぞれに関する位相誤差出力信号を出力するステップと、を含む。

(もっと読む)

マルチチャネル・データ検出システム用に構成された周波数エラー組み合わせ論理および周波数エラーを生成するための方法

【課題】 各チャネル用のフェーズ・ロック・ループを有するマルチチャネル・データ検出システムの周波数エラー組み合わせ論理を提供することにある。

【解決手段】 この周波数エラー組み合わせ論理は、各チャネルに関する周波数エラー情報を受信することと、受信周波数エラー情報を結合し、結合された位相エラーを生成し、各チャネルからの受信周波数エラー情報に重みを付けるように構成された組み合わせ論理と、結合された周波数エラーを少なくとも1つのチャネル・フェーズ・ロック・ループに適用するように構成された周波数エラー出力とを含む。

(もっと読む)

複数の読み取りチャネルに関する共通サンプル・タイミング制御ロジック、システム、及び方法(マルチ・チャネル・データ検出)

【課題】 例えば同時に書き込まれた磁気テープの並列トラックから複数の読み取りチャネルによって受信される信号の信号クロック制御が相関する複数の読み取りチャネルのサンプル・タイミングに関する共通サンプル・タイミング制御を提供する。

【解決手段】 共通サンプル・タイミング制御は、読み取りチャネルのうちの1つの位相誤差をそれぞれ指示する複数の位相誤差入力を備える。複数の位相誤差入力に応答するロジックは、各位相誤差入力の位相誤差指示を重み付けするとともに他の各位相誤差入力の位相誤差指示と交差結合させ、位相誤差指示の雑音分散に関する共通利得を与えるように構成される。フィードバック・ロジックは、交差結合に応答し、各読み取りチャネルに関するサンプル・タイミング位相推定値を提供するように構成される。

(もっと読む)

光ディスクコントローラおよびそれを備えた光ディスク装置

【課題】再生するディスクの種類やサポートする転送速度のモードが増えても、必要なメモリ容量を増やさない。

【解決手段】少なくとも2以上の転送速度で情報記録媒体の再生を光学的に行う光ディスク装置11のための光ディスクコントローラ114であって、情報記録媒体102を回転させる回転機構101を制御するための回転制御部113と、情報記録媒体から得られるRF再生信号を2値化し再生データを出力する2値化部106、整数の分周比を有する複数の分周器を含み、再生データに位相同期した同期クロックを生成する位相同期部107とを備え、位相同期部は、情報記録媒体の種類または転送速度に応じて分周器を切り替えて選択することにより同期クロックを生成し、分周比に応じた情報記録媒体の回転速度となるよう回転制御部が回転機構を制御する。

(もっと読む)

ワイドキャプチャ回路

【課題】光ディスク媒体に記録されたデジタルデータの再生において、PRML信号方式に適した回路構成で、ワイドキャプチャの周波数誤差検出精度を上げ、高速周波数引き込み、位相引き込みを可能とし、シーク時間の短縮を図り、これらの特性を考慮した回路構成のデジタルデータ再生装置のワイドキャプチャ回路を提供する。

【解決手段】ワイドキャプチャ回路において、同期パターン長を検出し、ICO9の発振周波数と再生信号の有する再生クロック周波数との周波数誤差を出力する第1のワイドキャプチャ部1030aと、同期パターンが存在する周期を検出し、ICO9の発振周波数と再生信号の有する再生クロック周波数との周波数誤差を出力する第2のワイドキャプチャ部1030bと、周波数誤差の2値の情報、または、周波数誤差の多値の情報を選択して出力する周波数誤差出力部1031と、位相比較器104と、スイッチ部105とを備えた。

(もっと読む)

情報記録再生装置およびその制御方法

【課題】光ディスクの形態の相違等によって正負が反転したウォブル信号が入力された場合であっても、「0」に対応するウォブル波形と「1」に対応するウォブル波形の境界点を精度良く検出することができ、ひいては、同期パターンや物理アドレスの検出性能を向上させることができる情報記録再生装置を提供する。

【解決手段】本発明に係る情報記録再生装置は、光ディスクから抽出されるウォブル信号を位相検波する位相検波部と、位相検波されたウォブル信号の位相変化点を検出する位相変化検出部と、位相変化点の時間軸方向の広がりを検出する分散判定部と、検出された位相変化点の広がりに基づいて、位相検波部に入力されたウォブル信号の極性を判定する極性判定部と、判定された極性に基づいて、位相検波部に入力されるウォブル信号の極性を反転させる極性反転部と、を備えたことを特徴とする。

(もっと読む)

情報記録再生装置、およびその記録クロック生成方法

【課題】ウォブル信号に同期して生成される記録クロックの周波数安定化を簡素な構成で実現することができる情報記録再生装置を提供する。

【解決手段】本発明に係る情報記録再生装置は、光ディスクに記録クロックを用いてデータを記録する情報記録再生装置において、光ディスクの再生信号から抽出されるウォブル信号によるフェーズロック制御に基づいて周波数制御され、記録クロックの発振源となるVCOと、VCOの周波数変動量を検出する周波数変動検出部と、を備え、VCOは、フェーズロック制御に基づく周波数制御に加えて、周波数変動検出部にて検出される周波数変動量に基づいて周波数制御される、ことを特徴とする。

(もっと読む)

再生装置及び方法

【課題】回路規模を小さくし、コストを低減することを課題とする。

【解決手段】ディスク状記録媒体から検出された再生信号を用いて、再生信号に同期したクロックを生成する第1のクロック生成手段(102〜113)と、ディスク状記録媒体上に形成されたウォブル周期に対応する周波数を含むウォブル信号を用いて、ウォブル周期に対応する周波数を有するクロックを生成する第2のクロック生成手段(119〜125)と、第2のクロック生成手段により生成されたクロックに基づいて、ウォブル信号に重畳されているアドレス情報を検出するアドレス検出手段(126〜134)とを有する再生装置が提供される。再生時には、第1のクロック生成手段と第2のクロック生成手段とを同時に動作させる。

(もっと読む)

クロック生成回路、クロック生成方法及び光ディスク装置

【課題】発振範囲が比較的狭いVCOを用いて、該発振範囲より広い周波数範囲のチャネルクロックを生成し、光ディスク最内周から最外周までを間断なく情報再生可能な光ディスク装置ならびにクロック生成回路を提供する。

【解決手段】第1クロック生成手段35a、36a、37aは、入力信号SIGに対して位相同期した第1同期クロックCK1を、第1周波数範囲において生成可能である。第2クロック生成手段35b、36b、37bは、前記入力信号に対して位相同期した第2同期クロックCK2を、前記第1周波数範囲と重複する範囲を有する第2周波数範囲において生成可能である。選択手段41は、前記第1同期クロックCK1及び前記第2同期クロックCK2のうち一方の同期クロックを選択する。制御手段40は前記入力信号の周波数を検出し、検出した周波数に応じて、前記一方の同期クロックを選択するための制御信号SLS4を生成し前記選択手段に提供する。

(もっと読む)

データ再生回路およびデータ再生装置

【課題】 複数の処理系にて再生データを並列処理する場合に、各処理系における適応型イコライザの構成の簡素化と回路規模の縮小化を図る。

【解決手段】 デジタルイコライザ511、521のタップ値は、共通のタップ値更新部518によって更新される。適応型イコライザ51、52にて生じる等化誤差e1(n)、e2(n)は、加算部514にて加算され、比率調整部515にて調整係数μが乗じられる。一方、デジタルイコライザ511、521から入力されるリサンプルデータの集合X1(n)とX2(n)が加算部516にて加算され、集合X(n)が生成される。比率調整部515から出力されるμ・e(n)は、乗算部517にて、集合X(n)に乗じられる。タップ値更新部518は、現在のタップ値H(n)に、μ・e(n)・X(n)を加算して、次のクロックタイミングのタップ値H(n+1)を生成する。

(もっと読む)

データ再生回路およびデータ再生装置

【課題】 デジタルPLLを用いながら、処理速度の高速化を円滑に図り得るデータ再生回路およびデータ再生装置を提供する。

【解決手段】 ADC30から出力されるデジタルデータは、一旦、メモリ70に格納された後、デジタルPLL41、デジタルイコライザ51および2値化回路61からなる第1の信号処理系と、デジタルPLL42、デジタルイコライザ52および2値化回路62からなる第2の信号処理系にデータユニット毎に順番に出力され、第1の信号処理系と第2の信号処理系によって並列的に処理される。このため、A/Dサンプリングするための固定クロックよりも数段低い周波数の動作クロックにて、第1の信号処理系と第2の信号処理系を動作させることができる。この動作クロックの周波数f2は、最も低くは、固定クロックの周波数f1の1/2をやや越える程度とすることができる。

(もっと読む)

PLL回路及びこれを用いた光ディスク装置

【課題】 シークによりチャネル周波数が切り替わる場合や直前に未記録領域が存在する場合でも、高密度記録されたデータ記録領域を先頭から誤りなく再生することの可能な、光ディスク装置を実現する。

【解決手段】 FM復調器(図1の6)により第2の信号の周波数を連続検出(Fwbl)し、第1の信号を入力とするPLL回路(図1の5)内の局所発振器(図1の53)の制御入力として、ループフィルタ(図1の52)出力(ΔF)と(Fwbl)を加算したものを用いる。常に周波数情報の得られる第2の信号により局所発振器(図1の53)の中心周波数を制御することで、短時間の位相引込みを実現する。

(もっと読む)

光ディスク装置

【課題】 記録時と再生時ともに信頼性の高いクロックを生成するPLL回路を提供する。

【解決手段】 アドレス情報を再生するためのウオブル信号を入力信号として、ウオブル同期クロック信号を生成するための第1のPLL回路と、再生時には、再生RF信号に同期するRF同期クロック信号を生成すると共に、記録時には、第1のPLL回路に入力される前記ウオブル信号に基づいて記録クロック信号を生成するための第2のPLL回路とを備え、前記第2のPLL回路は、記録時には、前記第1のPLL回路に入力されるウオブル信号と前記記録クロック信号或いは前記ウオブル同期クロック信号との位相比較に基づいてPLL回路を構成する光ディスク装置。

(もっと読む)

位相周波数検出回路およびPLL

【課題】 媒体の傷等の影響を受けず、変調マークに左右されずに安定に高速にPLLを引き込むことが可能な位相周波数検出回路およびPLLを提供することにある。

【解決手段】 再生信号に基づいて再生クロック信号を生成する回路において、前記再生クロック信号を生成する電圧制御発振器と、前記再生クロックから前記所定周期の信号を発生する第1の周期発生器と前記第1の周期発生器とは位相が異なり、前記再生クロックから前記所定周期の信号を発生する第2の周期発生器と、前記再生信号と前記第1の周期発生器の出力とを乗算する第1の乗算器と、前記再生信号と前記第2の周期発生器の出力とを乗算する第2の乗算器と、前記第1の乗算器の出力と第2の乗算器の出力に応じて前記電圧制御発振器の制御電圧を制御するPLL。

(もっと読む)

光ディスク装置

【課題】 CAV制御によりデータ記録を行なう場合であっても、ウォブル信号のディレイ量を適正な値にして安定したデータの記録を実行できる光ディスク装置を提供する。

【解決手段】 LPP信号fから第1の同期信号gを生成する第1のPLL回路44と、ウォブル信号eの位相をLPP信号fに合わせるディレイ回路62を有し、ウォブル信号eから第2の同期信号hを生成する第2のPLL回路46とを具備し、第1の同期信号gと第2の同期信号hとを加算して最終的な同期信号jを生成し、同期信号jに同期させてデータを記録する光ディスク装置30において、データを記録する際には、記録速度に基づいてディレイ回路62における最適なディレイ量を算出してデータ記録を実行する制御手段50を具備する。

(もっと読む)

データ記録装置

【課題】

記録媒体に形成されたクロック情報に基づいて生成された同期クロックを用いてデータの記録を行うデータ記録装置において、クロック情報の検出に不具合が生じたときでも、フレームの終了位置で書き込みを停止させることができるデータ記録装置を提供すること。

【解決手段】

本発明のデータ記録装置は、記録媒体に形成されたクロック情報に基づいて生成された同期クロックを用いてデータの記録を行うデータ記録装置であって、インターバルカウンタと、αカウンタと、セグメントカウンタとを備え、インターバルカウンタ及びαカウンタは、クロック情報に依存しない一定周波数のクロックで動作し、インターバルカウンタは、フレームを複数のセグメントに分割する分割情報が検出されたときにカウント値がリセットされ、前記セグメント長に相当するカウント値に達したときにカウント値がリセットされると共にαカウンタを起動する信号を出力し、αカウンタは、分割情報が検出されたときにカウント値がリセットされ、前記セグメント長よりも短い所定長さに相当するカウント値に達したときにカウント値がリセットされると共にセグメントカウンタのカウント値をインクリメントし、セグメントカウンタは、分割情報が検出されたときにそのカウント値をインクリメントし、フレーム長に相当するカウント値に達したときにカウント値がリセットされると共に書き込み禁止信号を出力する。

(もっと読む)

PLL回路およびディスク再生装置

【課題】 簡単な回路構成にて円滑かつ適正にPLLの周波数ずれを検出でき、これにより、PLLの位相を適正位相に円滑に追従させ得るPLL回路およびそれを内蔵したディスク再生装置を提供する。

【解決手段】 システムクロックをm個カウントする期間に生じるリサンプルタイミングの回数をリサンプルタイミングカウンタ111にてカウントする。このカウント値Krと目標値K0を周波数エラー検出回路112にて比較し、その差分値ΔF=K0−Krを算出する。算出された差分値ΔFは周波数ずれデータとしてLPF113に入力される。そして、LPF113にて直流化された後、加算器109にて位相差データΔPに加算され、デジタルVCO110に入力される。これにより、デジタルVCO110にて生成されるリサンプルタイミングが、適正周波数および適正位相に近づくよう調整される。

(もっと読む)

光ディスク装置および光ディスク装置の同期クロック生成方法

【課題】

従来の光ディスク装置では、同期クロックの元になる信号を発生する回路であるPLLの特性を切り替えるときに、光ディスクへの書き込みを一時中断しており、中断時に、記録速度が低下してしまうという問題があった

【解決手段】

光ディスクに形成されたウォブルに基づいて生成された同期クロックに対応する信号を出力し、互いに特性を異にする複数の位相同期回路と、複数の位相同期回路の出力の1つを選択して出力する選択回路と、選択回路の出力に基づいて同期クロックを生成する同期クロック生成回路を有する光ディスク装置。

(もっと読む)

クロック生成装置およびクロック生成方法

【課題】デジタル放送受信時は受信したデータストリームの基準時刻情報に随従したシステムクロックを正確に生成し、ディスク再生時には低ジッター、高ピュリティでかつ周波数変動の極小なシステムクロックを提供する。

【解決手段】データストリーム(MPEG2−TS)からの時刻基準情報(PCR)に同期した同期クロック(CK1)を生成する第1PLL回路(PLL1)と、固定クロック(CK3)を生成する発振器(VXO)と、クロック切替信号を出力する制御部(25)と、前記クロック切替信号によって、前記同期クロックと前記固定クロックを切り替え選択し、選択されたクロックをシステムクロックとして出力するクロック切替部(21g)とを備える。

(もっと読む)

ギガヘルツ周波数に効率的な遅延同期ループを有する多重位相クロック発生器を備える光学駆動回路

【課題】800MHzまたはそれ以上の周波数を有する入力クロックから、32個の異なる位相を発生させうる遅延同期ループ基盤の多重位相クロック発生器回路を備える光学(ディスク)駆動システムを提供する。

【解決手段】Nで分周されたクロックを、フィードバックループ内のM個の電圧制御される第1遅延素子に出力するための周波数分周器を有する遅延同期ループを備え、分周されていないクロックを遅延させて、M個の多重位相クロックを出力するために、フィードバックループの外部に同じM個の電圧制御される遅延素子を更に備える多重位相クロック発生器。光学駆動システムの光学駆動回路と、光学ディスク上の隣接する溝に書き込まれるマークの重複を防止するための書き込みストラテジを行う方法とを提供し、該回路及び方法は、GHzの周波数範囲で高解像度(例えば、T/32)でスイッチングする多重の書き込みストラテジ波形(チャンネル)を生成する。

(もっと読む)

1 - 20 / 20

[ Back to top ]