Fターム[5E034BC02]の内容

サーミスタ、バリスタ (5,260) | NTCの抵抗材料・組成 (181) | 金属酸化物系 (148) | Mn−Ni系 (34)

Fターム[5E034BC02]の下位に属するFターム

Mn−Ni−Cr系 (18)

Fターム[5E034BC02]に分類される特許

1 - 16 / 16

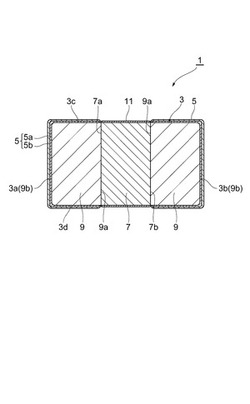

チップサーミスタ

【課題】抵抗値の調整を容易に行うことができるチップサーミスタを提供すること。

【解決手段】チップサーミスタ1は、金属酸化物を主成分とするセラミックスからなるサーミスタ部7と、金属とガラス成分とを含み且つサーミスタ部7を挟むようにサーミスタ部7の両側に配置されてサーミスタ部7と接続されている一対の導体部9と、を備えている。サーミスタ部7と一対の導体部9とは、一対の導体部9の対向方向に直交する断面形状が一対の導体部9の対向方向にわたって同じである。

(もっと読む)

サーミスタ、温度センサ及びガスセンサ

【課題】サーミスタの機械的な強度を向上し、且つ、サーミスタの反りの発生を防止することで、製品の信頼性を向上させることが可能なサーミスタ、を提供することを目的とする。

【解決手段】薄膜サーミスタ1は、基板2と、基板2上に配置されたサーミスタ膜5とを備え、基板2は、該基板2の最大厚さΔT3よりも薄い肉薄部分TH1を有し、サーミスタ膜5は、凹部52が形成されたもの、又はサーミスタ膜5の一部が除去されて孔部52が形成されたものである。これにより、薄膜サーミスタ1の素子としての強度が向上し、膜の応力によって発生する薄膜サーミスタ1の反りを防止する。

(もっと読む)

薄膜サーミスタ

【課題】薄膜からなる接続パッド部が剥がれて、接続不良を起こしてしまうような不具合を防止する。

【解決手段】接続パッド部が、セラミックス基板の一部を露出させ、引き出し線固定領域となるように形成されているので、接続パッド部およびセラミックス基板上の引き出し線固定領域の双方に引き出し線が取り付けられ、引き出し線から応力が加わった場合でも、その応力が主にセラミックス基板上の引き出し線固定領域によって受け止めることができ、引き出し線の引っ張り強度を向上させることが出来る。

(もっと読む)

積層型サーミスタ素子

【課題】高温での連続使用においても抵抗値にばらつきがなく、信頼性の高い積層型サーミスタ素子を提供すること。

【解決手段】少なくとも一対の内部電極層と、内部電極層の間に挟まれるサーミスタ層とを有する素子本体と、素子本体の表面に形成され、内部電極層と電気的に接続する外部電極層とを有する積層型サーミスタ素子であって、外部電極層は、素子本体の表面に直接に形成される第1外部電極層と、第1外部電極層の表面に形成される第2外部電極層とを有し、第1外部電極層が白金粒子とセラミック粒子とを含み、第2外部電極層が白金粒子で構成され、第1外部電極層における白金粒子とセラミック粒子との合計を100vol%とした時に、セラミック粒子が30〜50vol%であることを特徴とする。

(もっと読む)

サーミスタ素子

【課題】外部電極層にリード端子を強固に抵抗溶接することが可能で、高温での連続使用においても信頼性の高いサーミスタ素子を提供すること。

【解決手段】サーミスタ層を有する素子本体と、素子本体の表面に形成される外部電極層とを有するサーミスタ素子であって、外部電極層は、素子本体の表面に直接に形成される第1外部電極層と、第1外部電極層の表面に形成される第2外部電極層とを有し、第1外部電極層が白金粒子とセラミック粒子とを含み、第2外部電極層が白金粒子で構成され、第1外部電極層の厚みをtaと表した場合に、5μm≦ta≦30μmであり、第2外部電極層の厚みをtbと表した場合に、5μm≦tb≦50μmであり、第2外部電極層には、リード端子が抵抗溶接されることを特徴とする。

(もっと読む)

薄膜サーミスタ素子

【課題】 高い応答特性が得られると共に金属系の電極材料との密着性が良い保護膜が形成された薄膜サーミスタ素子を提供すること。

【解決手段】 アルミナ基板3と、アルミナ基板3上にサーミスタ材料で形成されたサーミスタ薄膜4と、サーミスタ薄膜4上に形成された一対の櫛形電極5と、櫛形電極5の少なくとも一部と共にサーミスタ薄膜4を覆うハフニウム酸化物またはハフニウム−金属酸化物で形成された保護膜6と、を備えている。

(もっと読む)

電子部品の製造方法

【課題】 マザー基板から各電子部品への切断工程を不要とし、生産性の向上をはかった電子部品の製造方法に関する。

【解決手段】 本発明の電子部品の製造方法は、焼成により消失する消失層2を準備する消失層準備工程と、消失層上に、電子部品を形成するための、未焼成チップ7を、間隔をあけて複数個形成する未焼成チップ形成工程と、消失層上に形成された複数個の未焼成チップ7を、消失層2とともに所定のプロファイルで焼成し、消失層2を消失させるとともに、複数個の分離した焼成済チップ8を得る焼成工程とを有するようにした。

(もっと読む)

電気的多層構成素子

【課題】一方では著しく低減された寄生キャパシタンスとインダクタンスを有し、他方では例えばプリント基板への容易で省スペース的な取り付けが可能である、より高い集積密度を備えた電気的多層構成素子を提供すること。

【解決手段】上下に積層された誘電層から形成された基体を有し、前記基体内で間隔を置いて誘電層間に配置された複数の導電的電極面を有し、該電極面に複数の電極が形成されており、構成素子の電気的なコンタクトのための少なくとも2つの隆起状はんだを有しており、該隆起状はんだは、基体の表面に配設されており、前記隆起状はんだは、基体内に配設されている貫通コンタクトを介して少なくとも1つの電極と導電的に接続されており、それにより第1の電極積層部と第2の電極積層部が形成され、これらの電極積層部がそれぞれ唯1つの隆起状はんだとコンタクトするようにする。

(もっと読む)

ボロメータ用抵抗材料、それを用いた赤外線検出器用ボロメータ、及びその製造方法

【課題】ボロメータ用抵抗材料、それを用いた赤外線検出器用ボロメータ、及びその製造方法を提供すること。

【解決手段】本発明に係るボロメータ用抵抗材料は、アンチモン(Sb)に、窒素(N)、酸素(O)及びゲルマニウム(Ge)からなる群から選択された1つ以上の元素を含むものであって、このような抵抗材料は、優れた特性、すなわち、高いTCR、低い比抵抗及び低いノイズ定数 を有し、CMOS工程で一般的に用いるスパッタリング法を用いて容易に薄膜で製造され、非冷却型赤外線検出器のボロメータに抵抗体として用いることができ、赤外線検出器に優れた温度精度を具現することができる。

(もっと読む)

セラミックス材料、このセラミックス材料の製造方法、およびこのセラミックス材料からなる電子セラミックス素子

【課題】高温で長時間にわたって安定であり、室温(〜25℃)から1000℃までの温度領域において、被測定対象の温度を測定しうる電子セラミックス素子を提供する。

【解決手段】電子セラミックス素子を、一般式[SE1−xM(II)x][Cr1−y−zRyLz]O3(ここで、SEは一または複数の希土類元素、M(II)は酸化数+2の一または複数の金属元素、LはAlおよび/またはGa、RはFe,Zn,GeおよびSnから選択される一または複数の金属元素であり、0<x<1、0<y<1、0.5<z<1、y+z<1である)で表されるセラミックス材料から構成する。

(もっと読む)

積層電子部品およびその製造方法

【課題】Ni、Cu、またはAlを主成分とする内部電極を用いた場合に、内部電極と外部電極との良好な接合を形成でき、両者の低抵抗接続を実現可能な積層電子部品およびその製造方法を提供する。

【解決手段】積層電子部品1は、セラミックスからなる素体2と、素体2内に形成された複数の内部電極3とを含む積層体4を有するPTCサーミスタであり、素体2と内部電極3が積層された単位構造10を少なくとも1つ備えたものである。内部電極2は、Ni、Cu、またはAlを主成分として含んでおり、この内部電極2には、金属成分としてAg、および、Agに対して1質量%以上60質量%以下のZnを含む外部電極5,5が接続されている。

(もっと読む)

表面実装型負特性サーミスタ

【課題】ガラス層を形成することなく、めっき液によるセラミック素体の侵食を防ぐことができ、セラミック素体の素体強度が高く、優れた信頼性を有する表面実装型負特性サーミスタを提供する。

【課題を解決するための手段】Mn,Ni及びTiを含む半導体セラミック材料からなるセラミック素体と、セラミック素体の表面に形成される外部電極と、外部電極の表面に形成されるめっき膜と、を具備する表面実装型負特性サーミスタにおいて、半導体セラミック材料に含まれるMnのモル量をa、及びNiのモル量をbとしたとき、MnとNiとのモル比が55/45≦a/b≦90/10であり、かつ、半導体セラミック材料のうちMn及びNiの総モル量を100モル部としたとき、Tiが0.5モル部以上25モル部以下の範囲で含有され、セラミック素体の内部に少なくともAgを含む内部電極が埋設されるとともに、内部電極は、外部電極と導通してなることを特徴とする。

(もっと読む)

サーミスタ及びサーミスタの製造方法

【課題】リニア温度幅が広く、かつ消費電流が小さいサーミスタを提供。

【解決手段】絶縁性の基体11と、この基体11の表面に設けられた少なくとも一対の電極12a1,12a2と、この基体11の表面に形成され電極に接続されたサーミスタ膜13とを有し、サーミスタ膜はB定数が1500K以上2200K以下のサーミスタ組成物からなり、サーミスタ膜にはトリミングが施されてトリミング溝14が形成されているものである。従って、リニア温度幅が70℃以上と広く、かつ消費電流が100μAより小さい省電力仕様の温度制御回路に用いることが可能なサーミスタを提供することができる。

(もっと読む)

チップ型NTC素子

【課題】 NTC素体の表面に薄い保護層を容易に形成することを可能にしつつ、熱処理による保護層のひび割れ等の発生を防止することができるチップ型NTC素子を提供する。

【解決手段】 チップ型NTC素子1はPTC素体2を備え、PTC素体2は、素体層3と、この素体層3を挟むように素体層3に積層された素体層4A,4Bとを有している。素体層3を構成するセラミックは、例えばMn2CoO4等で形成されている。素体層4A,4Bを構成するセラミックは、好ましくはCaMnO3で形成されている。素体層4A,4Bを含むPTC素体2の外表面には、素体層4A,4Bの侵食を防止するための保護層6が形成されている。保護層6は、CaMn2O4で形成されている。PTC素体2の両端面には、Niメッキ層9を有する端子電極7A,7Bがそれぞれ形成されている。

(もっと読む)

電気的多層構成素子

本発明は、上下に積層された複数の誘電層から構築された基体(5)を有している電気的多層構成素子に関している。これらの誘電層の間には導電的な電極面が間隔をおいて配設されており、その中には複数の電極(10A,15B)が設けられている。これらの電極(10A,15B)は少なくとも2つの隆起状はんだ(10,15)によって構成素子の電気的なコンタクトのために導電的にコンタクトしている。この種の構成素子は、特に能動素子の高い集積密度を呈し、フリップチップ構造形式で基板上に簡単に取り付けることが可能である。  (もっと読む)

(もっと読む)

サーミスタ組成物及びサーミスタ素子

【課題】 高温高湿下における抵抗変化率が小さいサーミスタ組成物、及び、これを用いたサーミスタ素子を提供すること。

【解決手段】 サーミスタ10は、内部電極12とサーミスタ層14とが積層されたサーミスタ素体11と、その端面に設けられた外部端子20とを備えるものである。サーミスタ層14は、主成分であるMn酸化物、Ni酸化物及びFe酸化物と、添加物であるAl酸化物及びZr酸化物を含むサーミスタ組成物から構成されている。このサーミスタ組成物において、主成分は、各金属元素だけの比率が、Mnが30〜89.9モル%、Niが10〜69.9モル%及びFeが0.1〜50モル%である関係を満たしている。また、主成分の合計100質量部に対する、Al酸化物及びZr酸化物の含有量は、それぞれAl2O3及びZrO2に換算して、0.01〜30質量部及び0.01〜10質量部である。

(もっと読む)

1 - 16 / 16

[ Back to top ]