Fターム[5E034DE16]の内容

サーミスタ、バリスタ (5,260) | 製造、試験(PTC、NTC、バリスタ) (588) | 皮膜形成法 (31)

Fターム[5E034DE16]に分類される特許

1 - 20 / 31

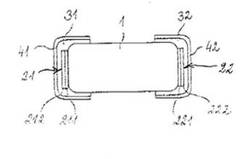

電気PTCサーミスタ部品とその製造方法

【課題】特性許容誤差を低くするPTCサーミスタ部品とその製造方法を提供する。

【解決手段】ベース本体1と、それぞれ前記ベース本体1の端面上に配置された第1の導電層と第2の導電層とを有する。第1の導電層は空乏層を破壊するバリア層21、22である。ベースの周面は第1の導電層がなく、第2の導電層はベースの各端面上に配置されたキャップ31、32を形成する。さらに、前記第1の導電層は、部品領域の分割前に基板の主要面上にスパッタを通じて生成される。キャップの形状をした第2の導電層は、分割された部品領域の端面上に、浸漬過程で生成される。

(もっと読む)

チップ部品およびその製造方法

【課題】大型でも、高性能で高品質で、実装状態で高い信頼性を確保することのできるチップ部品を提供する。

【解決手段】誘電体素子11と、該誘電体素子の内部に設けた内部電極11aと、該内部電極と電気的に接続した外部電極層15とを備え、誘電体素子11と外部電極層15の間に誘電体素子11の全面を覆うガラス層12を有し、外部電極層15は、金属成分を含む下地電極13と、樹脂電極14とからなり、樹脂電極14は、下地電極13を覆い、かつ誘電体素子11にガラス層12を介して接合する。ガラス層12は、結晶化ガラスからなることが好ましい。

(もっと読む)

薄膜サーミスタ素子

【課題】 高い応答特性が得られると共に金属系の電極材料との密着性が良い保護膜が形成された薄膜サーミスタ素子を提供すること。

【解決手段】 アルミナ基板3と、アルミナ基板3上にサーミスタ材料で形成されたサーミスタ薄膜4と、サーミスタ薄膜4上に形成された一対の櫛形電極5と、櫛形電極5の少なくとも一部と共にサーミスタ薄膜4を覆うハフニウム酸化物またはハフニウム−金属酸化物で形成された保護膜6と、を備えている。

(もっと読む)

薄膜抵抗温度センサ

【課題】基板に応力が加わって薄膜パターンが変形しても、温度検出精度への影響が少ない薄膜抵抗温度センサを提供する。

【解決手段】長方形状の基板2に、抵抗体を往復形状に接合した薄膜パターン3を形成する。薄膜パターン3は、往路部4と、往路部4に平行な復路部5と、これら往路部4と復路部5とを互い違いに接続する折り返し部6とから構成され、これら往路部4および復路部5の基板2短手方向に対する傾斜角度は、基板2の材料のポアソン比に基づいて決定される。

(もっと読む)

薄膜バリスタおよびその製造方法

【課題】保護膜を設けることによる素子の初期特性の劣化を招くことなく、耐湿性を改善して、信頼性の高い薄膜バリスタを提供する。

【解決手段】絶縁性の基体1と、基体上に形成されたZnOバリスタ層2と、その表面に、所定の電極間ギャップ13を介して対向するように配設された表面プレーナ型電極3a,3bと、ZnOバリスタ層の表面の少なくとも電極間ギャップ13に露出した領域を覆うように配設された、高抵抗ZnO薄膜からなるバッファ層4と、バッファ層を覆うように配設された保護膜5とを備えた構成とする。

保護膜として、シリコン酸化物薄膜、シリコン窒化物薄膜およびシリコン窒化酸化物薄膜からなる群より選ばれる少なくとも1種を用いる。

バリスタ特性を有するZnO薄膜の表面の結晶粒の平均的な直径を50nm以上とする。

バッファ層である高抵抗ZnO薄膜を、酸素を含む雰囲気中でスパッタ成膜して形成する。

(もっと読む)

薄膜サーミスタ素子及びその製造方法

【課題】 薄膜サーミスタ素子及びその製造方法において、電極とサーミスタ薄膜との付着強度を改善し、電極として十分な抵抗値であると共に耐熱試験においても抵抗値上昇を抑制すること。

【解決手段】 Si基板2と、Si基板2上に形成された第1サーミスタ薄膜5A及び第2サーミスタ薄膜5Bと、第1サーミスタ薄膜5A及び第2サーミスタ薄膜5B上に形成された櫛形電極3とを備えた薄膜サーミスタ素子であって、櫛形電極3が、少なくとも第1サーミスタ薄膜5A及び第2サーミスタ薄膜5Bと接触する部分が非晶質状態で成膜された白金又はその合金からなる電極層である。

(もっと読む)

薄型複合素子及びその製造方法

【課題】 サーミスタ及びバリスタをそれぞれ薄膜で構成して1チップ化することにより、ESDに強く、薄くて小型の高速熱応答性の高い薄型複合素子を得る。

【解決手段】 薄型複合素子10は、絶縁基板11上に形成された薄膜バリスタ12と、薄膜バリスタ上に形成された導電層からなる相対向する一対の櫛型電極13,14と、一対の櫛型電極を跨いでかつこれら電極の各基部が露出するように薄膜バリスタ及び電極13,14を被覆する薄膜サーミスタ16と、一対の櫛型電極の一方の露出した基部と電気的に接続するように薄膜バリスタの形成されていない絶縁基板上に形成された第1及び第2引出電極17,18と、これら電極17,18における引出線を接続するためのパッド部17c,18cを除いた基板上のすべての素子12,13,14,16を被覆する保護膜19とを備える。

(もっと読む)

薄膜バリスタおよびその製造方法

【課題】小型でありながら静電気対策部品として優れた特性を備え、量産可能な薄膜バリスタおよびその製造方法を提供する。

【解決手段】基材11表面にSiO2絶縁体膜12を備えた基板10を用い、電子ビーム蒸着によりAu電極による下部電極13を形成し、その表面に、Bi2O3を15wt%、Er2O3を2wt%含んだZnO焼結体をターゲットとして用い、高周波マグネトロンスパッタ法によりZnOバリスタ薄膜14を形成し、その表面に電子ビーム蒸着によりAu電極による上部電極15を形成する。

(もっと読む)

ポリマーヒューズおよびそれを用いた電子機器

【課題】電子機器や家電機器に使用されるヒューズに関して、微小化、軽量化が容易で、断線が確認しやすいポリマーヒューズを提供する。

【解決手段】共役系ポリマーをドーパントにより導電化してなる導電性ポリマーを主成分とするヒューズ素子1の両端に電気導体2を形成した。当該ヒューズ素子1は当該導電性ポリマー2を溶解した後、塗布(印刷)して形成する。導電性ポリマーはポリアニリン誘導体、ポリピロール誘導体およびポリチオフェン誘導体からなる群から選ばれた少なくとも一つであり、ドーパントはスルホン酸基、リン酸基、カルボン酸基およびこれらの塩基からなる群から選ばれた少なくとも一つを有する。

(もっと読む)

酵素反応熱検出システム

【課題】微少な温度変化に対して大きな抵抗値変化が得られる抵抗素子を用いて酵素反応の微少温度変化を的確に検出できる酵素反応熱検出システムを提供する。

【解決手段】酵素反応熱検出システムは、抵抗素子51及び酵素溶液F1を収容した第1容器52と、純水F2を収容した第2容器53と、試料溶液F3を収容しこれを第1容器52内に滴下可能な注入器54と、第2容器53内の純水F2を加熱するヒータ55と、抵抗素子51の抵抗値変化を電気信号(電圧)に変換・増幅し出力可能なブリッジ回路等の検出器56とを備え、注入器54から試料溶液F3を第1容器52内の酵素溶液F1に注入したときの酵素反応熱を抵抗素子51の抵抗値変化によって検出する。

(もっと読む)

薄膜センサの製造方法、薄膜センサおよび薄膜センサモジュール

【課題】熱処理などのコスト的に不利な工程を経ずに結晶を強配向化し、製品ごとの電気特性のばらつきが少ない薄膜センサの製造方法を提供すること。

【解決手段】絶縁基板と、該絶縁基板上に積層された金属からなる電気抵抗体とを有する薄膜センサの製造方法であって、

前記絶縁基板に、負の直流電圧を印加しながら、前記金属をスパッタリングして、前記電気抵抗体を形成する工程を有する

ことを特徴とする薄膜センサの製造方法。

(もっと読む)

サーミスタ薄膜及び赤外線検出用センサ並びにこれらの製造方法

【課題】 サーミスタ薄膜及び赤外線検出用センサ並びにこれらの製造方法において、1種類の組成のサーミスタ材料で異なる抵抗値を有する複数のサーミスタ薄膜を同時に得ることができ、製造コスト及び製造工程数の削減を図ること。

【解決手段】 Mn3O4−Co3O4若しくはMn3O4−Co3O4−Fe2O3系の複合金属酸化物からなるサーミスタ薄膜1Bであって、SiO2/Si基板4上に成膜されたAl2O3膜5の上に形成されている。また、赤外線検出用センサが、SiO2/Si基板4のSiO2層3上にパターン形成された第1のサーミスタ薄膜1Aと、Al2O3膜5上にパターン形成され第1のサーミスタ薄膜1Aと同一のサーミスタ材料の第2のサーミスタ薄膜1Bと、第1のサーミスタ薄膜1A上に形成された一対の第1の電極6と、第2のサーミスタ薄膜1B上に形成された一対の第2の電極7とを備えている。

(もっと読む)

面実装が可能な導電性ポリマー電子デバイスとその製造方法

面実装が可能な導電性ポリマー電子デバイスは、上部電極と下部電極の間に少なくとも1層の導電性ポリマー活性層を積層してなる。上部絶縁層と下部絶縁層はそれぞれ上部電極と下部電極を挟む。導電性第1平板端子と導電性第2平板導電性端子は下部絶縁層の上に形成される。メッキした貫通ビアにより第1と第2交差導体が形成され、形成された交差導体はそれぞれの電極を端子の一つに接続する。実施形態には、垂直に積層され、交差導体と電極により電気的に並列に接続された、2層以上の活性層を含むものがある。また、交差導体と絶縁層の接着を強化するため、上部絶縁層を貫通し、ベベルまたは面取り加工した入口穴を有する交差導体を少なくとも一つ含む実施形態もある。本面実装可能な導電性ポリマー電子デバイスの製造方法も提供する。  (もっと読む)

(もっと読む)

静電気対策部品の製造方法

【課題】本発明は、過電圧保護効果のばらつきの小さい静電気対策部品が得られる静電気対策部品の製造方法を提供することを目的とするものである。

【解決手段】セラミック基材1の上面にチタン薄膜7と銅薄膜8を形成する工程と、前記銅薄膜8の上面にレジスト9を塗布する工程と、前記チタン薄膜7と銅薄膜8で少なくとも一対の対向する引出電極となるようなパターンで形成できるように前記レジスト9に露光を施す工程と、前記レジスト9を除去する現像工程と、前記レジスト9が除去された部分のチタン薄膜7と銅薄膜8を除去して引出電極間にギャップ10を形成するエッチング工程と、前記引出電極間のギャップ10に過電圧保護材料を塗布する工程とを備え、前記現像工程の前に現像時間決定のための先行現像工程を設け、さらに、前記エッチング工程の前にエッチング時間決定のための先行エッチング工程を設けたものである。

(もっと読む)

バリスタ素体及びバリスタ

【課題】 めっき伸びやめっき付着が少ないバリスタを確実に得ることのできるバリスタ素体を提供すること。

【解決手段】 好適なバリスタ素体2は、内部電極層12及びバリスタ層14が交互に積層された構成を有する。バリスタ層14は、主成分としてZnOを含み、副成分としてCo、Pr及びZrを含む組成を有している。そして、バリスタ素体2を、その表面から深さ方向に分析したときにZrの含有量が略一定となる深さ位置を基準深さ位置としたとき、基準深さ位置におけるZrの含有量Z0、基準深さ位置よりも2μm表面側の深さ位置におけるZrの含有量Z1、基準深さ位置におけるPrの含有量P0、及び、基準深さ位置よりも2μm表面側の深さ位置におけるPrの含有量P1が、下記式(1)及び(2)を満たしている。

0.4×Z1/Z0+0.5≦P1/P0≦0.4×Z1/Z0+0.9 …(1)

1<Z1/Z0<2.2 …(2)

(もっと読む)

静電気保護素子とその製造方法

【課題】簡単な構成で、基板上の厚膜素子として製造することができ、低静電容量化が可能であり、機械的強度及び放熱特性が良好で、衝撃における影響が小さく、薄型・軽量化にも寄与する静電気保護素子とその製造方法を提供することを目的とする。

【解決手段】ZnOを主成分とし、炭化珪素を含む組成物粉末のペーストから形成されたESD保護膜12を、絶縁基板14上の電極16,18間に印刷して成る。ESD保護膜12は、ZnOを主成分とし炭化珪素を含む組成物粉末に、Mn・Co・Bi・Sb或いは希土類元素を含む組成物から成り、この組成物粉末100wt%に対し、炭化珪素を10wt%〜40wt%含む組成物からなる。ESD保護膜12を挟んだ一対の電極16,18のパターンの少なくとも一方を、櫛型或いはパターン幅に差異をもたせて形成しても良い。

(もっと読む)

サーミスタ素子、これを用いた温度センサ、及びサーミスタ素子の製造方法

【課題】還元雰囲気下で600℃を超える高温域でも、適切に温度検知ができ、特性変動が抑制されたサーミスタ素子、これを用いた温度センサ、及び、サーミスタ素子の製造方法を提供する。

【解決手段】サーミスタ素子2は、サーミスタ組成物からなるサーミスタ部1aと、これを緻密に被覆する耐還元性の被覆層1bとを備える。サーミスタ部1aは、導電性を有し、結晶構造がペロブスカイト型であるペロブスカイト相1aaを含む。被覆層1bは、ペロブスカイト相を構成する元素のうち、このペロブスカイト相をABO3と表記した場合において、Aサイトに位置する金属元素のうち少なくとも1種の金属元素、例えばSrと、Bサイトに位置する金属元素のうち少なくとも1種の金属元素、例えばAlと、を含む複酸化物、例えばSrAl2O4からなる。

(もっと読む)

サーミスタ薄膜及びその製造方法

【課題】 サーミスタ薄膜及びその製造方法において、エッチング法により高精度にパターニングされた薄膜を得ること。

【解決手段】 Si基板上のSiO2層又はAl2O3基板の基板2上にパターン形成されたMn3O4−Co3O4若しくはMn3O4−Co3O4−Fe2O3系の複合金属酸化物からなるサーミスタ薄膜1であって、HCl液をエッチング液としたエッチングによりパターン形成されている。これにより、リフトオフ法の場合に生じる薄膜端部の持ち上がり等がなく、高精度なパターン形状を得ることができる。したがって、パターニングされた本発明のサーミスタ薄膜1上に金属電極を形成しても、断線等の発生を抑制することができる。

(もっと読む)

温度感知素子

【課題】リード付き温度センサの耐腐食性および信頼性の向上

【解決手段】温度変化により抵抗値が変化する素子と、該素子の軸線上に延長するリードと、該素子を包囲する樹脂被覆とを有し、該樹脂被覆の表面に、平均粒径が5μ以下の疎水性無機フィラーが多数存在することを特徴とする温度感知素子。特に、温度変化により抵抗値が変化する素子と、該素子の両端に電気的に接続された電極と、該電極のそれぞれに電気的に接続され、該素子及び該電極によって構成された集積体の軸方向に伸びたリード線と、該素子を包囲しかつ該電極の少なくとも一部を被覆し、該素子と該電極間を固定する無機絶縁部材と、少なくとも該電極と該リード線の接続部を覆う樹脂被覆とを有し、該樹脂被覆の表面に、平均粒径が5μ以下の疎水性無機フィラーが多数存在する被覆を有することを特徴とする温度センサに関する。

(もっと読む)

積層型チップバリスタ及びその製造方法、並びに積層型素子

【課題】 外部電極の表面にめっき層をさらに形成させた場合であってもバリスタ電圧の低下が少ない積層型チップバリスタ及びその製造方法を提供すること。

【解決手段】 積層型チップバリスタ1は、複数のバリスタ層2、及び、当該各バリスタ層を挟むように配置された第1及び第2の内部電極4a,4bを有するバリスタ素子5と、このバリスタ素子5の端部に設けられ、第1及び第2の内部電極4a,4bにそれぞれ接続された外部電極6とから構成されるものである。また、外部電極6表面には、Niめっき層8及びSnめっき層10が順に形成されている。そして、この積層型チップバリスタ1における内部電極4a,4b中の水素含有量は、1.1×10−2g未満となっている。

(もっと読む)

1 - 20 / 31

[ Back to top ]