Fターム[5E070AB06]の内容

通信用コイル・変成器 (13,001) | 目的 (2,294) | 電気的特性の改善、調整(例;導電性改善) (846) | Q値 (99)

Fターム[5E070AB06]に分類される特許

21 - 40 / 99

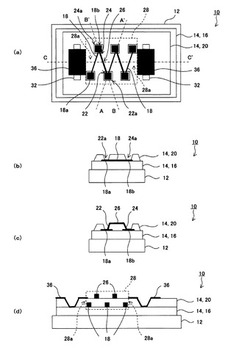

チップ一体型パッケージ、半導体装置

【課題】チップ一体型パッケージ、半導体装置を提供する。

【解決手段】半導体基板12上に積層した絶縁層14と、前記絶縁層14に横倒しに埋め

込んだ態様で形成され、前記半導体基板12に形成された回路または外部回路と電気的に

接続するソレノイド型のインダクタ28と、前記絶縁層14において前記インダクタ28

の両端の開口部28aを塞ぐ位置に埋め込んだ態様で形成した一対の磁性部材(磁性板3

5、磁性膜36、磁性樹脂38)と、を有することを特徴とする。

(もっと読む)

バラン実装デバイス

【課題】伝送線路バランのインピーダンスを整合することが可能なバラン実装デバイスを提供する。

【解決手段】一端が平衡信号出入力端30a,35aであり、他端が接地端30b,35bであり、電気的に独立して設けられた2つの平衡信号伝送路30,35と、一端が不平衡信号入出力端50aであり、他端が開放端50bである不平衡信号伝送路50とが、誘電体層24を介して対向してなる積層型バランを備えたバラン実装デバイスにおいて、一端が不平衡信号入出力端50aに導通され、他端が積層型バランに対して不平衡信号を入出力するための不平衡信号入出力端子部59に導通され、不平衡信号伝送路50の不平衡信号入出力端50aを有する側の平面スパイラル部50dの中心スペース部E2に配置されたインダクタ120を不平衡信号伝送路50と直列接続する。

(もっと読む)

低損失多層オンチップインダクタ

【課題】多層構造のオンチップインダクタ素子において、インダクタの表皮効果を低減してQ値を向上させる。

【解決手段】単一のインダクタ配線1から構成される、又は複数のインダクタ配線1を上下に積層して並列接続したものから構成されるインダクタ配線層を3層以上有し、各インダクタ配線層は上下に積層されて直列接続されており、最上層と最下層のインダクタ配線層を除く中間層の各インダクタ配線層の実効的な膜厚が、該最上層及び最下層のインダクタ配線層の実効的な膜厚よりも大きいことを特徴とする、半導体基板上絶縁膜中のオンチップインダクタである。

(もっと読む)

電子部品の製造方法

【課題】

本発明は、導電体層の形状精度に優れる電子部品の製造方法を提供することを目的とする。

【解決手段】

本発明は、絶縁体層を用意するA工程と前記絶縁体層に所定の導電体層を形成するB工程からなる。前記B工程は、前記所定の導電体層の形状に対応する突起を型の下面に有する第1型を用意する第1工程と、前記第1型を前記絶縁体層に押圧することにより前記所定の導電体層の収納領域を前記絶縁体層に形成する第2工程と、前記絶縁体層に導電体ペーストを印刷して導電体層を形成する第3工程と、前記所定の導電体層の形状に対応する溝を型の下面に有する第2型を用意する第4工程と、前記第2型を前記導電体層に押圧することにより前記所定の導電体層を形成する第5工程と、前記導電体層の一部を除去することにより、前記所定の導電体層を前記絶縁体層に形成する第6工程を備える。

(もっと読む)

電子部品及びその製造方法

【課題】大きなインダクタンス値及び高いQ値を得ることができる電子部品及びその製造方法を提供する。

【解決手段】コイルLは、積層体12に内蔵されている複数のコイル導体20a,20b、複数のコイル導体20a,20bに設けられている複数のランド部22a,22b、及び、複数のランド部22a,22bを接続するビアホール導体b1により構成されている。引き出し導体24a,24bは、積層体12に内蔵され、かつ、コイルLと外部電極とを接続している。複数のコイル導体20a,20bは、z軸方向から平面視したときに、互いに重なり合うことにより長方形状の環状の軌道Rを形成している。複数のランド部22a,22bは、z軸方向から平面視したときに、軌道Rの短辺L1上において軌道Rの外側に突出し、かつ、引き出し導体24a,24bと重なっていない。

(もっと読む)

インダクタおよびキャパシタを備えた電気回路

【課題】インダクタのQ値を劣化させることなく、引き出し配線の寄生インダクタンスの影響による共振周波数の設計値からのずれを抑制した電気回路を提供する。

【解決手段】平面スパイラルコイル13を有するインダクタ10と、平面スパイラルコイル13の外側に配されたキャパシタ20を備えた電気回路であって、平面スパイラルコイル13が形成された面の上方または下方で平面スパイラルコイル13を横切る引き出し配線40が、平面スパイラルコイル13の内周端12に導通され、引き出し配線40とキャパシタ20のいずれかの電極22とが電気的に接続され、平面スパイラルコイル13の周方向において、平面スパイラルコイル13の内周端12は、平面スパイラルコイル13の外周端11と同じ側に設けられ、キャパシタ20が平面スパイラルコイル13の近傍に配置されている。

(もっと読む)

積層インダクタ

【課題】製品規格に適合しつつコイル内径を大きく設定することが可能であるとともに、小型で高Q値を有する積層インダクタを提供する。

【解決手段】コイル導体パターン2間に絶縁層3が介在するような態様で、複数のコイル導体パターンと複数の絶縁層が積層された積層体4と、絶縁層に形成されたビアホール5を介してコイル導体パターンどうしが電気的に接続されることにより形成され、積層方向に沿って中心軸を有するコイル6と、積層体の実装面に形成され、各外部電極にコイルの一対の端部が、絶縁層に形成されたビアホールを介してそれぞれ電気的に接続された一対の外部電極7とを備え、各コイル導体パターンは、その一部が積層体の実装面を除いた非実装面の一部に露出している構成とする。

(もっと読む)

スパイラルインダクタ

【課題】導体線11の抵抗値が低くQ値が高いスパイラルインダクタを提供する。

【解決手段】スパイラルインダクタは、平板状の絶縁基板10と、絶縁基板10の主表面に配置されたらせん形状を有する導体線11とを有する。導体線11は線分状の複数の要素P1〜P12を直列に接続した多角形に近似した形状を有する。要素P1〜P12同士の接続箇所において導体線11の外側の角部を切り欠いたベンド部C1〜C11をそれぞれ形成することにより、高周波の分野において導体線11の外側の角部で発生する反射を抑制することができる。

(もっと読む)

積層型電子部品

【課題】互いに磁気的に負に結合するコイル間の磁気的な結合係数を適切な大きさにすると共に、形状を小型化する。

【解決手段】絶縁体層11A〜11Nとコイル用導体パターン12A〜12D、13A〜13Dを積層し、コイル用導体パターンによって内部にコイルが形成された第1のコイル部、絶縁体層とコイル用導体パターンを積層し、コイル用導体パターンによって内部にコイルが形成された第2のコイル部及び、第1のコイル部と第2のコイル部間に配置された磁気結合用窓Hを有する電極を積み重ねて積層体が形成され、第1のコイル部と第2のコイル部間に配置された電極は磁気的結合用窓Hに連なるスリットSが形成される。第1のコイル部のコイルと第2のコイル部のコイルは、磁気的に負に結合させる。

(もっと読む)

インダクタとその製造方法

【課題】インダクタ配線を2種類以上の組成の異なる金属により構成することにより、簡単な工程により精度よく再現性よく凹凸を設けることができて高周波領域で動作する時の表皮効果によるQ値の減少を精度よく再現性よく抑制できるインダクタおよびそのインダクタの製造方法を提供する。

【解決手段】本発明のインダクタ100は、半導体基板101と、この半導体基板101の上部に2種類以上の金属元素を含む金属層1111、1112が多層に積層された積層金属層からなるインダクタ配線111とを備え、このインダクタ配線111は、積層金属層を半導体基板101の上部に螺旋状で平面形状に配置され、積層金属層のうち隣接する少なくともいずれか2層の金属層1111、1112は積層方向に垂直な方向の幅が異なって配置されている。

(もっと読む)

スパイラルインダクタ

【課題】インダクタのQ値を減少させることなく、外部回路からのノイズを遮断するシールド部材12bを小型化する。

【解決手段】スパイラルインダクタは、第1の導体層に配置されたらせん形状を有する第1の導体線11aと、第2の導体層に配置された、第1の導体線11aと略同一のらせん形状を有する第2の導体線12aと、第1の導体層及び第2の導体層の間に配置された絶縁膜と、第2の導体線12aの長さ方向に沿って並べられ、絶縁膜を貫通して第1の導体線11aと第2の導体線12aとの間をそれぞれ電気的に接続する複数のビア21と、第2の導体線12aの周囲を取り囲むシールド部材12bとを備える。第2の導体線12aの最外周部分P1〜P8のうち少なくともシールド部材12bに近接する部分P2、P4、P6、P8において、内側ビア21bが第2の導体線12aの線幅方向の中心よりも内側で第2の導体線12aに接触している。

(もっと読む)

インダクタ素子

【課題】シリコン基板の抵抗の変動の影響を受けずに、Q値が高く且つばらつきの少ないインダクタ素子を提供する。

【解決手段】インダクタ素子では、絶縁膜2を介してP型シリコン基板1の上にインダクタ3が形成されている。P型シリコン基板1の上面では、P型シリコン基板1よりも高濃度なP+層6とN+層5とが互いに間隔を開けて形成されており、P+層6とP型シリコン基板1の一部分7とN+層5とはこの順で繰り返し形成されており、それぞれは縞状に形成されている。

(もっと読む)

電子部品及びこれを備えた電子機器

【課題】Q値の低下を抑制でき、小型化が可能な電子部品及びそれを備えた電子機器を提供すること。

【解決手段】基板5と、基板5上に設けられた絶縁層7と、絶縁層7の基板5とは反対側の面7aに設けられたスパイラルコイル8と、スパイラルコイル8と電気的に接続される外部端子12とを備えており、外部端子12は、基板5の側面5cに対向するように設けられていることを特徴とする電子部品2。

(もっと読む)

スパイラルインダクタ

【課題】複数のビアが導体線に接触する線幅方向の位置を最適化してスパイラルインダクタのQ値を向上させる。

【解決手段】スパイラルインダクタは、第1の導体層に配置されたらせん形状を有する第1の導体線11aと、第2の導体層に配置された、第1の導体線11aと略同一のらせん形状を有する第2の導体線12と、第1の導体層及び第2の導体層の間に配置された絶縁膜と、第2の導体線12の長さ方向に沿って並べられ、絶縁膜を貫通して第1の導体線11aと第2の導体線12との間をそれぞれ電気的に接続する複数のビア21とを備える。複数のビア21には、第2の導体線12の線幅方向の中心よりも外側で第2の導体線12に接触する外側ビア21aと、前述した中心よりも内側で第2の導体線12に接触する内側ビア21bとが含まれる。

(もっと読む)

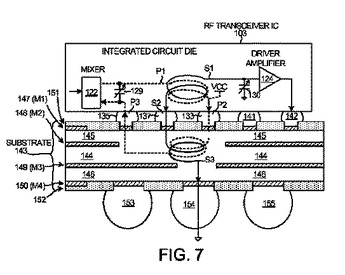

非半導体基板内に少なくとも部分的に配置された高Q変圧器

アセンブリは非半導体基板に例えば複数の低抵抗マイクロバンプによってフリップチップボンドされた集積回路ダイを含む。一つの新規な態様では、新規な高周波数変圧器の少なくとも一部が非半導体基板内に配置され、ここでは前記非半導体基板がボール・グリッド・アレイ(BGA)集積回路パッケージの基板である。低抵抗マイクロバンプの少なくとも一つは前記基板内の前記変圧器の部分を前記集積回路ダイ内の回路に接続する。2ギガヘルツで、前記新規な変圧器は少なくとも0.4のカップリング係数kおよび少なくとも10の変圧器品質ファクタQを有する。前記新規な変圧器構造は、セルラフォン内のRFトランシーバの送信チェーン内のドライバ増幅器のシングルエンド入力に差動出力をカップリングする用途に用いられる。  (もっと読む)

(もっと読む)

LC複合部品この発明は、複数の誘電体層の積層体内にインダクタ及びキャパシタを構成してなる、例えば帯域通過フィルタ等のLC複合部品に関するものである。

【課題】共振器のQ値を高く保ったまま全体に小型化でき、また共振器間の結合の自由度を高めたLC複合部品を構成する。

【解決手段】誘電体層101にはキャパシタ電極111,112およびそれらから引き出された入出力端子電極113,114が形成されていて、誘電体層102にはグランド電極120、誘電体層106にはキャパシタ電極140がそれぞれ形成されている。誘電体層103には直線状の線路電極131a,132a、誘電体層104にはコ字状の線路電極131b,132b、誘電体層105にはクランク状の線路電極131c,132c、がそれぞれ形成されている。誘電体層103,104,105には各線路電極の端部同士を接続するビア電極161a,162a,161b,162b,161c,162cが形成され、これらのビア電極と線路電極とによって二重螺旋状の電極が構成されている。

(もっと読む)

インダクタおよびフィルタ

【課題】高い構造強度と高いQ値とを有するインダクタの提供を図る。

【解決手段】インダクタ10は、エアブリッジ部12とエアブリッジ部13とを備える。エアブリッジ部12は、基板1上の複数の支持位置11の間に、基板1から浮き上がる状態で架設される。エアブリッジ部13は、エアブリッジ部12上の複数の支持位置11の間に、第1のエアブリッジ部12から浮き上がる状態で架設される。これによりエアブリッジ部12とエアブリッジ部13とが並列に接続されて電流が分散し、エアブリッジ部12およびエアブリッジ部13それぞれでの導体損が低減する。

(もっと読む)

半導体装置及びその製造方法

【課題】Q値を向上しかつ大電流を流すことが可能なインダクタの提供。

【解決手段】半導体基板1上に絶縁膜2を設ける。絶縁膜2上に螺旋状のインダクタ9を設ける。インダクタ9の表面に導電簿層(めっき層)8を設ける。導電簿層8はインダクタ9より導電率が高い。

(もっと読む)

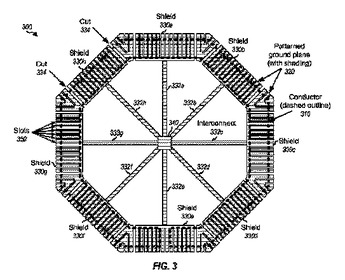

パターン化された接地平面を有するインダクタ

パターン化された接地平面を有するインダクタが、説明される。一設計においては、インダクタは、第1の層上に形成された導体と、その導体の下の第2の層上に形成されたパターン化された接地平面と、を含む。パターン化された接地平面は、オープンな中心エリアと、導体の形状に整合した形状と、を有する。パターン化された接地平面は、複数のシールド、例えば、八角形の形状の導体の8つの辺についての8つのシールド、を含んでいる。各シールドは、導体に垂直に形成された複数のスロットを有する。パターン化された接地平面を別個のシールドへと分割することと、各シールド上にスロットを形成することとは、パターン化された接地平面上の渦電流の流れを防止するのに役立ち、これは、インダクタのQを改善することができる。複数の相互接続は、複数のシールドを回路接地へと結合し、この回路接地は、導体の中心に位置することができる。  (もっと読む)

(もっと読む)

電子部品

【課題】縦方向に空隙を介し離間して設けられたスパイラル状のコイルを有する電子部品において、機械強度および耐衝撃能力を確保すること。

【解決手段】本発明は、基板50と、基板50上に設けられたスパイラル状の第1コイル10と、第1コイル10上方に空隙を介し離間して設けられたスパイラル状の第2コイル20と、第1コイル10と第2コイル20とを電気的に接続する第1接続部32と、基板50上に設けられ、第1コイル10または第2コイル20を外部と接続するための配線18、28と、第2コイル20の最外周の外側の側面に機械的に接続され、配線18、28または第1コイル10が形成されていない基板50上に機械的に接続された第2接続部38と、を具備する電子部品である。

(もっと読む)

21 - 40 / 99

[ Back to top ]