Fターム[5E082FG46]の内容

固定コンデンサ及びコンデンサ製造装置 (37,594) | 気体・固体誘電体 (7,068) | 気体・固体誘電体の製造・形成手段 (1,162) | 塗布、印刷 (820)

Fターム[5E082FG46]に分類される特許

141 - 160 / 820

積層セラミックコンデンサ

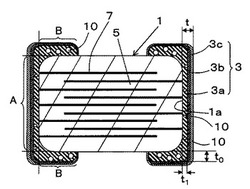

【課題】 内部電極層との接続が強固で、かつ高い耐熱衝撃性を有する外部電極を具備する積層セラミックコンデンサを提供する。

【解決手段】外部電極3が、金属とガラスとの焼結体からなる下地電極3aと、該下地電極3aの表面を覆うめっき膜とを有し、前記積層セラミックコンデンサを縦断面視したときに、前記下地電極3aと前記めっき膜3b、3cとの合計厚みが20μm以下であるとともに、前記下地電極3aは、前記コンデンサ本体1の前記側面側Bの厚みt0が前記端面側Aの厚みt1よりも厚く、かつ前記下地電極3aの前記側面側Bに存在する空隙10の面積割合が前記端面側Aに存在する空隙10の面積割合よりも大きい。

(もっと読む)

セラミックコンデンサ

【課題】回路基板において発生する振動音の大きさを好適に低減することができるセラミックコンデンサを提供することを課題とする。

【解決手段】誘電体素体21と誘電体素体21の両端部に設けられた外部電極22とを有するセラミックコンデンサ素子11と、外部電極22と回路基板13とを接続する接続端子12と、を備えたセラミックコンデンサ10であって、接続端子12は、回路基板13および外部電極22から離れた部分において、複数回屈曲させた屈曲部28を有していることを特徴とする。

(もっと読む)

セラミックコンデンサ

【課題】セラミックコンデンサに接続された回路基板において発生する振動音を抑制することができるセラミックコンデンサを提供する。

【解決手段】セラミックコンデンサは、誘電体を含む誘電体素体と、誘電体の少なくとも一部を介して対向する内部電極と、内部電極に接続する一対の外部電極と、回路基板と外部電極との距離を一定間隔に保ち、回路基板と外部電極とを電気的に接続可能な接続端子と、を有し、接続端子は、外部電極の回路基板側端面に接続端子の一端が固定される。

(もっと読む)

誘電体セラミックおよびそれを用いた積層セラミックコンデンサ

【課題】積層セラミックコンデンサの誘電体層として用いた場合に、寿命特性に優れた積層セラミックコンデンサを得ることが可能な誘電体セラミックおよびそれを用いて誘電体層を形成した信頼性(寿命特性)に優れた積層セラミックコンデンサを提供する。

【解決手段】(Ba1-x-y,Cax,Sry)(Ti1-a,Gea)O3で表わされ、0≦x≦0.20,0≦y≦0.40,0.001≦a≦0.20を満たすペロブスカイト化合物を主成分とし、このぺロブスカイト化合物1mol部に対して、Si化合物をSi換算で0<Si≦0.20mol部の割合で含有させる。

また、(Ba1-x-y,Cax,Sry)(Ti1-a,Gea)O3で表されるぺロブスカイト化合物1mol部に対し、V,Mn,Fe,およびCuからなる元素群より選ばれる少なくとも1種の化合物を、各元素換算で0.05mol部以下の割合で含有させる。

(もっと読む)

積層帯域通過フィルタ

【課題】小型・低損失で且つ通過帯域から通過帯域外への減衰が急峻であり、帯域内でのリップルの少ない積層帯域通過フィルタを構成する。

【解決手段】接地電極形成層(101)の接地電極(109)とキャパシタ電極形成層(102)のキャパシタ電極(111)〜(115)との間にそれぞれ容量を形成し、ビア電極(131)〜(140)および線路電極(116)〜(120)によって複数のインダクタ電極を構成するとともに、それらのループ面をインダクタ電極の配列方向に見たときにループの面同士が一部で重なるようにする。また、入力側(1段目)のLC並列共振器のインダクタ電極によるループとそれに隣接する2段目のLC並列共振器のインダクタ電極によるループの方向と、出力側(5段目)のLC並列共振器のインダクタ電極によるループとそれに隣接する4段目のLC並列共振器のインダクタ電極によるループの方向とを逆にする。

(もっと読む)

積層型電子部品およびその製造方法

【課題】積層体の所定の面上であって、複数の内部電極の各端部が露出した箇所に、直接、無電解めっきを施すことによって、複数の内部電極の各端部を互いに電気的に接続する外部電極を、良好な品質をもって形成できるようにし、実効体積率に優れかつ信頼性の高い、積層型電子部品を提供する。

【解決手段】積層体5として、内部電極3a,3bが露出する端面6において、隣り合う内部電極3a,3bが互いに電気的に絶縁されているとともに、絶縁体層2の厚み方向に測定した、隣り合う内部電極3a,3b間の間隔sが50μm以下であり、かつ端面6に対する内部電極3a,3bの突出長さpが0.1μm以上であるものを用意する。無電解めっき工程において、複数の内部電極3a,3bの端部に析出しためっき析出物が相互に接続されるように当該めっき析出物を成長させる。

(もっと読む)

セラミック電子部品

【課題】小型化が可能であり、端子電極とセラミック素体との固着強度に優れるセラミック電子部品を提供すること。

【解決手段】本発明は、金属成分を含有する内部電極が埋設されたセラミック素体1と、内部電極が露出するセラミック素体の両端面11をそれぞれ覆うように設けられる一対の端子電極3と、を備えるセラミック電子部品100であって、端子電極3は、セラミック素体1側から第1の電極層と、導体グリーンシートを焼付けて形成される第2の電極層と、を有し、第2の電極層が内部電極から拡散した金属成分を含有するセラミック電子部品100を提供する。

(もっと読む)

薄膜キャパシタの製造方法及び該方法により得られた薄膜キャパシタ

【課題】薄膜キャパシタにおける諸特性低下の原因となるヒロックを抑制し、リーク電流特性及び絶縁耐圧特性に優れた薄膜キャパシタを製造する。

【解決手段】下部電極を形成した後、300℃よりも高い温度のアニール処理を行わずに組成物を下部電極上に塗布し、乾燥は室温〜500℃の範囲内の所定の温度で行い、焼成は乾燥温度よりも高い500〜800℃の範囲内の所定の温度で行い、塗布から焼成までの工程は塗布から焼成までの工程を1回又は2回以上行うか或いは塗布から乾燥までの工程を2回以上行った後、焼成を1回行い、初回の焼成後に形成される誘電体薄膜の厚さは20〜600nmにすることを特徴とする。下部電極の厚さと初回の焼成後に形成される誘電体薄膜の厚さの比(下部電極の厚さ/誘電体薄膜の厚さ)は0.10〜15.0の範囲とするのが好ましい。

(もっと読む)

チップ型電子部品

【課題】小型であっても視認性が高くかつ機械的強度の高いチップ型電子部品、ならびに、外部電極の破壊を防止でき、かつセラミック本体を大きくできるチップ型電子部品を提供することである。

【解決手段】セラミックからなる絶縁層と導体層とが交互に積層されたセラミック本体により構成され、前記セラミック本体の積層方向における少なくとも1つの面が凸状に湾曲する第1湾曲面であり、前記セラミック本体の積層方向における膨張率が絶対値で5%より大きい、チップ型電子部品である。前記第1湾曲面の曲率半径が5.2mm以下である。

(もっと読む)

強誘電体薄膜及び該強誘電体薄膜を用いた薄膜キャパシタ

【課題】寿命信頼性を向上し得る、強誘電体薄膜及び該強誘電体薄膜を用いた薄膜キャパシタを提供する。

【解決手段】(PbxLay)(ZrzTi(1-z))O3(式中、0.9<x<1.3、0≦y<0.1、0≦z<0.9)で示される複合金属酸化物に、Bi、Si、Pb、Ge、Sn、Al、Ga、In、Mg、Ca、Sr、Ba、V、Nb、Ta、Sc、Y、Ti、Zr、Hf、Cr、Mn、Fe、Co、Ni、Zn、Cd、Li、Na、K、P、B、Ce、Nd、Sm及びCsからなる群より選ばれた1種或いは2種以上の元素から構成される金属酸化物がある一定の割合で混合した混合複合金属酸化物の形態をとる強誘電体薄膜が、2〜23層の焼成層を積層して構成され、焼成層の厚さtが45〜500nmであり、焼成層中に存在する結晶粒の定方向最大径の平均xが200〜5000nmであり、焼成層のいずれにおいても1.5t<x<23tの関係を満たす。

(もっと読む)

セラミック電子部品およびその製造方法

【課題】たとえば積層セラミックコンデンサのようなセラミック電子部品の外部端子電極をめっきにより形成するとき、不所望な箇所にまでめっき成長が生じてしまうことがある。

【解決手段】部品本体2が与えるセラミック面が、たとえばチタン酸バリウム系セラミックからなるもので比較的高いめっき成長力を示す高めっき成長領域11と、たとえばジルコン酸カルシウム系セラミックからなるもので比較的低いめっき成長力を示す低めっき成長領域12とを有するようにする。外部端子電極の下地となる第1層13を構成するめっき膜は、内部電極5および6の露出端によって与えられる導電面を起点として析出しためっき析出物が高めっき成長領域11と低めっき成長領域12との境界を低めっき成長領域12側へと越えて成長することが制限された状態で成長することによって形成される。

(もっと読む)

セラミック系絶縁層と金属層との積層体及び当該積層体の製造方法

【課題】セラミック系絶縁層の形成方法によらず、基材として用いる金属層の構成材料を適宜選択可能であり、セラミック系絶縁層の製造プロセスにおいて当該基材の劣化や当該絶縁層の絶縁性の低下を防止して、生産歩留の向上を図ることのできるセラミック系絶縁層と金属層との積層体及び当該積層体の製造方法を提供することを目的とする。

【解決手段】上記目的を達成するため、セラミック系絶縁層30と金属層10との積層体100において、当該金属層10には、セラミック系絶縁層30が設けられる側の面に、層厚が5nm〜100nmのケイ素化合物から成る保護層20を設ける構成とする。

(もっと読む)

積層型フィルタ

【課題】インダクタンスの大きさを増加させ,小型化による共振周波数の変化を最小化させる積層型フィルタの提供。

【解決手段】積層型フィルタ200は、複数の誘電体層が積層されたセラミック本体と、上記セラミック本体の外部面に形成されてグラウンドに連結される外部接地電極と、上記誘電体層のうち少なくとも1つに形成され、一端が上記外部接地電極に連結されるインダクタパターン電極35と、上記誘電体層のうち少なくとも1つに形成されるキャパシタパターン電極55と、上記インダクタパターン電極と上記キャパシタパターン電極とを電気的に連結し、上記外部接地電極によりインダクタンスを発生させる閉ループを形成させる外部端子電極と、上記キャパシタパターン電極と上記インダクタパターン電極との間に備えられ、上記インダクタパターン電極によるインダクタンスの大きさを調節する可変誘電体層40と、を含むことができる。

(もっと読む)

セラミックスラリー、セラミックスラリーの製造方法、キャリアフィルム付きセラミックグリーンシートおよび積層セラミック電子部品の製造方法

【課題】焼結助剤としてのシリカ成分の均一性が良好なセラミックグリーンシートであってシリコーン系の離型剤を塗布したキャリアフィルムから剥離しやすいセラミックグリーンシートを形成することができるセラミックスラリーを提供する。

【解決手段】セラミックスラリーは、焼結助剤としてシリカ成分を含むセラミックスラリーであって、シリカ成分として表面改質したシリカをゾルの形態で含む。シリカ成分は、たとえば、湿式合成されたシリカの溶剤分散体であって、シリカ粒子の表面のシラノール基が溶剤中で表面改質されたものである。また、シリカ成分は、シリカ粒子の表面のシラノール基がたとえばアルキル基、フェニル基、ビニル基、メタクリロキシ基、エポキシ基、アミノ基、カルボニル基、ニトロ基またはニトリル基を含む官能基によって改質されたものである。

(もっと読む)

積層型電子部品製造装置及び積層型電子部品の製造方法

【課題】電子部品の品質不良の発生を抑制し、低コストで、かつ連続的に運転することにより積層型電子部品の製造効率(生産速度)を高めることができる積層型電子部品製造装置及び積層型電子部品の製造方法を提供する。

【解決手段】外周に離型処理が施された無端連続状の成膜基材12と、成膜基材12に対してセラミックスラリーを押圧塗布し、乾燥硬化装置により乾燥させてセラミックシートSを連続形成する成膜形成部16と、成膜基材12に対してセラミックシートSを介して接触してセラミックシートSを成膜基材12から剥離させ、剥離したセラミックシートSを外周に巻き付けることによりセラミックシートSの積層構造体S’を形成する積層支持体14と、を有する。

(もっと読む)

磁性体と誘電体との複合焼結体、およびその製造方法、ならびにそれを用いた電子部品

【課題】 本発明は、Li−Zn−Cu−Fe−Oスピネル型結晶を含むとともに、耐湿性の高い磁性体と誘電体との複合焼結体、およびその製造方法、ならびにそれを用いた電子部品を提供することを目的とする。

【解決手段】 Li−Zn−Cu−Fe−Oスピネル型結晶とFeを含むBaTiO3結晶とを含む磁性体と誘電体との複合焼結体であって、CuKα特性X線回折による、BaTiO3結晶の2θ=31.7°付近のピーク強度I1に対するバリウムカルシウムシリケートの2θ=21.5°付近のピーク強度I2の比I2/I1が0.06以下である。

(もっと読む)

積層型電子部品製造装置及び積層型電子部品の製造方法

【課題】設備の小型化及び低コスト化が可能であり、高品質の積層型電子部品を効率良く製造できる積層型電子部品製造装置及びその製造方法を得る。

【解決手段】セラミックシートSを所定の方向に連続搬送するシート搬送部材12と、シート搬送部材12で搬送されるセラミックシートSをシート搬送部材12から剥離させ、複数層となるまで回転しながら巻き付ける中間積層部材14と、中間積層部材14に巻き付けられた複数層のセラミックシートSを所定の長さに切断するシート切断部材16と、シート切断部材16で所定の長さに切断された複数層のセラミックシートSの切断片STが転写されるシート積層部材18と、を有し、中間積層部材14の回転にあわせてシート積層部材18を移動させることにより、中間積層部材14に巻き付けられた複数層のセラミックシートSの切断片STをシート積層部材18に転写する。

(もっと読む)

誘電体セラミックおよびそれを用いた積層セラミックコンデンサ

【課題】誘電体層として用いた場合に、寿命特性に優れた積層セラミックコンデンサを得ることが可能な誘電体セラミックおよびそれを用いて誘電体層を形成した信頼性(寿命特性)に優れた積層セラミックコンデンサを提供する。

【解決手段】誘電体セラミックを、BaTiO3系セラミック粒子を主相粒子とする焼結体からなり、BaTiO3系セラミック粒子が、シェル部とコア部とを備え、副成分として、R(Nd,Sm,Eu,Gd,Tb,Dy,Ho,ErおよびYから選ばれる少なくとも1種)、および、M(Mg,Mn,Ni,Co,Fe,Cr,Cu,Al,Mo,WおよびVから選ばれる少なくとも1種)を含み、RおよびMは、BaTiO3系セラミック粒子のシェル部に存在するとともに、RおよびMの合計濃度が、粒界からコア部に向かって勾配を有し、かつ、極小となる部分C2と、極大となる部分C3とを有する構成とする。

(もっと読む)

チップ型電子部品

【課題】チップ型電子部品を実装した基板にたわみが生じた場合にも、セラミック素体にクラックが生じて致命的なダメージ受をけることを抑制、防止することが可能な、信頼性の高いチップ型電子部品を提供する。

【解決手段】内部電極3a,3bを備えたセラミック素体10と、少なくともセラミック素体10の端面10a,10bを含む領域に形成され、直接または間接に内部電極3a,3bと接続するとともに、セラミック素体10と接合するように形成された樹脂電極層12a,12bと、樹脂電極層を被覆するように形成されためっき金属層13a,13bとを備えた構成とし、かつ、セラミック素体と樹脂電極層の間の密着強度を、樹脂電極層とめっき金属層の間の密着強度よりも大きくする。

(もっと読む)

積層セラミックコンデンサ

【課題】 優れた高温負荷寿命を有する積層セラミックコンデンサを提供する。

【解決手段】 複数の誘電体層5とニッケルを導体材料とする複数の内部電極層7とが交互に積層されたコンデンサ本体1と、該コンデンサ本体1の前記内部電極層7が露出した端面に設けられた外部電極3とを有する積層セラミックコンデンサであって、前記誘電体層5が、チタン酸バリウムを主成分とする主結晶粒子9と、該主結晶粒子9間に存在する粒界相11とを有する焼結体からなり、前記誘電体層5と前記内部電極層7との間に、マグネシアが固溶した酸化ニッケルの結晶相12を有する。

(もっと読む)

141 - 160 / 820

[ Back to top ]