Fターム[5E346DD07]の内容

多層プリント配線板の製造 (97,916) | 各層形成の方法 (10,210) | 誘電体層形成の方法 (151)

Fターム[5E346DD07]に分類される特許

1 - 20 / 151

半導体装置、電子装置、配線基板、半導体装置の製造方法、及び配線基板の製造方法

【課題】配線基板に半導体素子を形成する場合において、配線基板の製造工程数を少なくする。

【解決手段】コア層200の一面上には、第1配線232が設けられている。第1配線232上、及びその周囲に位置するコア層200の一面上には、半導体層236が形成されている。第1配線232及び半導体層236は、半導体素子を形成している。本実施形態において半導体素子は、第1配線232をゲート電極としたトランジスタ230であり、半導体層236と第1配線232の間に、ゲート絶縁膜234を有している。

(もっと読む)

プリント配線板及びその製造方法

【課題】ビルドアップの流れの中でコンデンサ部を形成することができるプリント配線板を提供する。

【解決手段】プリント配線板10では、上部電極接続部52は、上部電極接続部第1部52aがコンデンサ部40と接触することなくコンデンサ部40を上下方向に貫通し、コンデンサ部40の上方に設けられた上部電極接続部第3部52cを経て上部電極接続部第2部52bから上部電極42に繋がっている。また、下部電極接続部51は、コンデンサ部40の上部電極42とは接触しないが下部電極41とは接触するようにコンデンサ部40を上下方向に貫通している。このため、ビルドアップしていく流れの中で、2枚の金属箔で高誘電体層を挟んだ構造を有し後にコンデンサ部40となる高誘電体キャパシタシートでもって全面を覆ったあとでも、上部電極接続部52や下部電極接続部51を形成することができる。

(もっと読む)

積層型チップキャパシタ及びこれを備えた回路基板装置

【課題】本発明は積層型チップキャパシタに関する。

【解決手段】本発明の一様態による積層型チップキャパシタは、複数の誘電体層が積層された積層構造を有し、積層方向に沿って配列された第1キャパシタ部と第2キャパシタ部を含むキャパシタ本体と、上記キャパシタ本体の側面上に形成された少なくとも一つの第1ないし第4外部電極−上記第1及び第3外部電極は相互同じ極性を有し、第2及び第4外部電極は相互同じ極性を有するが上記第1外部電極の極性とは異なる極性を有する−と、上記キャパシタ本体の外面上に形成され、上記第1外部電極と第3外部電極を相互連結するか上記第2外部電極と第4外部電極を相互連結する少なくとも一つの連結導体ラインと、を含む。

(もっと読む)

積層配線基板とその製造方法

【課題】積層配線基板の配線層をキャパシタ下部電極として利用する場合に、密着強度を上げる微細凹凸の形成がキャパシタ特性や信頼性に不利益を与えないようにする。

【解決手段】積層基板構造内の配線層14の表面に、絶縁基板10に他の絶縁基板19aを貼り合わせるときの密着強度を確保する微細凹凸が形成されている。当該微細凹凸が形成された配線層14面上に導電層16が形成されている。当該導電層16を下部電極とし、下部電極上にキャパシタ誘電体膜17と上部電極18が積層された容量素子が形成されている。

(もっと読む)

多層配線基板

【課題】寄生インダクタンスの影響を抑え、設計の自由度を保ちつつキャパシタ−レジスタ回路を配置できる多層配線基板を提供する。

【解決手段】複数の絶縁性基板が積層された多層配線基板1は、複数の絶縁性基板の少なくとも1つを貫通する第1接続部21Aを有し、電源を供給する電源パターンと、複数の絶縁性基板の少なくとも1つを貫通する第2接続部22Aを有し、基準電圧を形成するグラウンドパターンと、高誘電率材料からなるキャパシタ部31と、高抵抗材料からなるレジスタ部32と、キャパシタ部とレジスタ部との間に形成される電極部33とを備え、電源パターンとグラウンドパターンとを電気的に直列に接続するように配置されるキャパシタ−レジスタ回路部30とを備え、キャパシタ−レジスタ回路部は、キャパシタ部、レジスタ部、及び電極部が複数の絶縁性基板の面方向に積層されて形成されていることを特徴とする。

(もっと読む)

多層セラミック基板及びその製造方法

【課題】多層セラミック基板において、最外郭の絶縁シートに形成されたビアコンタクトが外部に突出するのを抑制する。

【解決手段】本発明の多層セラミック基板100は、第1のビアコンタクト124を有する第1の絶縁シート120と、第1のビアコンタクト124と上下に整列されて接合された第2のビアコンタクト134を有する第2の絶縁シート130とを含み、第1のビアコンタクト124と第2のビアコンタクト134とは、焼成時に互いに異なる収縮率を有する導電性ペーストによって形成されている。第2のビアコンタクト134は、第1のビアコンタクト124に比べて収縮率が高く、焼成後、第1のビアコンタクト124は、第2のビアコンタクト134の内部に拡がった形状を有している。

(もっと読む)

実装基板及びその製造方法並びに電子機器

【課題】静電容量素子を内蔵する実装基板において実装基板の大きさを制限し小型化する。

【解決手段】樹脂基板(10,13,16)に貫通開口部(スルーホールTH)が形成されており、樹脂基板の貫通開口部の内壁を被覆するように下部電極20が形成されており、下部電極の上層に誘電体膜21が形成されており、誘電体膜の上層に上部電極23が形成されており、樹脂基板上に配線(31,32)が形成されている構成とする。

(もっと読む)

複合材料構造、複合材料を含む回路基板構造、及び複合材料回路基板構造を形成する方法

【課題】複合材料を含む回路基板構造と、複合材料回路基板構造を形成する方法を提供する。

【解決手段】複合材料回路基板構造は基板と、複合材料誘電層と、パターン化導線層とを含む。複合材料誘電層は基板の上に位置し、触媒誘電層とパシベーション誘電層を含む。触媒誘電層は誘電材料と触媒顆粒を含んで基板に接触する。パシベーション誘電層は誘電材料を含んで触媒誘電層に接触する。パターン化導線層は触媒誘電層の上に位置する。

(もっと読む)

異方性誘電体

【課題】自立性があり、かつ誘電率に大きな異方性を有する異方性誘電体を提供する。

【解決手段】平板状金属粒子を絶縁材料中に配向分散した金属/絶縁材料複合体からなる異方性誘電体であり、この平板状金属粒子の配向方向と平行な方向の誘電率は、この配向方向と垂直な方向の誘電率の1.5倍以上である。

(もっと読む)

配線基板及びその製造方法

【課題】コンデンサ等を配線基板に内蔵する場合、半導体チップと外部との間で誘電率が低い信号配線を構成し、信号の伝送遅延を抑制可能な配線基板を提供する。

【解決手段】本発明の配線基板10は、半導体チップ200(搭載部品)を載置し、上下を貫通する収容穴部11aが開口されたコア材11と、収容穴部11aに収容されくり抜き部100aが形成されたコンデンサ100(内蔵部品)と、コア材11の上下にそれぞれ絶縁層及び導体層を交互に積層形成した配線積層部12、13と、収容穴部11aとコンデンサ100の間隙部、及びくり抜き部100aに充填されコンデンサ100の材料より誘電率が低い樹脂充填材50、51と、樹脂充填材51を貫通するスルーホール導体60を備えている。スルーホール導体60は第1配線積層部12を介して半導体チップ100に接続される信号配線として用いられ、低い誘電率により信号の伝送遅延を抑制し得る。

(もっと読む)

配線基板

【課題】複数のセラミック層を積層してなり、内部に中空部を有し、その底面や天井面などに形成した2層以上で平行な単一の導体層、および中空部と外部との間を連通する貫通孔を有し、導体層を含む形状・寸法精度に優れた配線基板を提供する。

【解決手段】複数のセラミック層s1〜s6を積層してなり、平面視が矩形の表面3、裏面4、およびこれらの間に位置する4つの外壁面5a,5bを有する基板本体2と、該基板本体2の内部に形成され、且つセラミック層s1〜s6のうち、中層のセラミック層s2〜s4の内側に形成された中空部6と、該中空部6の天井面7および床面8と、基板本体2の表面3および裏面4との間を個別に貫通する貫通孔h1,h2と、中空部6の天井面7および床面8に、2層が平行に形成されている単一の導体層10,17と、を備えた配線基板K1であって、貫通孔h1,h2は、中空部6の天井面7および床面8において、導体層10,17が形成された領域を除いた位置に開口している、配線基板K1。

(もっと読む)

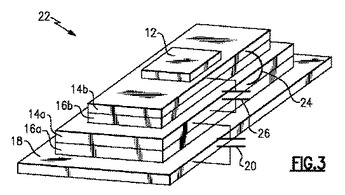

伝導性エミッション保護

1つの非限定的な実施例によれば、低伝導性エミッション基板は、対応する複数の導電層によって隔離された複数の薄い高絶縁耐力絶縁層を備えており、複数の導電層の1つが、複数の導電層の別の1つと短絡されている。  (もっと読む)

(もっと読む)

回路材料、回路積層体及びその製造方法

導電金属層と、誘電率が約3.5未満であり誘電正接が約0.006未満である誘電体複合材料とを含む回路基板積層体であり、誘電体複合材料は、ポリマー樹脂と、酸化鉄含有量が3重量パーセント以下である、約10〜約70体積パーセントのセノスフェアとを含む。  (もっと読む)

(もっと読む)

キャパシタ内蔵基板およびキャパシタ内蔵基板の製造方法

【課題】導体の脱落を抑制でき、かつ高周波のノイズの遮断が容易なキャパシタ内蔵基板およびキャパシタ内蔵基板の製造方法を提供する。

【解決手段】内蔵基板は、導電層12と基板13とキャパシタ14と導体18とを備え、上面13aにおける貫通孔13bの開口形状の短手方向の寸法が150μm以下であり、かつ短手方向の寸法に対する貫通孔13bの深さの比が2/3以上であり、キャパシタ14から導電層12まで最小の距離をなす方向に対して直交する方向の導体18の面積が0.09mm2以上である。導電層12は接地電位とする。基板13は、導電層12上に形成され、上面13aから導電層12に達する貫通孔13bを有している。キャパシタ14は上面13a上に形成されている。導体18は、貫通孔13bの内部に充填され、導電層12とキャパシタ14とを電気的に接続している。

(もっと読む)

キャパシタ、キャパシタ内蔵配線基板、及びその製造方法

【課題】キャパシタ面積が増大することを効果的に抑制するとともに、キャパシタ容量値を調整することのできるキャパシタ、キャパシタ内蔵配線基板、及びその製造方法を提供すること

【解決手段】本発明の第1の態様にかかるキャパシタ1は、基板101上に形成された下部電極102と、下部電極102上に形成された第1絶縁膜103と、第1絶縁膜103を介して下部電極102と対向配置され、下部電極102上に電極開口部106を有する上部電極104と、電極開口部106内に設けられた第2絶縁膜105と、を備え、電極開口部106の側面となる部分の上部電極104は、電極開口部106の底面と重複する部分の下部電極102よりも面積が大きいものである。

(もっと読む)

多層プリント配線板およびその製造方法

【課題】小型化、薄型化が可能であり、かつ、低コストで製造が可能な多層プリント配線板を提供する。

【解決手段】層間接続部23は、例えば、第一絶縁部11aに形成された第一導電部21aと、第一絶縁部11aに重ねて配された別な第一絶縁部11bに形成された第一導電部21bとの間を接続するように形成されていればよい。このような構成の多層プリント配線板10によれば、第一絶縁部11aと第一絶縁部11bとの間に層間接続部23を形成することで、積層された複数の第一絶縁部11の間に、抵抗体などの機能素子を形成することができる。

(もっと読む)

コンデンサ素子内蔵配線基板の製造方法

【課題】コンデンサ素子内蔵多層配線基板において、小型化・接続信頼性および電気特性を満足できない。

【解決手段】貫通導体を有する第1前駆体シートと、空洞部を有する第2前駆体シートと、多数の電極層及び多数の誘電体層を交互に積層して成る積層体、及び前記積層体を積層方向に貫通する引き出し電極部を有するコンデンサ素子と、を準備する工程と、前記第2前駆体シートの空洞部に前記コンデンサ素子を配置する工程と、前記貫通導体と前記引き出し電極部とを電気的に接続させるように、前記第1前駆体シートと前記第2前駆体シート及び前記コンデンサ素子とを積層する工程と、前記第1及び第2前駆体シートを硬化させる工程と、を備えたことを特徴とするコンデンサ素子内蔵配線基板の製造方法。

(もっと読む)

多層プリント配線板及び多層プリント配線板の製造方法

【課題】コンデンサの吸湿を抑制し、電流リークを低減した多層プリント配線板等を提供する。

【解決手段】多層プリント配線板10は、コア基板21と、第1の層間樹脂絶縁層36aと、高誘電体層43と第1及び第2層状電極41,42とを有する層状コンデンサ部40と、第2の層間樹脂絶縁層36bと、電源プレーン層52Pと、最外の層間樹脂絶縁層36dと、各層間樹脂絶縁層を貫通する複数のビア導体と、半導体素子を実装するグランド用パッド61及び電源用パッド62を有する実装部60とを備え、ビア導体はグランドビア導体61aと電源ビア導体62aとを有し、第1層状電極41はグランドビア導体61aを介してグランド用パッド61に接続され、第2層状電極42は電源ビア導体62aを介して電源用パッド62に接続される。

(もっと読む)

多層プリント配線板とその製造方法

【課題】実装された電子部品がサージから保護される多層プリント配線板であって、電子部品の高密度実装に対応し、さらに、長期にわたる使用においてもサージ保護機能の劣化が小さい多層プリント配線板と、この多層プリント配線板を容易に製造することのできる製造方法を提供する。

【解決手段】内層に酸化亜鉛シートからなるバリスタ層2を有し、かつ、このバリスタ層2が、信号ライン3、グランド層4及び電源層5に接続されている多層プリント配線板1である。

(もっと読む)

セラミック多層基板

【課題】チタン酸バリウム系の高誘電率セラミック層と低誘電率セラミック層との積層体を、低温焼成によってデラミネーションやクラックを抑制しつつ接合することである。

【解決手段】低誘電率の絶縁体からなる低誘電率層と高誘電率の誘電体からなる高誘電率層との共焼結によって得られるセラミック多層基板を提供する。低誘電率層は、xBaO−yTiO2−zZnO(x、y、zは、それぞれ、モル比率を示し、x+y+z=1;0.09≦x≦0.20;0.49≦y≦0.61;0.19≦z≦0.42)の組成を有する低誘電率セラミック成分と、この低誘電率セラミック成分100重量部に対して1.0重量部以上、5.0重量部以下添加されている酸化ホウ素含有ガラス成分と含む。高誘電率層が、CuOおよびBi2O3が添加されたチタン酸バリウム系誘電体からなる。

(もっと読む)

1 - 20 / 151

[ Back to top ]