Fターム[5E346HH02]の内容

多層プリント配線板の製造 (97,916) | 目的、課題、効果 (10,213) | 電気的特性に関するもの (2,662) | 低インピーダンス化 (111)

Fターム[5E346HH02]に分類される特許

1 - 20 / 111

層間絶縁用の樹脂フィルムおよびビルドアップ配線基板

【課題】絶縁層全体の特性(バルク特性)と、接着性などの表面特性とを両立させることができる樹脂フィルム、およびこれを用いて得られるビルドアップ配線基板を提供する。

【解決手段】ビルドアップ配線基板の層間絶縁材料として使用されるBステージ化した樹脂フィルムにおいて、熱硬化性の第1樹脂層と、その第1樹脂層の片側表面に積層され、表面粗化していない銅に対する接着強度が優れており、厚みが全体の10%以下である熱硬化性の第2樹脂層と、を有する樹脂フィルム。

(もっと読む)

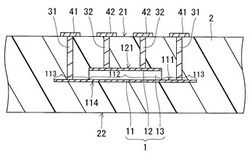

コンデンサ素子及びコンデンサ内蔵基板

【課題】コンデンサ内蔵基板に生じるインダクタンスを小さくすることが可能なコンデンサ素子、及び該コンデンサ素子を具えたコンデンサ内蔵基板を提供する。

【解決手段】本発明に係るコンデンサ素子は、第1電極層11と第2電極層12との間に誘電体層13が介在したコンデンサ素子1であって、第1電極層11は、第2電極層12側の表面111の一部が該第2電極層12によって覆われ、第1電極層11が金属箔により形成される一方、第2電極層12が金属薄膜又は金属箔により形成されている。本発明に係るコンデンサ内蔵基板は、前記コンデンサ素子1と絶縁基板2とを具え、該絶縁基板2内にコンデンサ素子1を埋設することにより絶縁基板2にコンデンサ素子1が内蔵されている。

(もっと読む)

配線基板およびその製造方法

【課題】接地または電源導体は、信号配線導体導体に沿う辺を有する開口パターンを備えることで、信号配線導体と接地または電源導体との間隔を小さく形成して、信号配線導体のインピーダンスの低減ができる高密度配線の配線基板およびその製造方法を提供する。

【解決手段】絶縁層上にセミアディティブ法により形成された第一の幅の帯状の信号配線導体3aおよび該信号配線導体3aに対して第一の間隔で隣接して配置されるとともに前記第一の幅よりも広い第二の幅にわたり延在する接地または電源導体3b、3cを具備して成る配線基板であって、前記接地または電源導体3b、3cは、前記信号配線導体3aに沿う辺を有する開口パターン11を備える。

(もっと読む)

配線基板

【課題】インピーダンスが所定の値に整合された幅の広い引き出し配線を介して半導体素子接続パッドと外部接続パッドとの間に高速の信号を効率よく伝送させることが可能な配線基板を提供すること。

【解決手段】上面側ビルドアップ接続配線部Aは、半導体素子接続パッド7に第1のピッチで接続されているとともにコア絶縁板1の上面中央部においてコア接続配線部Bに第1のピッチよりも広い第2のピッチで接続されており、コア接続配線部Bは、コア絶縁板1の中央部から外周部に向けて延在する帯状の引き出し配線2Sを含み、引き出し配線2Sの中央部側の端部が上面側ビルドアップ接続配線部Aに電気的に接続されているとともに外周部側の端部が下面側ビルドアップ接続配線部Cに電気的に接続されており、下面側ビルドアップ接続配線部Cが外部接続パッド8に電気的に接続されている。

(もっと読む)

多層配線基板およびその製造方法、並びに半導体装置

【課題】薄膜キャパシタの導電層と誘電層との界面での剥離を抑えることが可能な多層配線基板およびその製造方法、並びにこの多層配線基板を備えた半導体装置を提供する。

【解決手段】上部電極および下部電極の間に誘電層を有する薄膜キャパシタを備えた機能領域と、前記機能領域以外の周辺領域とを有し、前記周辺領域の少なくとも一部に、前記誘電層および導電層が積層された係留部が設けられ、前記導電層の前記誘電層に接する面のラフネスが、前記上部電極または前記下部電極の前記誘電層に接する面のラフネスよりも大きい多層配線基板。チップおよび前記多層配線基板を備えた半導体装置。

(もっと読む)

実装基板及びその製造方法

【課題】実装された半導体装置に供給する電源のノイズを低減できる実装基板及びその製造方法を提供すること。

【解決手段】本発明の一態様である実装基板100は、板状部材1、電源回路21、ビア31及び32を有する。板状部材1は、表面にLSIケース51、LSI52及びピン53からなる半導体装置が実装される。電源回路21は、半導体装置が実装される領域の板状部材1内に埋め込まれ、電源電圧及び接地電圧を出力する。ビア31は、半導体装置と電源回路21との間の板状部材1内に形成され、電源回路21から出力される電源電圧を半導体装置に供給する。ビア32は、半導体装置と電源回路21との間の板状部材1内に形成され、電源回路21から出力される接地電圧を半導体装置に供給する。

(もっと読む)

部品内蔵配線基板の製造方法

【課題】内蔵部品との接続信頼性に優れた配線基板を低コストで製造することができる部品内蔵配線基板の製造方法を提供すること。

【解決手段】セラミックコンデンサ101とコア基板11とを準備した後、ビルドアップ材をコア基板11のコア裏面13側に接合することで、絶縁層を形成しかつ収容穴部90の一方の開口を閉塞する。コア裏面13側の絶縁層上にセラミックコンデンサ101を搭載することで収容穴部90内にセラミックコンデンサ101を収納し、樹脂充填部93で収容穴部90の内壁面91とセラミックコンデンサ101との隙間92を埋める。コア主面12側及びコア裏面13側に形成された絶縁層を研磨し、セラミックコンデンサ101の外部電極111,112,121,122を露出させる。樹脂充填部93上に、全面めっきを施した後にパターニングを行って導体層50を形成する。

(もっと読む)

プリント回路板

【課題】信号用ビアホール部における電源インピーダンスを低減して信号電流のリターン経路を確保することで放射ノイズを低減する。

【解決手段】プリント配線板101は、電源層11、グラウンド層12、第一の信号配線層13、及び第二の信号配線層14が絶縁層を介して積層されて構成されている。IC111とIC112とが信号用ビアホール21を介して信号配線22,23で電気的に接続されている。プリント配線板101には、電源層11に電気的に接続される電源用スルーホール3と、グラウンド層12に電気的に接続されるグラウンド用スルーホール4とが形成されている。各信号配線層13,14には、一端が電源用スルーホール3に電気的に接続され、他端がグラウンド用スルーホール4に電気的に接続された各コンデンサ1,2が実装されている。

(もっと読む)

プリント配線板

【課題】 コンデンサを内蔵すると共に内蔵コンデンサとの接続を適切に取ることができるプリント配線板を提供する。

【解決手段】 チップコンデンサ20をコア基板30内に収容する。チップコンデンサ20は、銅めっき膜29を被覆した第1、第2電極21,22に銅めっきによりなるバイアホール46で電気的接続を取ってある。銅めっき膜29により第1、第2電極21,22の表面が平滑になり、接続層40に非貫通孔43を穿設した際に樹脂残さが残らず、バイアホール46とチップコンデンサ20との接続信頼性を高めることができる。

(もっと読む)

有機多層基板及びその製造方法

【課題】 有機多層基板において、内蔵された積層型電子部品と前記基板の配線導体との電気的、機械的接続が、前記電子部品の外部電極の側面電極部だけで取られていた。このため、その接続信頼性は十分とはいえなかった。また、上述の両者の接続面が狭い、該接続面から前記電子部品の内部電極までの距離が長いことから、この部分に寄生の抵抗分やインダクタンス分が生じ、この基板を使った電子機器のレスポンスを劣化させるという問題があった。

【解決手段】 前記電子部品と前記基板の配線導体との電気的、機械的接続を、前記電子部品の外部電極の側面電極部に加えて、端面電極部でも取る構成とした。

(もっと読む)

多層印刷配線板およびその製造方法、プリプレグ、樹脂付金属箔、樹脂フィルム、ならびに金属箔張積層板

【課題】スルーホールを有する領域に折り曲げ部を設けた場合でも、層間接続の抵抗値の上昇が抑制される多層印刷配線板を提供する。

【解決手段】第1の熱硬化性樹脂に由来する樹脂硬化物を含む第1の絶縁層100、および前記第1の絶縁層の両面に配置された厚さが1〜35μmである金属箔を有し、前記金属箔からなる回路層26および前記第1の絶縁層100の両面に配置された金属箔を互いに接続するスルーホール20が形成された回路基板と、前記回路基板の少なくとも一方の面上に設けられ、グリシジルアクリレート樹脂およびポリアミドイミド樹脂から選択される少なくとも1種である第2の熱硬化性樹脂に由来する樹脂硬化物を含み厚さが80μm以下である第2の絶縁層200と、を有する多層印刷配線板の前記回路基板および第2の絶縁層200が積層された領域に折り曲げ部を備えて構成する。

(もっと読む)

配線基板

【課題】高周波信号を損失少なく伝送させることが可能な配線基板を提供すること。

【解決手段】半導体素子Sが搭載される搭載部1aを有する基板1と、その上に積層されており、搭載部1aに臨む端面2aを有する絶縁層2と、絶縁層2の上面を搭載部1a側から反対側に向けて延在する帯状の信号配線3と、絶縁層2の上面の信号配線3の両側に配設された上面側接地導体4と、絶縁層2の下面に配設された下面側接地導体5とを備え、信号配線3および上面側接地導体4に半導体素子SとワイヤWを介して電気的に接続されるワイヤボンディング部8を有してなる配線基板であって、絶縁層2は、上面側接地導体4のワイヤボンディング部8に隣接する位置に、端面2aからワイヤボンディング部8よりも奥に入り込む切り欠き部6が形成されており、切り欠き部6内に上面側接地導体4と下面側接地導体5とを接続する接続導体7が被着されている。

(もっと読む)

多層配線基板

【課題】不要放射ノイズを十分に低減することができる多層配線基板を得る。

【解決手段】第1の信号電極層40、グランド電極層30、電源電極層20及び第2の信号電極層10をこの順で積み上げて積層体を構成した多層配線基板。多層配線基板の上面にはIC60が実装され、裏面には3端子コンデンサ46が実装される。第1の信号電極層40は、入力側実装用ランド42、該入力側実装用ランド42に接続した入力側電源供給パターン41、出力側実装用ランド43、該出力側実装用ランド43に接続した出力側電源供給パターン44及びグランド側実装用ランド45が設けられている。電源電極層20には電源電極21が設けられている。第2の信号電極層10にはIC実装用ランド11が設けられている。

(もっと読む)

積層型チップキャパシタ及びこれを備えた回路基板装置

【課題】本発明は積層型チップキャパシタに関する。

【解決手段】本発明の一様態による積層型チップキャパシタは、複数の誘電体層が積層された積層構造を有し、積層方向に沿って配列された第1キャパシタ部と第2キャパシタ部を含むキャパシタ本体と、上記キャパシタ本体の側面上に形成された少なくとも一つの第1ないし第4外部電極−上記第1及び第3外部電極は相互同じ極性を有し、第2及び第4外部電極は相互同じ極性を有するが上記第1外部電極の極性とは異なる極性を有する−と、上記キャパシタ本体の外面上に形成され、上記第1外部電極と第3外部電極を相互連結するか上記第2外部電極と第4外部電極を相互連結する少なくとも一つの連結導体ラインと、を含む。

(もっと読む)

セラミック回路基板およびそれを用いた電子装置

【課題】 大電流を流せる複雑な多層構造を有し、信頼性が高く、小型化や薄型化のできるセラミック回路基板および電子装置を提供すること。

【解決手段】 セラミック基板1が積層されて互いに接合されたセラミック多層基板と、セラミック多層基板の上面および下面に接合された表層金属回路板3と、内層のセラミック基板1に形成された回路貫通孔1a内に配置された内層金属回路板4と、一端が内層金属回路板4に、他端が他の内層金属回路板4または表層金属回路板3にそれぞれろう材2によって接合され、内層金属回路板4と他の内層金属回路板4または表層金属回路板3とを接続する金属柱5とを備えるセラミック回路基板である。内層金属回路板4も表層金属回路板3と同様に金属板からなるので大電流を流すことができ、回路貫通孔1aの内壁面に熱応力が加わらないようにすることができ、信頼性が高く、小型化や薄型化できるセラミック回路基板となる。

(もっと読む)

電源及びグランド対線路を含む多層配線基板構造

【課題】電源及びグランドの平板構造で見られる低特性インピーダンスを維持しつつ平板に置ける共振モードを防止する構造を提供する。

【解決手段】絶縁物層とパターニングされた導体層とを含む積層体10を有する多層配線基板において、前記積層体10内に互いに平行となるように配置された電源用の第1導電路1及びグランド用の第2導電路2と、前記第1導電路1の上面及び前記第2導電路2の上面にまたぐように設けられ、前記第1及び第2導電路側から順次積層された第1絶縁膜3と、第1導電膜4又は第1半導体膜4とを有する第1積層膜と、を備える。

(もっと読む)

ノイズ対策構造

【課題】基板のインピーダンスを低減させ、しかも、電源パターンと電源供給パターン間の電磁気的結合による高周波電流の発生を防止することにより、不要放射ノイズを抑制したノイズ対策構造を提供する。

【解決手段】IC10の電源端子11,13に接続される電源パターン3−1,3−2と、グランド端子12に接続されるグランドパターン4とを、多層回路基板2の上層21に並設し、グランドパターン5−1と電源供給パターン6とグランドパターン5−2とを、下層22に並設する。そして、3端子コンデンサ7−1を電源パターン3−1とグランドパターン4とグランドパターン5−1と電源供給パターン6とに接続し、3端子コンデンサ7−2を電源パターン3−2とグランドパターン4とグランドパターン5−2と電源供給パターン6とに接続した。

(もっと読む)

半導体装置

【課題】 半導体装置のインターポーザ基板内部に設けられた電源パターンに、GND用スルーホール、信号用スルーホール等によりに、インピーダンスが上昇するため、許容電流量を上げることができない。

【解決手段】 半導体装置に設けられた、電源用端子、グラウンド用端子、信号用端子からなる接続用端子のうち、電源用端子はすべて1つの電源領域に配置されており、電源領域には、電源用端子のみが設ける。これによりインターポーザ基板内部に設けられた電源層に不要なスルーホールを空けることがなく、インピーダンスの上昇を抑制できる。

(もっと読む)

パッケージ基板および半導体装置

【課題】多信号系のレイアウトスペースを十分に確保しつつ、電源供給系の電源ノイズを低減すること。

【解決手段】電源電圧が印加される電源プレーンを電源電極に電気的に接続する電源ビア44が通過する配線層52は、電源ビア44を取り囲む格子状グランドプレーン51が形成されている。格子状グランドプレーン51の全部は、グランドビア45を介して、グランドプレーンに電気的に接続されている。このとき、半導体装置1は、電源ビア44と格子状グランドプレーン51とは、強い相互インピーダンスをもち、電源の実効インピーダンスを著しく低減させ、電源ノイズを低減することができる。

(もっと読む)

多層プリント配線板

【課題】 高周波領域のICチップ、特に3GHzを越えても誤動作やエラーの発生しないパッケージ基板を提供する。特に、スイッチをONしてから発生する電圧降下のうち1回目と2回目の電圧降下を改善する。

【解決手段】 表裏を接続する複数のスルーホール36を備え、表裏の導体層34と内層の導体層16とを有する3層以上の多層コア基板30上に、層間絶縁層50、150と導体層158が形成された多層プリント配線板10において、

複数のスルーホール36は、ICチップ90の電源回路またはアース回路または信号回路と電気的に接続している電源用スルーホール36Pとアース用スルーホール36Eと信号用スルーホールとからなり、電源用スルーホール36Pの内、少なくともIC直下のものは、内層のアース用導体層16Eを貫通する際、延出する導体回路を有しない。

(もっと読む)

1 - 20 / 111

[ Back to top ]