Fターム[5F003AP00]の内容

バイポーラトランジスタ (11,930) | 目的 (494)

Fターム[5F003AP00]の下位に属するFターム

電流集中防止 (43)

短絡防止 (14)

断線、段切防止 (11)

誤動作、寄生効果、表面リークの防止 (62)

容量低減 (108)

二次降伏電圧、安全動作領域改善 (122)

雑音特性改善 (29)

温度特性改善 (30)

機械的強度改善 (3)

耐湿性改善 (7)

Fターム[5F003AP00]に分類される特許

1 - 20 / 65

半導体集積回路装置

【課題】絶縁素子分離型のバイポーラトランジスタの放熱性を改善する。

【解決手段】薄い半導体層の第1のエリアに配置された第1のトランジスタと、薄い半導体層の第2のエリアに配置された第2のトランジスタで構成される回路部と、を備え、第1のトランジスタは、並列接続された複数のバイポーラトランジスタ素子を構成する複数の単位能動領域の配列全体を囲って配置された素子分離溝を含み、素子分離溝を能動領域から少なくとも1μm離間して設け、能動領域で生成される熱を単位能動領域を囲んで存在する半導体領域から外方に放熱させる構成を備えてなり、第2のトランジスタは、バイポーラトランジスタ動作を行う単位能動領域と、単位能動領域を取り囲んで形成され単位能動領域から1μm以下の位置に配置された素子分離溝を含む。

(もっと読む)

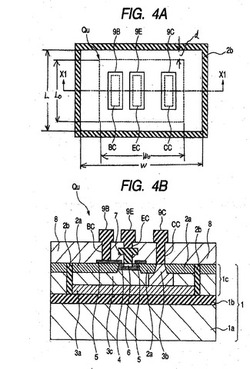

半導体装置

【課題】2層の電極構造の絶縁膜の厚み分の段差に基づく固着不良を回避したディスクリート型バイポーラトランジスタを提供する。

【解決手段】1層目のエミッタ電極7の上下に設けられるエミッタコンタクトホールCH2とエミッタスルーホールTH2を非重畳とし、1つのエミッタ電極7についてエミッタコンタクトホールCH2とエミッタスルーホールTH2互いに離間して複数配置する。これにより、2層目のエミッタ電極17表面では、最大でも、膜厚が厚い絶縁膜に設けられたエミッタスルーホールTH2の段差の影響しか及ばず、2層目の電極表面の平坦性が向上する。これにより金属プレートの固着不良を回避できる。

(もっと読む)

半導体装置、半導体装置の製造方法及びパワーアンプ素子

【課題】ウェハー上面側から基板までの電流経路を低抵抗にできる半導体装置およびその製造方法を提供する。

【解決手段】第一導電型高濃度半導体基板101と、第一導電型高濃度半導体基板101上に設けられた低濃度不純物エピタキシャル層103と、105とを含み、第一導電型高濃度半導体基板101に接続するトレンチ110が低濃度不純物エピタキシャル層103、105に設けられている半導体装置であって、トレンチ110の内壁に沿って少なくとも低濃度不純物エピタキシャル層103、105中に形成されるとともに、第一導電型高濃度半導体基板101に接続する、第一導電型高濃度半導体基板101と同一導電型の第一導電型高濃度不純物領域112と、第一導電型高濃度不純物領域112上に形成されたコンタクト111とを含む、半導体装置を提供する。

(もっと読む)

窒化物系半導体素子

【課題】オーミック電極と窒化物系半導体層とのオーミック特性が熱により劣化するのを抑制することが可能な窒化物系半導体素子を提供する。

【解決手段】この窒化物系半導体素子(窒化物系半導体レーザ素子)は、p側オーミック電極6に、約1nmの厚みを有するとともにp型コンタクト層5の主表面に接触して形成されるSi層6aと、Si層6a上に形成される約20nmの厚みを有するPd層6bとを含むとともに、n側オーミック電極9に、約1nmの厚みを有するとともにn型GaN基板1の下面に接触して形成されるSi層9aと、Si層9aの下面上に形成される約6nmの厚みを有するAl層9bと、Al層9bの下面上に形成される約30nmの厚みを有するPd層9cとを含む。

(もっと読む)

半導体装置およびその製造方法

【課題】エミッタ層の寸法幅を微細化し、半導体装置の高性能化を図る技術を提供する。

【解決手段】n型のコレクタ層2の活性領域上にp型のSiGe合金層6aと断面凸状のp型のシリコン膜7aとが形成され、シリコン膜7a内の上部にはエミッタ層として機能するn型のエミッタ拡散層13が形成されている。エミッタ拡散層13上にはエミッタ電極であるn型の多結晶シリコン膜8aおよびシリコン窒化膜9aが形成されている。多結晶シリコン膜8aの側面およびシリコン膜7aの表面に表面絶縁膜10が設けられるとともに、多結晶シリコン膜8aとシリコン膜7aとの界面50に沿って、多結晶シリコン膜8aの外側から内側に向かって突出するシリコン酸化膜からなる突出部10aが設けられている。

(もっと読む)

接合型電界効果トランジスタ及びその製造方法及び半導体装置

【課題】コレクタエピタキシャル層を薄膜化した高速バイポーラトランジスタを搭載した集積回路中に所望の高耐圧J−FETを混載可能とした半導体装置及びその製法を提供すること。

【解決手段】P型の単結晶Si基体などの第1導電型の半導体基体2上にシリコン半導体層などの第2導電型の半導体層3を積層し、この半導体層3中にAs(ヒ素)等の第2導電型の不純物によってソース領域12及びドレイン領域13を形成し、さらにこの半導体層3上に、シリコン・ゲルマニウム層によってP型の第1導電型不純物(例えば、ホウ素など)を有するゲート領域14を形成する。

(もっと読む)

ヘテロ接合バイポーラトランジスタ

【課題】パワーアンプの歪特性及び効率を悪化させずに耐破壊性を向上させることが可能なヘテロ接合バイポーラトランジスタを提供すること

【解決手段】本発明にかかるヘテロ接合バイポーラトランジスタは、第1導電型のサブコレクタ層2と、第1導電型不純物を含む第1のコレクタ層41と、第1のコレクタ層41より第1導電型不純物の濃度が高い第3のコレクタ層43と、前記第1のコレクタ層41より第1導電型不純物の濃度が低い第2のコレクタ層42と、第2導電型のベース層5と、ベース層5よりもバンドギャップの広い半導体を含む第1導電型のエミッタ層6と、第1導電型のエミッタキャップ層8と、を有するものである。

(もっと読む)

半導体装置

【課題】寄生動作を抑制した半導体装置を提供する。

【解決手段】半導体装置は、n-領域2aと、n-領域2aから離れて形成されたn-領域2cと、n-領域2aとn-領域2cとの間に形成されたn-領域2bと、n-領域2cとn-領域2bとの間に配置され、p-領域1よりも低抵抗のp拡散領域4bとを備える。n-領域2aに接するように形成されたエミッタ電極7を備える。n-領域2cに接するように形成されたコレクタ電極9を備える。n-領域2aとn-領域2bとに挟まれる領域に形成されたベース電極8を備える。n-領域2bとp拡散領域4bとが導線11で電気的に接続されている。n-領域2bの幅Xよりもn-領域2bとn-領域2cとの距離Yが長くなるように形成されている。

(もっと読む)

ヘテロ接合バイポーラトランジスタ用エピタキシャルウェハ、及びその製造方法

【課題】 ヘテロ接合バイポーラトランジスタ用エピタキシャルウェハにおいて、エミッタ層とエミッタコンタクト層との間に形成される遷移層に起因する電流利得率の低下を防止する。

【解決手段】 GaAs基板上に少なくともコレクタ層、GaAsベース層、InGaPエミッタ層、GaAsエミッタコンタクト層、及びノンアロイ層がエピタキシャル成長によって順次形成されたヘテロ接合バイポーラトランジスタ用エピタキシャルウェハにおいて、前記InGaPエミッタ層と前記GaAsエミッタコンタクト層との間に、前記InGaPエミッタ層よりも低In組成のInxGa1-xP層の薄膜層が形成されていることを特徴とする。

(もっと読む)

半導体装置

【課題】トランジスタの耐圧を互いに異ならせるために追加する工程を最小限に抑え、かつトランジスタサイズの増大を招くことなく、耐圧が互いに異なるトランジスタを得る。

【解決手段】N+ソースドレイン領域15,15及びPウェル7からなるバイポーラ構造はNMOSトランジスタ3n,5nで同じである。P+ソースドレイン領域19,19及びNウェル9からなるバイポーラ構造はPMOSトランジスタ3p,5pで同じである。保護NMOSトランジスタ5n及び内部PMOSトランジスタ3pはシリコン窒化膜23で覆われ、内部NMOSトランジスタ3n及び保護PMOSトランジスタ5pはシリコン窒化膜23には覆われていない。保護NMOSトランジスタ5nの耐圧は内部NMOSトランジスタ3nよりも低く、保護PMOSトランジスタ5pの耐圧は内部PMOSトランジスタ3pよりも低い。

(もっと読む)

化合物半導体素子およびその製造方法

【課題】 微少な電極とコンタクト層との間のコンタクト抵抗を低くできる化合物半導体素子およびそのような半導体素子を工程数を増やすことなく製造する方法を提供する。

【解決手段】 GaAs基板1上に、所定の半導体層2,3,4,5を形成した後、InGaAsから構成されるオーミックコンタクト層6を、その表面が凹凸となるように、MOCVD法またはMBE法によって形成する。そして、オーミックコンタクト層6の凹凸表面上に、横幅が10μm以下である金属電極9を形成する。オーミックコンタクト層6と金属電極9の界面における凹凸状の構造は、高低差が0.1μmから0.5μmの範囲内にあり、かつ、隣り合う山と山との間隔が0.1μmから0.5μmの範囲内にある。

(もっと読む)

ヘテロ接合バイポーラトランジスタ

【課題】高出力化に付随して要求される破壊耐圧に優れた高耐圧化特性を有するヘテロ接合バイポーラトランジスタを提供する。

【解決手段】n型GaAsサブコレクタ層101と、n型GaAsサブコレクタ層101上に位置し、GaAsよりバンドギャップが広いInGaPから構成されるn型InGaP第3コレクタ層102と、n型InGaP第3コレクタ層102上に位置するn型GaAs第2コレクタ層103と、n型GaAs第2コレクタ層103上に位置し、GaAsよりバンドギャップが広いInGaPから構成されるn型InGaP第2コレクタ層109とを備える。

(もっと読む)

ヘテロ接合バイポーラトランジスタ

【課題】ヘテロバリア効果による高電流動作時でのトランジスタ特性の劣化を抑制した、高性能なSiGe−HBTを提供することにある。

【解決手段】ベース領域4は、エミッタ領域9からコレクタ領域3に向かい、Ge組成比が連続的に減少する第1の領域4aと第2の領域4bを有し、第1の領域4aにおけるGe組成比の減少率が、第2の領域4bにおけるGe組成比の減少率よりも小さくなっている。また、エミッタ領域9に接するベース領域5は、エミッタ領域9からコレクタ領域3に向かいGe組成比が増加している。

(もっと読む)

半導体装置の製造方法

【課題】縦型PNPトランジスタと縦型NPNトランジスタとを備えた半導体装置の製造方法に関し、縦型NPNトランジスタのコレクタ抵抗の増加を抑制する方法を提供する。

【解決手段】縦型PNPトランジスタと縦型NPNトランジスタとを備えた半導体装置の製造方法であって、N型埋め込み拡散層41の形成位置に対応する部分の半導体基板11上に、第1のN型不純物と第1のN型不純物よりも拡散定数の大きい第2のN型不純物とを含有した絶縁膜55を形成し、絶縁膜55が形成された半導体基板11を加熱して、半導体基板11に第1及び第2のN型不純物を拡散させて、N型埋め込み拡散層41を形成した。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】基板の表面をトレンチ構造にしてエミッタ領域及びエミッタ電極を設け、デバイスサイズを小型化、高集積化することができる半導体装置及び該半導体装置の製造方法を提供する。

【解決手段】シリコン基板10は、N型不純物(例えばアンチモンSb)が含有され、コレクタ領域RCを形成している。シリコン基板10の表面には、複数の凹部10a、10a、…を形成している。各凹部10aの底面及び側面には、エミッタ領域REを形成してあり、エミッタ領域REの下側及び各凹部10aを除くシリコン基板10の表面には、ベース領域RBを形成してある。エミッタ領域REにはN型不純物としてのリンが、ベース領域RBにはP型不純物としてのボロンが含有されている。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】基板の表面をトレンチ構造にしてベース領域及びベース電極を設け、デバイスサイズを小型化、高集積化することができる半導体装置及び該半導体装置の製造方法を提供する。

【解決手段】シリコン基板10は、N型不純物として、例えば、アンチモンが含有され、コレクタ領域RCを形成している。シリコン基板10の表面には、複数の凹部10a、10a、…を形成してある。各凹部10aを除くシリコン基板10の表面の一部には、エミッタ領域REが各凹部10aで離隔されるように形成してあり、コレクタ領域RCの上側であって、各凹部10aの底面及び側面、並びにエミッタ領域REの下側には、ベース領域RBを形成してある。エミッタ領域REにはN型不純物としてのリンが、ベース領域RBにはP型不純物としてのボロンが含有されている。

(もっと読む)

半導体装置およびその製造方法

【課題】電流増幅率hFEやコレクタ・エミッタ間の耐圧を、他の半導体素子に影響を与えずに、容易に調整することができる半導体装置及びその製造方法を提供する。

【解決手段】本半導体装置は、第1の導電型不純物を含む半導体基板と、半導体基板上に形成された第2の導電型不純物を含む第1の半導体領域と、第1の半導体領域上に、周囲を第1の導電型不純物を含む第2の半導体領域で囲むように形成された、第2の導電型不純物を含む第3の半導体領域と、第2の半導体領域直下の第1の半導体領域内に形成された、第1の半導体領域より高濃度の第2の導電型不純物を含む埋込半導体領域と、第2の半導体領域及び第1の半導体領域の接合部に形成された、第1の半導体領域より高濃度の第2の導電型不純物を含む介挿半導体層とを有し、第3の半導体領域をエミッタとし、第2の半導体領域をベースとし、埋込半導体領域をコレクタとするバーティカル型バイポーラトランジスタである。

(もっと読む)

半導体装置およびその製造方法

【課題】耐圧性および耐湿性が向上された半導体装置およびその製造方法を提供する。

【解決手段】本発明の半導体装置は、トランジスタ等が形成される活性領域19を囲むように、分離領域13A、13Bを設けている。この分離領域13A等は、半導体基板11の上面から下面まで連続して延在していおり、内部にはシリコン酸化膜等から成る絶縁物層14Aが形成されている。従って、活性領域19が形成される半導体基板11の側面の全てを絶縁物により被覆することができるので、半導体装置の耐圧性および耐湿性を向上させることができる。

(もっと読む)

半導体装置の製造方法

【課題】FZ法およびコレクタ二重拡散法でn−型半導体層/n+型半導体層を形成した基板により半導体装置を製造すると、ドリフト層に遷移領域が形成される。このためコレクタ抵抗の低減には限界があり、装置の薄型化も進まなかった。

【解決手段】FZ法で作成したn−型半導体基板の第1主面に素子領域を形成後、n−型半導体基板を第2主面側から所定の耐圧確保に必要最小限の膜厚付近までバックグラインド研削する。その後、第2主面側に1μm程度の厚みの高濃度不純物層を形成し、ドリフト層とする。これにより遷移領域が形成されず、また従来のn+型半導体層の厚みも大幅に低減できるので、コレクタ抵抗低減によるオン抵抗の低減が実現する。更に生産性も向上でき、装置の薄型化にも寄与できる。

(もっと読む)

半導体装置およびその製造方法

【課題】従来は、コレクタ抵抗の低減およびコレクタ−エミッタ間耐圧の向上の双方を達成することが困難であった。

【解決手段】半導体装置1は、SOI基板10(半導体基板)と、SOI基板10の表層に設けられたコレクタ領域22とコレクタ引上領域26と、コレクタ領域22とコレクタ引上領域26に挟まれて設けられたコレクタ引出領域28と、コレクタ領域22の上にベース領域32を介して設けられ、コレクタ領域22およびベース領域32と共にバイポーラトランジスタを構成するエミッタ領域34と、を備えている。ここで、コレクタ引出領域28は、コレクタ領域22よりも不純物濃度が高い。

(もっと読む)

1 - 20 / 65

[ Back to top ]