Fターム[5F003AP06]の内容

バイポーラトランジスタ (11,930) | 目的 (494) | 二次降伏電圧、安全動作領域改善 (122)

Fターム[5F003AP06]に分類される特許

1 - 20 / 122

半導体装置

【課題】ホールド電圧が高いエミッタ・ベース短絡型の保護素子が設けられた半導体装置を提供する。

【解決手段】半導体装置1は、基板10と、前記基板上に形成された第1導電形の半導体層11と、前記基板と前記半導体層との間に形成された第1導電形の埋込層13と、前記半導体層上に形成された第2導電形のウェル14と、前記半導体層上であって、前記ウェルから離隔し、前記埋込層の直上域に形成された第1導電形の第1コンタクト層15と、前記ウェル上に形成された第2導電形の第2コンタクト層16と、前記ウェル上であって、前記第1コンタクト層と前記第2コンタクト層との間に形成された第1導電形の第3コンタクト層17と、前記埋込層と前記第1コンタクト層との間に形成され、前記第1コンタクト層に接した第1導電形のディープ層18と、を備える。

(もっと読む)

半導体装置

【課題】バイポーラトランジスタの形成領域において半導体層の下部に絶縁層を有する基板が用いられた半導体装置において、バイポーラトランジスタの電流増幅率を向上させる。

【解決手段】バイポーラトランジスタは、半導体層1cに形成されたコレクタ5、ベース7、エミッタ9、ベース用高濃度オーミック拡散層11及びコレクタ用高濃度オーミック拡散層13、並びに半導体層1c上に形成されたゲート絶縁膜15及びゲート電極17を備えている。ベース7は、絶縁層1bに達する深さで形成され、上方から見てゲート電極17と一部重複して形成され、ゲート電極17下でコレクタ5に隣接して形成されている。ベース7は、ベース7側のゲート電極17の端部からコレクタ5側に向かってP型不純物濃度が低くなる濃度傾斜をもっている。

(もっと読む)

半導体素子の製造方法、ESD保護素子の製造方法

【課題】半導体ウエハに厚みばらつきがある前提で、コストアップをすることなく高品質の半導体素子を提供すること。

【解決手段】第1導電型の活性層の下に第1導電型の埋込拡散層を有する半導体基板を準備するステップと、活性層と埋込拡散層の総厚を測定し、測定した総厚から前記活性層の厚さを求めるステップと、活性層に、埋込拡散層との間で電流が流れる第1導電型のコレクタ領域をイオン注入によって形成するステップと、活性層に、埋込拡散層との間で電流が流れる第2導電型のベース領域をイオン注入によって形成するステップと、ベース領域内に、ベース領域との間で電流が流れる第1導電型のエミッタ領域をイオン注入によって形成するステップとを備え、ベース領域を形成するステップは、活性層の厚さに応じてイオン加速エネルギーを変化させるステップであることを特徴とする。

(もっと読む)

ヘテロ接合バイポーラトランジスタ

【課題】GaAsSb系の化合物半導体のベース層を有するInP系HBTにおいて、高周波特性を犠牲にすることなく、さらにオフ耐圧を向上させる。

【解決手段】InPからなる基板101の上に形成された第1コレクタ層102と、この上に形成された第2コレクタ層103と、この上に形成されてGa,As,およびSbから構成された化合物半導体からなるベース層104と、この上に形成されてInおよびPから構成された化合物半導体からなるエミッタ層105とを少なくとも備える。第2コレクタ層103は、第1コレクタ層102およびベース層104に接した状態で、ベース層104の伝導帯端のエネルギー準位よりも低く、第1コレクタ層102の伝導帯端よりも高い伝導帯端のエネルギー準位を有し、ベース層104の価電子帯端のエネルギー準位よりも低い価電子帯端のエネルギー準位を有したものとなっている。

(もっと読む)

電流値依存性の少ない増幅率を有する半導体デバイス

【課題】本発明は、数桁のレベルで変化する電流を、複雑な回路を使わないで一定の増幅率で増幅することを課題とする。

【解決手段】本発明ではこの課題を解決するために、第1導電形の第1半導体領域と、該第1半導体領域に接して設けられた逆導電形の第2半導体領域と、該第2表面で該第2半導体領域と接して設けられた第1導電形の第3半導体領域とを有する半導体デバイスにおいて、該第2半導体と接して該第3半導体領域を離間して囲む該第2半導体領域より高不純物濃度の

第4半導体領域を更に設ける。

(もっと読む)

バイポーラ半導体素子

【課題】表面欠陥の発生を低減できて積層欠陥の発生を抑制でき、オン電圧ドリフトを抑制できるSiCバイポーラ半導体素子を提供する。

【解決手段】このSiC pinダイオード20は、六方晶構造の炭化珪素半導体で作製され、メサ状の半導体層31が六角柱形状で6つの側面(メサ面)31Aをすべて{0m−m0}面(m,nは整数)とした。これにより、メサ面31Aに対する〈11−20〉方向のバーガーズベクトルBV1,BV2の角度θ1,θ2(図4)が、{11−20}面の素子表面(メサ面)に対するバーガーズベクトルBV101,BV102の角度θ101,θ102(図12)に比べて小さくなると共に表面欠陥が発生するのに必要なバーガーズベクトルBV1,BV2の長さが長くなる。これにより、メサ面31Aに表面欠陥SDが入り難くなり、メサ状の半導体層31の各メサ面31Aでの表面欠陥を低減できて、積層欠陥の発生を抑制できる。

(もっと読む)

半導体装置

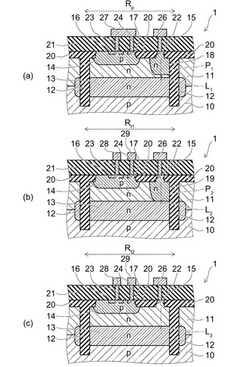

【課題】 放熱性を改善したバイポーラトランジスタを有する半導体装置を提供することにある。

【解決手段】 複数のバイポーラトランジスタQuが配列される半導体装置であって、エミッタ配線L3は幅広部と細長部とを有し、細長部におけるバイポーラトランジスタ素子数が、幅広部が配置された配列の外縁に沿う方向に配列されたバイポーラトランジスタ素子数よりも少なくなるように配置する。

【効果】エミッタ配線の寄生抵抗によるエミッタ−ベース間電圧ばらつきを低減する。

(もっと読む)

半導体装置

【課題】バイポーラトランジスタにおいてオフ耐圧及び破壊電流量の双方を高くする。

【解決手段】第2のベース領域116は、ディープウェル112の表層に形成されており、平面視において第1のベース領域114とシンカー110との間に位置している。そして第2のベース領域116は、第1のベース領域114に接続しており、第1のベース領域116よりも不純物濃度が高く、かつ第1のベース領域116よりも深さが浅い。埋込層108は、半導体層106に形成され、上面がディープウェル112及びシンカー110に接しており、ディープウェル112よりも不純物濃度が高い。

(もっと読む)

半導体装置

【課題】betaの高いラテラル・バイポーラトランジスタを有する半導体装置を提供する。

【解決手段】ラテラル・バイポーラトランジスタとCMOSトランジスタが混載された半導体装置で、ラテラル・バイポーラトランジスタは、素子分離領域20に開口したオープン領域と、オープン領域19上のポリシリコン膜32と、ポリシリコン膜32から活性領域12側面へ不純物拡散したエミッタ拡散層39と、素子分離領域20上のダミー・ゲート・ポリシリコン膜50と、活性領域12上のコレクタ拡散層領域37、ベース拡散層領域27と、コレクタ電極101、ベース電極102、エミッタ電極103と、活性領域12及び前記ポリシリコン膜32上のシリサイド領域42とを備え、活性領域12上の非シリサイド領域が、ベース拡散層領域27とコレクタ拡散層領域37の間の境界領域と、活性領域12と素子分離領域20の間の境界領域を含むことを特徴とする。

(もっと読む)

半導体デバイス

【課題】半導体デバイスにおいて耐圧を高めること。

【解決手段】n型のシリコン基板1と、シリコン基板1の表層に形成されたp型のベース領域2と、ベース領域2の上方に形成され、シリコンよりもバンドギャップが広い半導体材料を含むn型のコレクタ層7aとを有する半導体デバイスによる。

(もっと読む)

半導体装置及びその製造方法

【課題】MOSプロセスへの導入が容易で、エミッタ−ベース間のリーク電流(電界強度)を低減し、ノイズやサージ電圧の影響を受けにくい高性能な半導体装置とその製造方法の提供。

【解決手段】導電膜をマスクとして、2回のイオン注入を行ってエミッタを形成する。第2エミッタ領域111bは、低濃度の不純物イオン注入によって形成し、第1エミッタ領域111aは、高濃度の不純物イオン注入によって形成する。その結果、エミッタの周縁部に低濃度の第2エミッタ領域が形成され、電界が緩和され、リーク電流が低減する。また、導電膜とエミッタ電極116とが接続され、ノイズの影響を受けにくくなる。

(もっと読む)

SiC結晶成長層の製造方法およびバイポーラ型半導体素子

【課題】層厚さが厚くてもSiC結晶中にある炭素空孔を低減できるSiC結晶成長層の製造方法を提供する。

【解決手段】SiC結晶成長層としてのドリフト層23を成長させる工程内に、シリコン原料ガスであるシランと炭素原料ガスであるプロパンのうちのプロパンのみを結晶成長表面に供給する第2の期間を設けている。このことで、結晶成長表面の炭素の過飽和度を上げ、成長途中の表面に過剰な格子間炭素を発生させる。これにより、成長後のSiC結晶成長層としてのドリフト層23の表面から離れている比較的深い箇所での炭素空孔を減少させることができる。

(もっと読む)

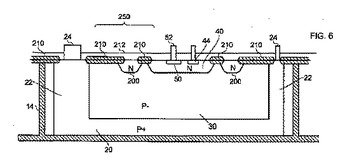

バイポーラトランジスタ

エミッタ領域(50)と、ベース領域(40)と、コレクタ領域(20)と、ベース領域(40)から離間し、それを囲む、保護領域(200)とを備える、バイポーラトランジスタ。保護領域(200)は、ベース領域(40)を形成するために使用される同一ドーピングマスクを使用して形成することができ、動作中には、空乏層を展開する役割を果たすことができる。また、本発明は、上記バイポーラトランジスタを製造する方法であって、エミッタ領域と、ベース領域と、コレクタ領域とを形成することと、該ベース領域を囲む保護領域を形成することとを含む、方法も提供する。  (もっと読む)

(もっと読む)

半導体装置

【課題】バイポーラの高耐圧縦型PNPプロセスをベースにして、寄生PNPトランジスタに起因する漏洩電流の発生しない高耐圧IGBTを形成する。

【手段】P型半導体基板1に、IGBTのコレクタ電極15と電気的に接続するP+型コレクタ層8と、当該P+型コレクタ層8と連続するP+型埋め込み層4と、該P+型埋め込み層4の下層のN型埋め込み層2と、該P+型埋め込み層4と該N型埋め込み層2の間のN+型埋め込み層3とを形成する。また、N+型埋め込み層3の端部と一体となり、前記P型半導体基板1上に形成されたN型エピタキシャル層5の表面まで延在し、コレクタ電極15と電気的に接続されたN+型導電層7を形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】形成する素子に要求される素子間耐圧や素子内部耐圧に応じたディープトレンチ膜を有する半導体装置を提供する。

【解決手段】P型のシリコン基板11上に、N+型埋め込み層12と、N型半導体層13と、が積層された基板10と、基板10にN+型埋め込み層12の形成位置よりも深く形成され、基板10内の素子形成領域内を区画するディープトレンチ20と、ディープトレンチ20の内壁に沿って形成される側壁酸化膜23,24と、ディープトレンチ20内を埋めるTEOS膜を含むディープトレンチ膜26と、ディープトレンチ膜26で区画される素子形成領域に形成されるLDMOSと、を備え、ディープトレンチ20は、N+型埋め込み層12の上面よりも浅い位置の境界深さまでの第1のディープトレンチ21と、境界深さから底部までの第1のディープトレンチ21よりも小さい開口径を有する第2のディープトレンチ22によって構成される。

(もっと読む)

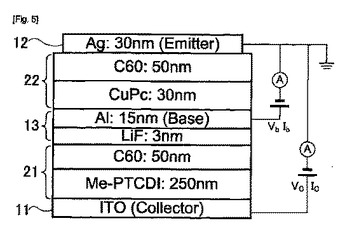

電流増幅型トランジスタ素子及び電流増幅型発光トランジスタ素子

電流増幅型トランジスタ素子には、エミッタ電極とコレクタ電極との間に、有機半導体層が2層とシート状のベース電極とが設けられている。一方の有機半導体層は、エミッタ電極とベース電極との間に設けられた、p型有機半導体層とn型有機半導体層とのダイオード構造を有する。前記電流増幅型トランジスタ素子と、その中に形成された有機EL発光素子部とを含む電流増幅型発光トランジスタ素子も開示されている。  (もっと読む)

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】バイポーラトランジスタが動作する際に、ベース領域のうちコレクタ側の端部が破壊されることを抑制する。

【解決手段】ベース領域150は、ウェル110内に形成されている。エミッタ領域170はベース領域150の中に形成され、ベース領域150より浅い。コレクタ領域140はウェル110内に形成され、ベース領域150の外側に位置している。第1埋込領域180は、少なくとも一部がベース領域150の中に位置しており、ベース領域150よりも不純物濃度が高い。そして第1埋込領域180は、平面視において、エミッタ領域170とコレクタ領域140の間に少なくとも一部が位置している。また第1埋込領域180は、エミッタ領域170の縁のうち少なくとも一辺と重なっており、かつエミッタ領域170の全面には重なっていない。

(もっと読む)

アバランシェ機能を有する高降伏電圧広バンドギャップMOSゲートバイポーラ接合トランジスタ

第1のコレクター、第1のエミッタ、及び第1のベースを有する第1の広バンドギャップバイポーラ接合トランジスタ(BJT)と、第1の広バンドギャップBJTのベースに電流を供給するように構成されたソース領域を有する広バンドギャップMOSFETと、第1のコレクターに電気的に接続された第2のコレクター、第1のエミッタに電気的に接続された第2のエミッタ、及び第1のベースに電気的に接続された第2のベースを有する第2の広バンドギャップBJTとを含む高パワー広バンドギャップMOSFETゲートバイポーラ接合トランジスタ(MGT)を提供する。 (もっと読む)

高利得ワイドバンドギャップ・ダーリントン・トランジスタ及び関連する製造方法

パッケージ化電力電子デバイスが、ベース、コレクタ、及びエミッタ端子を有するワイドバンドギャップ・バイポーラ・ドライバ・トランジスタ(112)と、ベース、コレクタ、及びエミッタ端子を有するワイドバンドギャップ・バイポーラ出力トランジスタ(116)とを含む。出力トランジスタのコレクタ端子は、ドライバ・トランジスタのコレクタ端子に結合され、出力トランジスタのベース端子は、ドライバ・トランジスタのエミッタ端子に結合され、ダーリントン対をもたらす。平面図における出力トランジスタの面積は、ドライバ・トランジスタの面積より少なくとも3倍大きい。例えば、出力トランジスタのドライバ・トランジスタに対する面積比は、約3:1から約5:1までの間とすることができる。関連するデバイス及び製造方法についても説明される。 (もっと読む)

ヘテロ接合バイポーラトランジスタ

【課題】コレクタ層に用いる材料のバンドギャップを大きくし、コレクタ層の膜厚・キャリア濃度を変更せずに高耐圧化を図ることができるヘテロ接合バイポーラトランジスタを提供する。

【解決手段】半絶縁性化合物半導体基板上に、サブコレクタ層、コレクタ層、ベース層、エミッタ層、エミッタコンタクト層、ノンアロイ層が順次形成されてなるヘテロ接合バイポーラトランジスタにおいて、前記エミッタ層はInGaPからなり、前記コレクタ層はAlxGa(1-x)As(0≦x≦1)からなり、さらに前記コレクタ層は、前記サブコレクタ層側から前記ベース層側へxが大きくなるグレーデッド層と、前記グレーデッド層上に形成されるxが一定の定混晶比層とを有するものである。

(もっと読む)

1 - 20 / 122

[ Back to top ]