Fターム[5F003BF06]の内容

バイポーラトランジスタ (11,930) | エミッタ・ベース接合 (716) | JE接合 (461) | ヘテロJE (433)

Fターム[5F003BF06]に分類される特許

421 - 433 / 433

半導体装置の製造方法

濃度1から10%のSiH3CH3をH2により希釈し、希釈したSiH3CH3の一部と、GeH4と、SiH4(またはDCS)とをそれぞれ所定の流量でエピタキシャル装置のチャンバへ供給し、SiGe:Cをエピタキシャル成長技術により形成する。SiH3CH3を希釈することにより、SiH3CH3に含まれる酸素系不純物の濃度が低減するので、チャンバへ供給される酸素系不純物が低減して、成膜されるSiGe:Cに含まれる酸素系不純物の濃度が低減する。 (もっと読む)

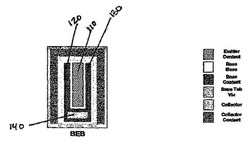

バイポーラ接合トランジスタジオメトリ

【課題】

【解決手段】 バイポーラ接合トランジスタ(100)に関連する方法、装置、デバイスの実施例が記載されている。

(もっと読む)

BICMOSプロセスにおいてシード層トポグラフィを軽減する方法

バイポーラデバイスにおいてエピタキシャルベース層を形成する方法。同方法は:活性シリコン領域(10)に隣接したフィールドアイソレーション酸化物領域(12)を有する構造を提供するステップと;前記フィールドアイソレーション酸化物領域(12)上に窒化シリコン/シリコン積層(14,16)を形成するステップであって、前記窒化シリコン/シリコン積層(14,16)はシリコンの上位層(14)と窒化シリコンの下位層(16)とを含む、前記ステップと;階段状シード層を形成するために前記窒化シリコン/シリコン積層(14,16)にエッチングを実行するステップであって、前記窒化シリコンの下位層がエッチングされると同時に前記シリコンの上位層が横方向にエッチングされる、前記ステップと;前記階段状シード層および活性領域(10)とにわたってSi/SiGe/Si積層(20)を成長させるステップと;含む。  (もっと読む)

(もっと読む)

ひずみ印加半導体デバイス

多数キャリアが正孔であるトランジスタにおいて、少なくとも1つの狭いバンドギャップの領域または層が、p型にドーピングされるかまたは過剰の正孔を含み、かつ機械的圧縮ひずみを受け、これによって、正孔の移動度がかなり増大し得る。pチャネル量子井戸FETでは、量子井戸のInSb井戸のp型層5(変調ドーピングまたは直接ドーピングされている)が、In1−xAlxSb層4と、In1−xAlxSb層6との間にあるが、ここで、xは、軽い正孔および重い正孔が、kTをはるかに超える量だけ分離されるような範囲にまで、層5中にひずみを導入するに十分な値である。pnpバイポーラデバイスを含む、本発明の範囲内にあるトランジスタは、相補型論理回路における電子が多数キャリアである従来の等価物と一緒に用いられ得る。  (もっと読む)

(もっと読む)

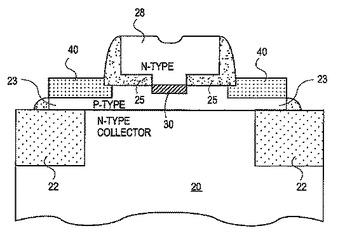

改善された外部ベース領域を備えたバイポーラ接合形トランジスタ及びその製造方法

バイポーラトランジスタ及びその製造方法に関する。第1のエピタキシャル層(23)上への第2の、より高濃度にドープされたエピタキシャル層の成長によって、外部ベース領域(40)が形成される。第2のエピタキシャル層は上にあるポリシリコンエミッタ台座(28)の下まで広がり、かつ、この台座(28)から絶縁される。  (もっと読む)

(もっと読む)

増大した線形性および製造可能性を有するFETを含むBiFET

例示的一実施例によれば、基板上に位置するBiFETは、基板の上に位置するエミッタ層部分を含み、エミッタ層部分は第1のタイプの半導体を含む。HBTはエッチストップ層の第1の部分をさらに含み、エッチストップ層の第1の部分はInGaPを含む。BiFETは基板の上に位置するFETをさらに含み、FETはソース領域およびドレイン領域を含み、エッチストップ層の第2の部分はソース領域およびドレイン領域の下に位置し、エッチストップ層の第2の部分はInGaPを含む。FETはエッチストップ層の第2の部分の下に位置する第2のタイプの半導体層をさらに含む。エッチストップ層はFETの線形性を増大させ、HBTの電子の流れを低下させない。  (もっと読む)

(もっと読む)

選択可能な自己整合性を備えた隆起型外因性ベースを有するバイポーラ・トランジスタ及びその形成方法

【課題】 SiGe真性ベースとエミッタに近接した隆起型外因性ベースとを持つ改良されたバイポーラ・トランジスタを提供する。

【解決手段】 隆起型外因性ベースを持ち、外因性ベースとエミッタ(106)との間の選択可能な自己整合性を備えるバイポーラ・トランジスタが開示される。製造方法は、真性ベース(108)の上に所定の厚さのポリシリコン又はシリコンの第1外因性ベース層(102)を形成するステップを含む。次いで、誘電体のランディング・パッド(128)が、リソグラフィによって第1外因性ベース層(102)の上に形成される。次に、ポリシリコン又はシリコンの第2外因性ベース層(104)が誘電体ランディング・パッド(128)の上に形成され、隆起型外因性ベースの全体の厚さが完成する。エミッタ(106)開口部が、リソグラフィ及びRIEを用いて形成され、その際、第2外因性ベース層(104)は、誘電体ランディング・パッド(128)上でエッチング停止される。エミッタ(106)と隆起型外因性ベースとの間の自己整合性の程度は、第1外因性ベース層(102)の厚さと、誘電体ランディング・パッド(128)の幅と、スペーサの幅とを選択することによって達成される。

(もっと読む)

半導体部品および半導体部品の製造方法

半導体部品は、半導体基板(110)と、半導体基板の上方のエピタキシャル半導体層(120)と、エピタキシャル半導体層内のバイポーラトランジスタ(770、870)と、エピタキシャル半導体層内の電界効果トランジスタ(780、880)とを含む。エピタキシャル半導体層の一部によって、バイポーラトランジスタのベースと電界効果トランジスタのゲートとが形成され、エピタキシャル半導体層のその一部は実質的に均一なドーピング濃度を有する。同じまたは他の実施形態においては、エピタキシャル半導体層の異なる部分によって、バイポーラトランジスタのエミッタと電界効果トランジスタのチャネルとが形成され、エピタキシャル半導体層のその異なる部分はエピタキシャル半導体層の一部の実質的に均一なドーピング濃度と同じかまたは異なる実質的に均一なドーピング濃度を有する。  (もっと読む)

(もっと読む)

半導体素子及び方法

【課題】既に達した速度を潜在的に越えることさえできる極めて高速で動作できるバイポーラトランジスタとその方法を提供することである。

【解決手段】バイポーラトランジスタから制御可能な光放射を生成する方法及び素子が開示されている。また、以下の工程、つまりエミッタ、ベース、及びコレクタ領域を有するバイポーラトランジスタを提供し、電気信号とエミッタ、ベース、及びコレクタ領域を結合する電極を提供し、及び自然放射の不利益に対して誘導放射を強化するためにベース領域を適合させ、それによりベース領域のキャリア再結合寿命を削減する工程を含むバイポーラトランジスタの速度を増大させる方法も開示されている。

(もっと読む)

三次元集積回路構造及びこれを作る方法

垂直方向の半導体装置は、電気装置そして/または相互接続を含む分離して作られた基板に付加される。多くの垂直方向の半導体装置は物理的に互いに分離され、そして同一半導体本体又は半導体基板内には配置されない。多くの垂直方向の半導体装置は取り付けられた後に個別のドープされたスタック構造を生成するため、エッチングされた数個のドーピングされた半導体領域を含む薄い層として分離して作られた基板へ付加される。あるいは多くの垂直方向の半導体装置が分離して作られた基板に取り付けるのに先立ち製作される。ドープされたスタック構造は、ダイオードキャパシタ、n‐MOSFET、p‐MOSFET、バイポーラトランジスタ、及び浮遊ゲートトランジスタのベースを形成する。強誘電体メモリー装置、強磁性体メモリー装置、カルコゲニド位相変更装置が分離して作られた基板と連結して使用するために、堆積可能なアッド‐オン層に形成される。堆積可能なアッド‐オン層は相互接続ラインを含む。

(もっと読む)

(もっと読む)

HBTの製造方法

【課題】 オーバエッチングがべ一ス層まで及ぶことがなく、高速化を図ったHBTの製造方法を提供する。

【解決手段】 コレクタ層とベース層が同じエッチング液でエッチングされる材質で形成されている場合において、

を含んでいる。

(もっと読む)

多層配線基板及び半導体装置

【課題】エミッタ配線からバイアホール、サーマルビアを介して多層配線基板下面につながる放熱経路の熱抵抗を低減し、半導体装置全体の熱抵抗を低減すること。

【解決手段】厚さ方向に貫通孔4を有する多層配線基板3において、多層配線基板3に実装される半導体基板1がその厚さ方向に貫通孔5を有し、かつ、多層配線基板3及び半導体基板1の厚さ方向と直交する平面内において、半導体基板の貫通孔5の占める領域全体が多層配線基板内貫通孔4の占める領域に含まれている多層配線基板。

(もっと読む)

ヘテロバイポーラトランジスタ及びその製造方法

【課題】 信頼性の高い、低電圧動作,高速動作が可能なヘテロバイポーラトランジスタを提供する。

【解決手段】 ドットハッチングを施した領域は、Si層上のSiGeC層における格子歪み量が1.0%以内で、かつバンドギャップが従来の実用的なSiGe(Ge含有率が約10%)のバンドギャップよりも小さくできる領域である。この領域は、Si1-x-y Gex Cy とあらわされるSiGeCにおいて、Geの含有率をx、Cの含有率をyとした場合、4つの直線

421 - 433 / 433

[ Back to top ]