Fターム[5F003BM04]の内容

バイポーラトランジスタ (11,930) | 構成材料 (828) | 2−6族 (12)

Fターム[5F003BM04]に分類される特許

1 - 12 / 12

半導体デバイス

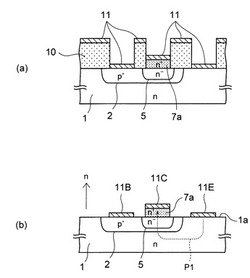

【課題】半導体デバイスにおいて耐圧を高めること。

【解決手段】n型のシリコン基板1と、シリコン基板1の表層に形成されたp型のベース領域2と、ベース領域2の上方に形成され、シリコンよりもバンドギャップが広い半導体材料を含むn型のコレクタ層7aとを有する半導体デバイスによる。

(もっと読む)

大面積ナノ可能マクロエレクトロニクス基板およびその使用

【課題】複数の半導体デバイスを有する電子的な基板を得るための方法および装置。

【解決手段】ナノワイヤ薄膜が、基板上に形成される。ナノワイヤ薄膜は、動作電流レベルを達成するのに十分なナノワイヤの密度を有するように形成される。複数の半導体領域が、ナノワイヤ薄膜に画定される。コンタクトが、半導体デバイス領域において形成され、それによって、電気的な接続を複数の半導体デバイスに提供する。さらに、ナノワイヤを製造するための様々な材料、p型ドーピングナノワイヤおよびn型ドーピングナノワイヤを含む薄膜、ナノワイヤヘテロ構造、発光ナノワイヤヘテロ構造、ナノワイヤを基板上に配置するためのフローマスク、ナノワイヤを成膜するためのナノワイヤ噴霧技術、ナノワイヤにおける電子のフォノン散乱を減少または除去するための技術、および、ナノワイヤにおける表面準位を減少させるための技術が、説明される。

(もっと読む)

半導体基板、電子デバイス、半導体基板の製造方法及び電子デバイスの製造方法

【課題】半導体基板、電子デバイス、半導体基板の製造方法及び電子デバイスの製造方法を提供する。

【解決手段】シリコンに不純物原子が導入された不純物領域104を有するベース基板102と、不純物領域104に接して設けられている複数のシード体112と、複数のシード体112の各々に接して設けられ、複数のシード体112の各々とそれぞれ格子整合または擬格子整合する複数の化合物半導体114とを備える半導体基板100。当該半導体基板100は、ベース基板102上に設けられ、不純物領域104の少なくとも一部を露出する複数の開口が設けられた阻害体をさらに備えてもよい。

(もっと読む)

トランジスタ素子およびその製造方法

【課題】

ベース電極とコレクタ半導体の電荷注入障壁の制御が可能である、高性能な縦型薄膜のトランジスタ素子および製造方法を提供する。

【解決手段】

基板10上に、第一電極20と、コレクタ半導体層30と、ベース電極40と、エミッタ半導体層31と、第二電極21とを順次積層するトランジスタ素子において、コレクタ半導体層とエミッタ半導体層の間にベース電極が存在するようにするとともに、コレクタ半導体層が金属酸化物よりなることを特徴とする。

(もっと読む)

高周波デバイスの誘電体突出部

(例えばシリコン)バイポーラデバイス(40、100、100’)の高周波性能は、外部ベースコンタクト(46)とコレクタ(44、44’、44”)との間の容量結合(Cbc)の低減により向上される。外部ベースコンタクト(46)をコレクタ(44、44’、44”)の外周部(441)から隔てるように、製造中に誘電体突出部(453、453’)が作製される。誘電体突出部(453、453’)は、外部ベースコンタクト(46)を真性ベース(472)に結合するトランジション領域(461)の下に位置する。デバイス製造中に、多層誘電体スタック(45)が真性ベース(472)に隣接して形成され、真性ベース(472)から外部ベースコンタクト(46)へのトランジション領域(461)を形成可能なアンダーカット領域(457、457’)の同時作製が可能にされる。キャビティ(457、457’)内に形成されたトランジション領域(461)が、それをコレクタ(44、44’、44”)の外周部(441)から隔てる誘電体突出部(453、453’)の上に位置することで、ベース−コレクタ接合容量(Cbc)が低減される。デバイスのfMAXが有意に上昇される。  (もっと読む)

(もっと読む)

半導体を用いた電子デバイス

【課題】高耐圧電子デバイスおよび耐環境電子デバイスを提供する。

【解決手段】本発明においては、ダイオードやトランジスタ等の電子デバイス中で電子が走行する領域に、高純度の酸化モリブデンであって、その禁制帯幅が3.45eV以上であるような酸化モリブデンが用いられる。本発明によれば、高耐圧特性および高耐環境特性を有する電子デバイスが実現できる。

(もっと読む)

ナノスケールワイヤ及び関連デバイス

【課題】

ナノテクノロジー、特にナノスケールでのエレクトロニクス用途に適したナノスケールワイヤ及び関連デバイスをを提供することを目的とする。

【解決手段】

少なくとも1012バイト/cm2の密度をもつメモリ素子のアレイを含み、

少なくともひとつのメモリ素子は、自立型バルクドープ半導体を含む物品を含み、該自立型バルクドープ半導体は、500ナノメートル未満の最小幅をもつ少なくとも一つの部分

を含む、

デバイスを使用する。

(もっと読む)

トランジスタ素子

【課題】 縦型の薄膜電流注入型トランジスタにおいて、通常の空気雰囲気で高い電流増倍率と高い電流密度を安定して制御できるトランジスタ素子を提供することを目的とする。

【解決手段】 本発明は、第1電極と第2電極の間に第1半導体層、第3電極、第2半導体層を配し、前記第3電極から注入される電流によって前記第1電極から前記第2電極に流れる電流を制御するトランジスタ素子であって、前記第3電極が金属微粒子を構成要素として含む。また、前記第1半導体層が酸化亜鉛、前記第2半導体層が、酸化インジウム、酸化錫、酸化カドミミウムの少なくともいずれか1つを主成分とし、前記第1電極から前記第2電極に流れる電流が主として電子によるものである。

(もっと読む)

半導体装置

【課題】 本願発明は、高利得で高速動作に適したバイポーラトランジスタを提供するものである。より具体的な技術的な側面では、本願発明はトランジスタを微細化した際に、高利得と高速性を実現できるバイポーラトランジスタを提供することにある。

【解決手段】 本願発明は、ベース領域の側面に、ベース領域よりバンドギャップが広い外部ベース領域を設けた構造を有する。ベース領域はシリコン・ゲルマニウムが代表例である。

(もっと読む)

個別電子コンポーネントのマトリクスを形成する方法および形成されるマトリクス

本発明は、基板(100)上にアクティブ層(101)を形成する段階および少なくとも基板(100)が出現するまで、トレンチ(102)をアクティブ層(101)内に形成することでコンポーネントを個別化する段階を含む、電子コンポーネント(111)のマトリクスを製造する方法に関する。この方法は、アクティブ層(101)上に機能材料の層(102)を蒸着する段階と、前記トレンチ(102)を充填し、電子コンポーネント(111)の上側面に薄膜(115)を形成するように、材料の層(103)上に感光性樹脂(104)を蒸着する段階と、トレンチの樹脂の部分の露光を少なくしつつ樹脂(104)を放射線に少なくとも部分的に曝露する段階と、適切に露光された部分を除去するように樹脂(104)を現像する段階と、現像段階の後、外面に現われる機能材料の層(103)の部分を除去する段階と、樹脂の残り部分を除去する段階とを含む。  (もっと読む)

(もっと読む)

ヒューズ素子及びヒューズ素子を備えた半導体装置並びに半導体装置の製造方法

【課題】より低い電圧の印加によって溶断可能であって、しかも溶断に要する熱量を低減可能なヒューズ素子、及びヒューズ素子を備えた半導体装置、並びに半導体装置の製造方法を提供する。

【解決手段】ヒューズ素子は、半導体基板上に少なくともシリコンと、このシリコンよりも融点が低い元素とで形成した導電層と、この導電層の上面に形成した金属シリサイド層とで形成する。シリコンよりも融点が低い元素はゲルマニウムとする。特に、半導体基板には、上面に金属シリサイド層を設けたシリコン−ゲルマニウム層からなるベース引き出し電極を備えたバイポーラトランジスタが形成されており、導電層はバイポーラトランジスタにおけるシリコン−ゲルマニウム層の形成にともなってヒューズ素子部分に形成されたシリコン−ゲルマニウム層で形成する。

(もっと読む)

バイポーラ接合トランジスタおよびその形成方法

【課題】バイポーラ接合トランジスタ(BJT)を提供すること。

【解決手段】各BJTのコレクタ領域は、半導体基板表面内に配置され、第1のシャロー・トレンチ・アイソレーション(STI)領域に隣接している。第2のSTI領域が形成され、この第2のSTI領域は、第1のSTI領域とコレクタ領域との間に延在し、約90°以下のアンダーカット角度で活性ベース領域の一部をアンダーカットする。例えば、第2のSTI領域は、約90°未満のアンダーカット角度のほぼ三角形の断面を有していても、約90°のアンダーカット角度のほぼ長方形の断面を有していてもよい。このような第2のSTI領域は、コレクタ領域の上側表面内に形成される多孔質表面部を使用して製作することができる。

(もっと読む)

1 - 12 / 12

[ Back to top ]