Fターム[5F003BP05]の内容

バイポーラトランジスタ (11,930) | 製法 (1,830) | 拡散 (273) | 拡散源 (104)

Fターム[5F003BP05]の下位に属するFターム

Fターム[5F003BP05]に分類される特許

1 - 18 / 18

半導体装置及びその製造方法

【課題】バーティカル型のバイポーラトランジスタにおいて、エミッタ領域からベース領域にかけて存在する界面準位を安定に低減することを可能とした半導体装置とその製造方法を提供する。

【解決手段】バーティカル型のバイポーラトランジスタ10は、シリコン基板1に形成されたP型のベース領域13と、シリコン基板1に形成されてベース領域13に接するエミッタ領域15と、シリコン基板1の表面であってベース領域13とエミッタ領域15との境界部21上に形成されたシリコン酸化膜17と、シリコン酸化膜17上に形成されたポリシリコンパターン19と、を有する。シリコン酸化膜17とシリコン基板1との界面に塩素が1×1017cm−3以上の濃度で存在する。

(もっと読む)

半導体装置およびその製造方法

【課題】InP系の微細構造デバイスをより効果的に冷却できるようにする。

【解決手段】主表面を(001)面としたInPからなる基板101の上にInGaAsからなるバッファ層102を形成し、バッファ層102の上に接して配置されたInPの層を含んでバッファ層102の上に形成されたデバイス103を形成し、デバイス103の周囲のバッファ層102を露出させた状態でデバイス103を覆う保護層104を形成し、露出したバッファ層102の上に金を堆積して金層105を形成し、次に、バッファ層102の表面に接触している金層105よりデバイス103の下部のバッファ層102に金を拡散させる。

(もっと読む)

半導体装置

【課題】betaの高いラテラル・バイポーラトランジスタを有する半導体装置を提供する。

【解決手段】ラテラル・バイポーラトランジスタとCMOSトランジスタが混載された半導体装置で、ラテラル・バイポーラトランジスタは、素子分離領域20に開口したオープン領域と、オープン領域19上のポリシリコン膜32と、ポリシリコン膜32から活性領域12側面へ不純物拡散したエミッタ拡散層39と、素子分離領域20上のダミー・ゲート・ポリシリコン膜50と、活性領域12上のコレクタ拡散層領域37、ベース拡散層領域27と、コレクタ電極101、ベース電極102、エミッタ電極103と、活性領域12及び前記ポリシリコン膜32上のシリサイド領域42とを備え、活性領域12上の非シリサイド領域が、ベース拡散層領域27とコレクタ拡散層領域37の間の境界領域と、活性領域12と素子分離領域20の間の境界領域を含むことを特徴とする。

(もっと読む)

半導体装置

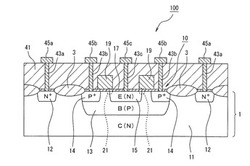

【課題】バイポーラの高耐圧縦型PNPプロセスをベースにして、寄生PNPトランジスタに起因する漏洩電流の発生しない高耐圧IGBTを形成する。

【手段】P型半導体基板1に、IGBTのコレクタ電極15と電気的に接続するP+型コレクタ層8と、当該P+型コレクタ層8と連続するP+型埋め込み層4と、該P+型埋め込み層4の下層のN型埋め込み層2と、該P+型埋め込み層4と該N型埋め込み層2の間のN+型埋め込み層3とを形成する。また、N+型埋め込み層3の端部と一体となり、前記P型半導体基板1上に形成されたN型エピタキシャル層5の表面まで延在し、コレクタ電極15と電気的に接続されたN+型導電層7を形成する。

(もっと読む)

半導体装置、半導体装置の製造方法

【課題】 p型不純物が隣接する半導体結晶層中へ拡散することを抑え、ひいては良好で安定した特性を持つ半導体装置を提供する。

【解決手段】 P−InP基板401と、P−InP基板401に格子整合し、かつ、p型の不純物が注入されたp−ZnドープInPバッファ層402と、p−ZnドープInPバッファ層402よりも上層にあって、P−InP基板401に格子整合し、かつ、p型不純物、n型不純物のいずれか一方を含むn−SiドープInPクラッド層404、n−SiドープInGaAsキャップ層405と、を備え、n−SiドープInPクラッド層404、n−SiドープInGaAsキャップ層405に、Sbを含ませる。

(もっと読む)

接合の作製方法

【課題】バイポーラトランジスタのエミッタ−ベース界面において、ドーパント濃度プロファイルを制御する方法を提供する。

【解決手段】第1濃度を有する第1ドーパントを含む第1半導体材料を形成する工程と、その上に、第2濃度を有し、これにより接合を形成する、第2ドーパントを含む第2半導体材料を形成する工程と、第2半導体材料を形成する前に、原子層エピタキシまたは気相ドーピングにより、第1半導体材料の上に、第2ドーパントを形成するのに適した、単分子層の少なくとも一部分の前駆体を堆積し、これにより接合における第2ドーパントの第2濃度を増加させる工程と、を含む(またはこれらの工程からなる)。

(もっと読む)

BiCDMOS構造及びその製造方法

【課題】DMOS電力回路、CMOSデジタル論理回路、及びコンプリメンタリバイポーラアナログ回路の全てを単一の集積化された回路チップ上に実現するBiCDMOS構造及びその製造方法を提供する。

【解決手段】基層10内に下向きに延出し、且つ基層の上に配置されたエピタキシャル層40内に上向きに延出し、かつエピタキシャル層の上側主面の下に配置された埋め込み絶縁領域21Bと、エピタキシャル層内のみに配置され、かつ埋め込み絶縁領域の上側主面から上向きに延出した埋め込みウェル領域44Bと、エピタキシャル層内に配置され、かつエピタキシャル層の上側主面からエピタキシャル層内に下向きに延出し、かつ埋め込みウェル領域の上側主面に接触する下側主面を備えたウェル領域51Bとを有し、バイポーラトランジスタがウェル領域内に形成され、MOSトランジスタがウェル領域外のエピタキシャル層の上側主面に形成される。

(もっと読む)

半導体装置の製造方法

【課題】微細加工が求められる半導体装置であるBiCMOSの製造方法に関し、特に半導体基板上に形成されるエピタキシャル層の表面の平坦性を向上することを課題とする。

【解決手段】本発明のBiCMOSの製造方法は、P型シリコン基板1の主面をエッチングしてくぼみ部32を形成する第1工程と、くぼみ部32を被覆するシリコン酸化膜22をマスクにして当該P型シリコン基板1にN+型埋め込み層2を形成する第2工程と、N+型埋め込み層2を含むP型シリコン基板1の主面を熱酸化して、P型シリコン基板1上にシリコン酸化膜22を含むシリコン熱酸化膜25を形成する第3工程と、シリコン熱酸化膜25を除去した後、N+型埋め込み層2を含むP型シリコン基板1の主面上にN型エピタキシャル層を形成する第4工程と、を含む。

(もっと読む)

半導体装置の製造方法

【課題】工程数を増加させることなく高速バイポーラトランジスタと高耐圧バイポーラトランジスタを同一半導体基板上に形成し、高耐圧バイポーラトランジスタを使用する回路の歪特性を低減できる半導体装置の製造方法の提供。

【解決手段】半導体基板101上に、コレクタの一部となる埋込み領域102を、第1、第2のバイポーラトランジスタの形成領域に同一工程で形成し、エピタキシャル層104を形成し、第1の縦型バイポーラトランジスタの形成領域においては、埋込み領域102をベース形成領域の全体に形成し、第2の縦型バイポーラトランジスタの形成領域においては、埋込み領域102をベース形成領域の1箇所に埋込み領域を形成しない領域を有して形成する。第2の縦型バイポーラトランジスタの埋込み領域を形成しない領域では、周囲からの不純物の拡散により、縦方向の拡散拡がり量が連続的に狭くなり、埋込み領域を形成しない領域が形成される。

(もっと読む)

半導体装置及びその製造方法

【課題】従来の半導体装置では、ISOを構成するP型の埋込層の横方向拡散幅が広がる等により、ISOの形成領域が狭め難いという問題があった。

【解決手段】本発明の半導体装置では、P型の基板6上に2層のEPI7、8が形成される。基板6及びEPI7、8には、ISO1、2、3が形成され、複数のアイランドに区分される。ISO1は、L−ISO9、M−ISO10及びU−ISO11が連結し、形成される。そして、L−ISO9とU−ISO11との間にM−ISO10が配置され、L−ISO9の横方向拡散幅W1が狭められる。この構造により、ISO1の形成領域が狭められる。

(もっと読む)

半導体装置及びその製造方法

【課題】従来の半導体装置では、コレクタ領域が拡散層により形成され、横方向拡散によりデバイスサイズが縮小し難いという問題があった。

【解決手段】本発明の半導体装置では、P型の単結晶シリコン基板2上にN型のエピタキシャル層3が形成されている。コレクタ領域としてのN型の埋め込み拡散層6が基板2とエピタキシャル層3に渡り形成されている。エピタキシャル層4には、N型の埋め込み拡散層6に達するトレンチ9が形成されている。トレンチ9は、N型不純物が導入されたポリシリコン16により埋設されている。この構造により、NPNトランジスタ1では、コレクタ領域でのシート抵抗値が低減され、デバイスサイズが縮小される。

(もっと読む)

半導体装置及びその製造方法

【課題】従来の半導体装置、例えば、横型PNPトランジスタでは、耐圧特性を維持しつつ、また、デバイスサイズを増大させることなく、所望の電流増幅率を得ることが難しいという問題があった。

【解決手段】本発明の半導体装置では、P型の単結晶シリコン基板3上にN型のエピタキシャル層4が形成されている。横型PNPトランジスタ1では、エピタキシャル層4はベース領域として用いられる。そして、基板3及びエピタキシャル層4には、モリブデン(Mo)が拡散されている。この構造により、ベース電流値が調整され、横型PNPトランジスタ1の所望の電流増幅率(hFE)を実現することができる。

(もっと読む)

半導体装置の製造方法

【課題】縦型PNPトランジスタと縦型NPNトランジスタとを備えた半導体装置の製造方法に関し、縦型NPNトランジスタのコレクタ抵抗の増加を抑制する方法を提供する。

【解決手段】縦型PNPトランジスタと縦型NPNトランジスタとを備えた半導体装置の製造方法であって、N型埋め込み拡散層41の形成位置に対応する部分の半導体基板11上に、第1のN型不純物と第1のN型不純物よりも拡散定数の大きい第2のN型不純物とを含有した絶縁膜55を形成し、絶縁膜55が形成された半導体基板11を加熱して、半導体基板11に第1及び第2のN型不純物を拡散させて、N型埋め込み拡散層41を形成した。

(もっと読む)

半導体装置の製造方法

【課題】P+層を形成する時にステッパーマスクを用いることなく、約2.0μmの幅を有するP+層を、約2.5μmの幅を有するP−層の外縁よりも内側に配置する

【解決手段】P−層5上にP+層7を配置する工程を含む半導体装置の製造方法において、P−層5を形成する時に用いられた酸化膜3の開口3aと同じものをP+層7を形成する時に用い、P−層5を形成するための熱処理よりも、P+層7を形成するための熱処理を弱くした。好ましくは、P−層5を形成する時に用いられた酸化膜3の開口3aに形成された新たな酸化膜3bに対してリンデポジションを行う工程を、P+層7を形成する工程の前に設けた。

(もっと読む)

半導体装置およびその製造方法

【課題】NPNトランジスタ等のバイポーラリニア素子とIIL素子とを同一の半導体基板上に備えた半導体装置であって、高耐圧であるとともに、動作特性の優れたIIL素子を有するものを提供すること。

【解決手段】IIL素子に含まれたマルチコレクタ型NPNトランジスタTr1は、半導体基板101の裏面側から表面側へ向かう縦方向に順にN型エミッタ層Tr1E、P型ベース層Tr1B、N型コレクタ層Tr1Cを備える。マルチコレクタ型NPNトランジスタのP型ベース層Tr1Bは、エミッタ層Tr1E側で高く、かつコレクタ層Tr1C側で低くなるように傾斜した不純物濃度プロファイルを持つ。

(もっと読む)

半導体装置及びその製造方法

【課題】従来の半導体装置では、パワー用半導体素子の耐圧特性と制御用半導体素子のデバイスサイズの縮小化とを実現することが難しいという問題があった。

【解決手段】本発明の半導体装置では、P型の単結晶シリコン基板3上にN型のエピタキシャル層4が形成されている。基板3にはP型の埋込拡散層6が形成され、基板3とエピタキシャル層4には、N型の埋込拡散層10がP型の埋込拡散層7上に形成されている。この構造により、P型の埋込拡散層7の這い上がりが抑制され、パワー用半導体素子の耐圧特性を維持しつつ、エピタキシャル層4の厚みを薄くすることができる。そして、制御用半導体素子のデバイスサイズを縮小化することができる。

(もっと読む)

マルチコレクタ型ラテラルPNPトランジスタおよびその製造方法、カレントミラー定電流回路並びに半導体装置

【課題】 コレクタ電流比の精度を高めることができるマルチコレクタ型ラテラルPNPトランジスタを提供すること。

【解決手段】 層状に設けられたベース領域3と、ベース領域3の表面に閉領域をなすパターンで形成されたエミッタ領域5とを備える。ベース領域3の表面のうちエミッタ領域5から離間した位置に、エミッタ領域5に対して対称なパターンで互いに離間して形成された少なくとも一対のコレクタ領域6A,6Bを備える。各領域3,5,6A,6Bを覆う絶縁膜を備える。その絶縁膜は少なくともエミッタ領域5に対応した位置にエミッタ電極配線接続用のコンタクト窓19を有する。そのコンタクト窓19のパターン寸法W2は、エミッタ領域5のパターン寸法W1に対して1/2以下である。

(もっと読む)

自己整合エピタキシャル成長バイポーラ・トランジスタ

照明システムは、複数個の発光素子(R、G、B)を含む光源(1)を有する。これらの発光素子は、少なくとも第1の原色の第1の発光ダイオードと、少なくとも第2の原色の第2の発光ダイオードとを備え、第1と第2の原色がお互いに異なっている。この照明システムは、発光素子によって発せられた光を平行にするためのファセット光コリメータ(2)を有する。このファセット光コリメータは、照明システムの長手方向軸(25)に沿って構成される。ファセット光コリメータ内の光伝搬は、全内部反射に、又はファセット光コリメータのファセット上に施された反射コーティングでの反射に基づいている。ファセット光コリメータは、光源から離れて面する側で、ファセット光反射板に組み合わせる。この照明システムは、光整形拡散体(17)を更に備える。この照明システムは、均一な空間の及び空間角度色分散で光を発する。  (もっと読む)

(もっと読む)

1 - 18 / 18

[ Back to top ]