Fターム[5F003BP06]の内容

バイポーラトランジスタ (11,930) | 製法 (1,830) | 拡散 (273) | 拡散源 (104) | 多結晶 (63)

Fターム[5F003BP06]に分類される特許

1 - 20 / 63

半導体装置及び半導体装置の製造方法

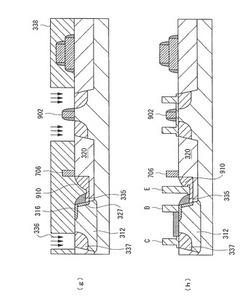

【課題】ラテラル・バイポーラトランジスタを有する半導体装置であって、エミッタポリシリコンに対する良好なコンタクトを得ることができる半導体装置及びその半導体装置の製造方法を提供する。

【解決手段】ラテラル・バイポーラトランジスタを有する半導体装置であって、ラテラル・バイポーラトランジスタは、第1の導電層を構成する基板と、第1の導電層上に配置されたn−hill層312と、n−hill層312を囲む素子分離酸化膜320に開口されたオープン領域と、オープン領域上に形成されるポリシリコン膜910と、ポリシリコン膜910から固相拡散されたエミッタ領域と、素子分離酸化膜320に形成されたダミーゲートポリシリコン706と、を有し、ダミーゲートポリシリコン706によってポリシリコン膜910からの固相拡散されるエミッタ領域の形状が制御される。

(もっと読む)

半導体装置

【課題】ラテラル・バイポーラトランジスタを有する半導体装置であって、エミッタ、コレクタ間の耐圧をより高めることができる半導体装置を提供する。

【解決手段】HCBT100は、第1の導電層を構成する基板1と、n−hill層11と、素子分離酸化膜6とを備え、n−hill層11は第2の導電層と第3の導電層を含み、第3の導電層は第4の導電層を含み、第4の導電層はエミッタ電極31Aと接続し、コレクタ電極31Bをさらに備え、n−hill層11はコレクタ電極31Bと電気的に接続し、少なくとも2つのコレクタ電極31Bを備え、n−hill層11はコレクタ電極31Bと電気的に接続し、少なくとも2つのコレクタ電極31Bは、コレクタ電極31B同士を結ぶ直線と、n−hill層11に備わる少なくとも一つの側面の2つの対向する位置を結ぶ直線とが直交する位置にあることを特徴とする。

(もっと読む)

半導体装置の製造方法

【課題】良好な電気特性を有する半導体装置の製造方法を提供する。

【解決手段】電極層の上に希土類金属シリサイド膜とアモルファスシリコン膜とを形成し、希土類金属シリサイド膜とアモルファスシリコン膜とをマイクロ波を用いて加熱することにより、希土類金属シリサイド膜の結晶構造に応じた結晶配向を持つように、アモルファスシリコン膜を結晶化させる。

(もっと読む)

半導体装置

【課題】betaの高いラテラル・バイポーラトランジスタを有する半導体装置を提供する。

【解決手段】ラテラル・バイポーラトランジスタとCMOSトランジスタが混載された半導体装置で、ラテラル・バイポーラトランジスタは、素子分離領域20に開口したオープン領域と、オープン領域19上のポリシリコン膜32と、ポリシリコン膜32から活性領域12側面へ不純物拡散したエミッタ拡散層39と、素子分離領域20上のダミー・ゲート・ポリシリコン膜50と、活性領域12上のコレクタ拡散層領域37、ベース拡散層領域27と、コレクタ電極101、ベース電極102、エミッタ電極103と、活性領域12及び前記ポリシリコン膜32上のシリサイド領域42とを備え、活性領域12上の非シリサイド領域が、ベース拡散層領域27とコレクタ拡散層領域37の間の境界領域と、活性領域12と素子分離領域20の間の境界領域を含むことを特徴とする。

(もっと読む)

半導体装置及びその製造方法

【課題】結晶欠陥による接合リークを防止しながら、バイポーラトランジスタの面積を縮小し、コレクタ容量の低減によってトランジスタ特性を向上できるようにした半導体装置及びその製造方法を提供する。

【解決手段】活性領域1からSTI4上にかけて連続して形成したSiGe膜は、半導体基板3上ではSiGeエピ膜6となり、STI4上ではSiGeポリ膜7となる。半導体基板3とSTI4の境界はSiGe−HBT形成工程以前の洗浄工程によって段差15が生じており、SiGeエピ膜6及び半導体基板3には、上記境界を基点とした結晶欠陥が応力によって発生する可能性がある。この境界に第1のP型不純物層8及び第2のP型不純物層9を設けることで、結晶欠陥をこれらP型不純物層8、9に内包し、接合リークの発生を抑制する。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】寄生容量を低減しつつ、トランジスタが形成される半導体層に歪応力を与える。

【解決手段】半導体層3に形成されたコレクタ層3aの表面および裏面にストレス印加層5を形成し、ストレス印加層5を介して埋め込み絶縁層6上に配置されたベース層9をコレクタ層3aの側壁に選択的に形成し、ベース層9の側壁を絶縁膜10から露出させる開口部12を形成し、開口部12を介してベース層9の側壁に接続されたエミッタ層13aを埋め込み絶縁層6上に形成する。

(もっと読む)

バイポーラトランジスタ及びその製造方法

【課題】バイポーラトランジスタの高周波特性の向上を図る。

【解決手段】p型シリコン基板10上に形成されたn型導電型の第1コレクタ層14と、第1コレクタ層14上に形成された、第1コレクタ層14より幅の狭い、n型導電型の第2コレクタ層21と、第1コレクタ層14上に、第2コレクタ層21側面に接して形成された絶縁膜層20と、第2コレクタ層21上に形成された、p型導電型のベース層22と、ベース層22側面に接してに形成された、p型導電型のベース引き出し層25と、ベース層22上に形成された、n型導電型のエミッタ領域32とを備える。第1コレクタ層14とベース層22の間、又は第1コレクタ層14とベース引き出し層25の間に、絶縁膜層20が形成されていることにより、ベース・コレクタ間の接合容量を低減させる。

(もっと読む)

バイポーラトランジスタの製造方法及びバイポーラトランジスタ

【課題】バイポーラトランジスタの高周波特性を向上させる。

【解決手段】ヘテロバイポーラトランジスタ70は、ベースとエミッタ、ベースとコレクタがヘテロ接合を有し、双条ベース構造を有する。N型エピタキシャル層3上の内部ベース層(P型SiGe層)5と接する外部ベース層10、及び内部ベース層(P型SiGe層)5上には、絶縁膜7及びN型多結晶シリコン膜8が積層形成される。積層形成された絶縁膜7及びN型多結晶シリコン膜8の中央部にはエミッタ開口部19が設けられる。エミッタ開口部19にはN型エピタキシャル層11が設けられる。N型エピタキシャル層11及びN型多結晶シリコン膜8上には、エミッタ開口部19を覆うようにT型形状を有するN型多結晶シリコン膜12が設けられる。左右のN型多結晶シリコン膜8及びエミッタ開口領域は同時に形成され、左右のN型多結晶シリコン膜8の幅は同一に設定される。

(もっと読む)

半導体装置

【課題】SiGe混晶層を有する半導体装置において、高い高周波特性と安定した低いベースコンタクト抵抗とを得られるようにする。

【解決手段】半導体装置は、N型のコレクタ層1aと、コレクタ層1aの上に形成され、P型SiGe層3bを含む真性ベース層となるSiGeエピ膜3と、SiGeエピ膜3の周囲に形成され、P型の多結晶シリコン層及びP型の多結晶シリコンゲルマニウム層を含むベース引き出し電極4と、SiGeエピ膜3の上部に形成されたN型のエミッタ層8とを有している。真性ベース層の上部には、Si−Cap層3cが形成されており、エミッタ層8は、Si−Cap層3cの上部に形成された上部エミッタ領域8bと、該上部エミッタ領域8bの下側に該上部エミッタ領域8bと接して形成された下部エミッタ領域8aとにより構成されている。

(もっと読む)

半導体装置、半導体装置の製造方法及びパワーアンプ素子

【課題】ウェハー上面側から基板までの電流経路を低抵抗にできる半導体装置およびその製造方法を提供する。

【解決手段】第一導電型高濃度半導体基板101と、第一導電型高濃度半導体基板101上に設けられた低濃度不純物エピタキシャル層103と、105とを含み、第一導電型高濃度半導体基板101に接続するトレンチ110が低濃度不純物エピタキシャル層103、105に設けられている半導体装置であって、トレンチ110の内壁に沿って少なくとも低濃度不純物エピタキシャル層103、105中に形成されるとともに、第一導電型高濃度半導体基板101に接続する、第一導電型高濃度半導体基板101と同一導電型の第一導電型高濃度不純物領域112と、第一導電型高濃度不純物領域112上に形成されたコンタクト111とを含む、半導体装置を提供する。

(もっと読む)

半導体装置およびその製造方法

【課題】バイポーラトランジスタの耐圧の確保と電流増幅率hFEの向上とが容易な半導体装置およびその製造方法を提供する。

【解決手段】SOI基板のSOI層SLにバイポーラトランジスタBTと、nMOSトランジスタNTと、pMOSトランジスタPTとが形成されている。バイポーラトランジスタBTのコレクタ領域CLのn-領域CLLは、SOI層SLの厚み方向に対してpMOSトランジスタPTのn-チャネル形成領域NCと同じ不純物濃度分布を有している。バイポーラトランジスタBTのベース領域BAは、pMOSトランジスタPTのn-チャネル形成領域NCのn型の不純物濃度よりも高いp型の不純物濃度を有している。

(もっと読む)

半導体装置

【課題】バイポーラトランジスタの周りで電位変動が発生した場合であっても、該電位変動の影響を受け難く、耐圧等の他の特性と両立できる、安価な半導体装置を提供する。

【解決手段】埋め込み酸化膜12上のSOI層13に、埋め込み酸化膜12に達する絶縁トレンチ17が形成され、該絶縁トレンチ17により取り囲まれたSOI層13からなる第1絶縁分離領域Z1に、バイポーラトランジスタTr1が形成されてなる半導体装置100であって、第1絶縁分離領域Z1を取り囲む絶縁トレンチ17の外側のフィールド領域Fが、バイポーラトランジスタTr1に印加される最高電位Vmaxと同じ電位に設定されてなる半導体装置100とする。

(もっと読む)

半導体装置の製造方法

【課題】不純物を拡散させる熱処理を低温化・短時間化し、かつ、良品率を向上させること。

【解決手段】親水性膜19を成膜するステップと、親水性膜19の開口部22により露出する基板表面25を親水性膜19とともに薬液で処理するステップと、基板表面25に隣接するように成膜されたポリシリコン膜32に注入された不純物をポリシリコン膜32から基板8に拡散させるステップとを備えている。このとき、半導体装置は、基板表面25が薬液で処理されることにより、基板8とポリシリコン膜32との界面に膜が形成されることが防止され、ポリシリコン膜32から基板8に不純物を拡散させる熱処理を低温化し、または、短時間化することができる。さらに、半導体装置は、薬液で処理されるときに用いられた液体が親水性膜19の表面に残ることが防止され、ウォーターマークが生成されることが防止され、パターン異常の発生が防止される。

(もっと読む)

半導体装置およびその製造方法

【課題】電流リーク及び寄生抵抗が抑制され、安定した電流利得を実現する半導体装置を提供する。

【解決手段】n型コレクタ層102上に、第一の半導体層110を成長させつつ、p型多結晶シリコン膜106、シリコン窒化膜108を含む積層膜からなる庇部の下面に露出したp型多結晶シリコン膜106の下方に第一の多結晶半導体層120を成長させ、その後第一の多結晶半導体層120を選択的に除去する。さらに第二の半導体層112、114、第三の半導体層116を成長させつつ、庇部の下面に露出したp型多結晶シリコン膜106の下方に第二の多結晶半導体層122、124、第三の多結晶半導体層126を、シリコン窒化膜108に接触しないように選択的に成長させ、第三の半導体層と、第三の多結晶半導体層を接触させる。

(もっと読む)

半導体装置の製造方法

【課題】バイポーラトランジスタの電極形成時に、MOSトランジスタを覆う層間絶縁膜上のポリシリコン膜のエッチング残りの発生を低減可能な半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法は、(a)バイポーラトランジスタ5とMOSトランジスタ6a、6bとが形成された半導体基板51を覆うように層間絶縁膜65を形成する工程と、(b)層間絶縁膜65を平坦化する工程と、(c)層間絶縁膜66におけるバイポーラトランジスタ5の電極70用の開口部68を形成する工程と、(d)層間絶縁膜66及び開口部68を覆うようにポリシリコン膜69を形成する工程と、(e)層間絶縁膜66上のポリシリコン膜69をエッチバックして、開口部68内に電極70を形成する工程とを具備する。

(もっと読む)

半導体装置の製造方法

【課題】トランジスタと抵抗素子とを備える半導体装置の製造工程を簡素化することが可能な技術を提供する。

【解決手段】NMOSトランジスタが形成される活性領域AR4と、拡散抵抗素子が形成される活性領域AR5とを半導体層2に区画する素子分離構造3を当該半導体層2に形成する。その後、n型のソース・ドレイン領域33を活性領域AR4に形成する。そして、得られた構造に対して、その上方からマスクレスでp型不純物102pを導入して、活性領域AR5に抵抗素子として機能する不純物領域を形成する。このとき、ソース・ドレイン領域33内からはみ出すことなく、かつソース・ドレイン領域33のうちp型不純物102pが導入される領域での導電型がn型を維持するように、活性領域AR4に対してp型不純物102pが導入される。

(もっと読む)

第二のポリ層の形成後に二重ポリバイポーラトランジスタの2つのレベルをドーピングするプロセス

【課題】

単結晶半導体材料よりエミッタドーパントに対して少なくとも1桁大きい材料の層の速い横方向拡散特性を用いる減少されたマスクの組とインプラントの複雑さを有する(高周波数応用)相補的バイポーラトランジスタ構造の製造プロセスを提供する。

【解決手段】

別のベースとエミッタポリ層がドープされずに形成される。それからあるデバイスのエミッタポリと他のデバイスのベースポリのエッジとはドーパントマスクを介して露出され、同時にドープされる。エミッタドーパントはエミッタポリの表面内に直接入り、ここでそれはベース上に位置し、それと接触している。ベース接触ドーパントは外因性ベースを形成するために高い拡散係数を有する材料の層を含むベースポリのエッジ内に入り、その層を通り抜けて迅速に横方向に拡散し、それからコレクタ材料(例えばアイランド)表面内に下方に拡散する。第二のマスクは第二のデバイスのエミッタと第一のデバイスのベースポリのエッジを露出するようパターン化され、それからドープされる。

(もっと読む)

半導体装置

【課題】 第1導電領域(一導電型半導体層)と第2導電領域(逆導電型領域または金属層)が接合し、これらの間に逆方向電圧を印加して高い耐圧を確保する半導体装置において、耐圧を向上させる場合には、一導電型半導体層の不純物濃度を低減したり、半導体層の厚みを増加させるなどの手法を採用しており、オン抵抗が増大するなどの問題があった。

【解決手段】 第1導電領域内の第1の深さに逆導電型の複数の第1埋め込み領域を設け、第2の深さに逆導電型の複数の第2埋め込み領域を設ける。第2埋め込み領域の距離(第2の距離)を、第1埋め込み領域の距離(第1の距離)より大きくする。逆方向電圧印加時には実際の接合部が臨界電界に達する以前に、第1埋め込み領域によって第1の深さにおいて水平方向の電界がピンチオフし、耐圧を向上させることができる。同様に、第1の深さにおける電界強度が臨界電界に達する以前に第2埋め込み領域によって第2の深さにおいて水平方向の電界がピンチオフし、耐圧を増加させることができる。

(もっと読む)

バイポーラトランジスタ及びその製造方法

【課題】半導体層間の隔離構造を改善してコレクタのサイズが減少し、半導体層間の電流が最短経路に流れることができ、コレクタ抵抗が最小化できるバイポーラトランジスタ及びその製造方法を提供する。

【解決手段】バイポーラトランジスタ100の製造方法は、基板101にコレクタ領域102が形成されるステップと、コレクタ領域102を含んだ基板101上にエピタキシャル層115が形成されるステップと、エピタキシャル層115にベース領域103が形成され、ベース領域103にエミッタ領域104が形成されるステップと、エミッタ領域104とベース領域103を貫通してコレクタ領域102までトレンチが形成され、トレンチの側壁に酸化膜108が形成されるステップと、トレンチの内部にポリシリコン層110が形成されるステップとを含む。

(もっと読む)

BICMOS統合のために選択的エピタキシャル成長を用いる、隆起した外因性自己整合型ベースを有するバイポーラ・トランジスタ

【課題】BICMOS統合のために選択的エピタキシャル成長を用いる、隆起した外因性自己整合型ベースを有するバイポーラ・トランジスタを提供する。

【解決手段】隆起した外因性自己整合型ベースを有する高性能バイポーラ・トランジスタが、CMOSデバイスを含むBiCMOS構造と統合される。パッド層を形成して、先在するCMOSデバイスのソースおよびドレインに対して真性ベース層の高さを隆起させることにより、かつ選択的エピタキシを介して外因性ベースを形成することにより、表面の凹凸の影響は、外因性ベースのリソグラフィによるパターン形成時に最小になる。また、バイポーラ構造の製作の間に、化学機械研磨プロセスを使用しないことにより、プロセス統合の複雑さが軽減される。内側のスペーサまたは外側のスペーサが、エミッタからベースを分離するために形成されうる。パッド層、真性ベース層、および外因性ベース層は、一致した外側の側壁表面を有するメサ構造を形成する。

(もっと読む)

1 - 20 / 63

[ Back to top ]