Fターム[5F003BP33]の内容

バイポーラトランジスタ (11,930) | 製法 (1,830) | エピタキシャル (577) | 選択エピタキシャル (76)

Fターム[5F003BP33]に分類される特許

1 - 20 / 76

ヘテロ接合バイポーラトランジスタ

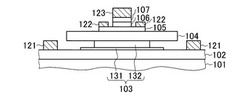

【課題】コレクタメサ表面で発生するコレクタリーク電流を抑制し、微細なHBTのコレクタ耐圧特性を改善する。

【解決手段】第2サブコレクタ層103は、第1サブコレクタ層102より平面視で小さい面積に形成されている。また、コレクタ層104は、第2サブコレクタ層103を構成している半導体層132より平面視で大きい面積に形成されている。また、ベース層105は、コレクタ層104より平面視で小さい面積に形成されている。また、エミッタ層106は、ベース層105より平面視で小さい面積に形成されている。加えて、第2サブコレクタ層103を構成している半導体層132およびベース層105は、平面視でコレクタ層104の内側の領域に形成されている。

(もっと読む)

半導体装置の製造方法

【課題】バイポーラトランジスタの動作速度を高速化できるようにした半導体装置の製造方法を提供する。

【解決手段】単結晶Si基板1に設けられたn型のコレクタ層20と、コレクタ層20の表面の周辺部上に設けられたSiO2膜21と、SiO2膜21を覆ってコレクタ層20の表面の中央部に接合するp型のベース層30と、を有し、ベース層30は、コレクタ層20の表面の中央部上に設けられた単結晶SiGe膜31aと、SiO2膜21を覆うように単結晶SiGe膜21上に積層された単結晶Si膜35aとを含む。ベース層30とコレクタ層20との接合領域60がコレクタ層20の表面の中央部に限定されるため、接合面積を小さくすることができ、ベース層とコレクタ層との間の容量CBCを低減することができる。

(もっと読む)

半導体装置の製造方法

【課題】本発明の実施形態は、ベース層の幅を狭く形成しエミッタ層の不純物濃度を高くした低雑音特性を有する半導体装置の製造方法を提供することを目的とする。

【解決手段】一実施形態に係る半導体装置の製造方法は、第1導電型の第1半導体層の上に第2導電型の第2半導体層を成長する半導体装置の製造方法であって、前記第1半導体層の表面を常圧よりも低い圧力の還元性雰囲気に曝して熱処理する工程(S02〜S04)と、前記第1半導体層の表面上に、前記第2半導体層を常圧の雰囲気でエピタキシャル成長する工程(S05〜S07)と、を備えたことを特徴とする。

(もっと読む)

半導体装置及びその製造方法

【課題】バイポーラトランジスタや縦型FET等の縦型デバイスを、絶縁膜マスクを用いた選択成長による、ボトムアップ構造にするすることで、精密な制御を要求される工程を削減できる製造方法を提供する。

【解決手段】導電性基板20の第1主表面上に、第1絶縁膜32、金属膜42及び第2絶縁膜52を順次に形成する。次に、第1絶縁膜、金属膜及び第2絶縁膜の、中央領域の部分を除去することにより、導電性基板を露出する成長用開口部70を形成する。次に、成長用開口部内に、半導体成長部82,84を形成する。次に、第2絶縁膜の、中央領域の周囲の周辺領域内に設けられた引出電極領域の部分72を除去することにより、金属膜を露出する引出電極用開口部を形成する。次に、引出電極用開口部内72に、引出電極90を形成する。次に、半導体成長部上及び導電性基板の第2主表面上にオーミック電極92を形成する。

(もっと読む)

バイポーラトランジスタおよびその製造方法

【課題】HBT(ヘテロジャンクション・バイポーラトランジスタ)による段差を低減し、接合面積をより小さくできる製造方法を提供する。

【解決手段】半絶縁性のInPからなる基板101の上に形成されたアンドープInPからなる第1半導体層102と、第1半導体層102の上に接して形成された第1導電型のInPからなるエミッタ層103と、第1半導体層102の上に接して形成されたInGaAsからなるコレクタ層108と、第1半導体層102の上に接して形成され、エミッタ層103およびコレクタ層108に挟まれて配置された第2導電型のInGaAsからなるベース層105とを備える。また、半絶縁性のInPからなる第1分離層106aおよび第2分離層106bを備える。

(もっと読む)

バイポーラトランジスタおよびその製造方法

【課題】HBTによる段差を低減し、接合面積をより小さくできるようにする。

【解決手段】半絶縁性のInPからなる基板101の上に形成されたアンドープInPからなる第1半導体層102と、第1半導体層102の上に接して形成された第1導電型のInPからなるエミッタ層103と、第1半導体層102の上に接して形成された第2導電型のInGaAsからなるベース層106と、第1半導体層102の上に接して形成されたInGaAsからなるコレクタ層107とを少なくとも備える。加えて、エミッタ層103,ベース層106,およびコレクタ層107は、これらの順に第1半導体層102の平面上で配列して接続されている。

(もっと読む)

埋め込み絶縁層を貫いて半導体層間に接触を有するデバイス、およびこのデバイスの製造プロセス

【課題】簡潔な方法で、SeOI基板上の半導体デバイスの半導体領域に接続するラインを提供すること。

【解決手段】第1の側面によると、本発明は埋め込み絶縁層(3、BOX)によってベース基板(2)から隔離された半導体材料の薄い層(1)を含むSeOI(Semiconductor−On−Insulator)基板上に作製された半導体デバイスに関し、デバイスは、薄い層内に第1の伝導領域(1、D1、S、E)と、ベース基板内に第2の伝導領域(5、BL、SL、IL)とを含み、接触(I1、I2、IN、IP)は絶縁層を貫通して第1の領域と第2の領域を接続する。第2の側面によると、本発明は第1の側面に関する半導体デバイスの製作プロセスに関する。

(もっと読む)

半導体装置およびその製造方法

【課題】低コストで性能向上が可能なBiCMOS型半導体集積回路装置を実現することができる半導体装置およびその製造方法を提供する。

【解決手段】n型の半導体基板1の表面から所定の深さに、コレクタ領域を構成するn型の不純物領域26を備える。当該不純物領域26の上方、かつ半導体基板1に形成されたシャロートレンチ分離14で挟まれた領域18にはp型のベース領域20を備える。ベース領域20には、n型の半導体膜からなるエミッタ電極が接触して設けられている。当該半導体装置は、不純物領域26がベース領域20下からシャロートレンチ分離14下まで延在し、当該シャロートレンチ分離14を貫通して不純物領域26に電気的に接続するコンタクトプラグ52を備える。

(もっと読む)

半導体装置及びその製造方法

【課題】III-V族窒化物半導体に設けるオーミック電極のコンタクト抵抗を低減しながらデバイスの特性を向上できるようにする。

【解決手段】半導体装置(HFET)は、SiC基板11上にバッファ層12を介在させて形成された第1の窒化物半導体層13と、該第1の窒化物半導体層13の上に形成され、該第1の窒化物半導体層13の上部に2次元電子ガス層を生成する第2の窒化物半導体層14と、該第2の窒化物半導体層14の上に選択的に形成されたオーム性を持つ電極16、17とを有している。第2の窒化物半導体層14は、底面又は壁面が基板面に対して傾斜した傾斜部を持つ断面凹状のコンタクト部14aを有し、オーム性を持つ電極16、17はコンタクト部14aに形成されている。

(もっと読む)

半導体基板、電子デバイス、半導体基板の製造方法及び電子デバイスの製造方法

【課題】半導体基板、電子デバイス、半導体基板の製造方法及び電子デバイスの製造方法を提供する。

【解決手段】シリコンに不純物原子が導入された不純物領域104を有するベース基板102と、不純物領域104に接して設けられている複数のシード体112と、複数のシード体112の各々に接して設けられ、複数のシード体112の各々とそれぞれ格子整合または擬格子整合する複数の化合物半導体114とを備える半導体基板100。当該半導体基板100は、ベース基板102上に設けられ、不純物領域104の少なくとも一部を露出する複数の開口が設けられた阻害体をさらに備えてもよい。

(もっと読む)

イオン注入せずに縦型接合形電界効果トランジスタおよびバイポーラ接合トランジスタを製造する方法およびそれによって製造されたデバイス

縦型接合形電界効果トランジスタ(VJFET)またはバイポーラ接合トランジスタ(BJT)のような半導体デバイスを製造する方法が記載される。その方法はイオン注入を必要としない。VJFETデバイスは、エピタキシャル成長した埋め込みゲート層のみでなく、エピタキシャル再成長したn型チャネル層及びエピタキシャル再成長したp型ゲート層も有する。その方法で製造されたデバイスも記載される。 (もっと読む)

バイポーラトランジスタ及びその製造方法

【課題】エミッタ接地直流増幅率のばらつきを低減し、かつ抵抗の増大を防止できる、信頼性に優れるバイポーラトランジスタを得ること。

【解決手段】本発明は、N−型エピ層3aやP−型シリコン基板1aを含む半導体基板、N+型ポリシリコン層21a、タングステン層25、シリサイド層27a、シリサイド層39a、ベース電極36a、エミッタ電極36b及びコレクタ電極36cを少なくとも備える。半導体基板上に形成されたN+型ポリシリコン層21aはシリサイド層27aに覆われる。シリサイド層27a上の形成されたタングステン層25はシリサイド層39aに覆われる。

(もっと読む)

半導体基板、半導体基板の製造方法、電子デバイス、および電子デバイスの製造方法

【課題】結晶薄膜を有する半導体基板の設計および上記結晶薄膜の膜質および膜厚の制御を容易にできる半導体基板を提供する。

【解決手段】ベース基板と、ベース基板上に、一体にまたは分離して設けられ、化合物半導体の結晶成長を阻害する阻害層とを備え、阻害層は、ベース基板まで阻害層を貫通する複数の開口を有する複数の第1開口領域を有し、複数の第1開口領域のそれぞれは、内部に同一の配置で設けられた複数の第1開口を含み、複数の第1開口の一部は、電子素子が形成されるべき第1化合物半導体が設けられている第1素子形成開口であり、複数の第1開口の他の一部は、電子素子が形成されない第1ダミー開口である半導体基板を提供する。

(もっと読む)

半導体基板、電子デバイス、および半導体基板の製造方法

【課題】電子デバイスのスイッチング速度等の性能を向上させる。半導体基板の結晶性を向上させる。

【解決手段】ベース基板と、絶縁層と、SixGe1−x結晶層とをこの順に有する半導体基板であって、SixGe1−x結晶層上に設けられる阻害層と、SixGe1−x結晶層に格子整合または擬格子整合している化合物半導体とを備え、阻害層はSixGe1−x結晶層にまで貫通する開口を有し、かつ化合物半導体の結晶成長を阻害する半導体基板を提供する。また、上記開口の内部でSixGe1−x結晶層に格子整合または擬格子整合する化合物半導体と、化合物半導体を用いて形成された半導体デバイスとを備える電子デバイスを提供する。

(もっと読む)

接合の作製方法

【課題】バイポーラトランジスタのエミッタ−ベース界面において、ドーパント濃度プロファイルを制御する方法を提供する。

【解決手段】第1濃度を有する第1ドーパントを含む第1半導体材料を形成する工程と、その上に、第2濃度を有し、これにより接合を形成する、第2ドーパントを含む第2半導体材料を形成する工程と、第2半導体材料を形成する前に、原子層エピタキシまたは気相ドーピングにより、第1半導体材料の上に、第2ドーパントを形成するのに適した、単分子層の少なくとも一部分の前駆体を堆積し、これにより接合における第2ドーパントの第2濃度を増加させる工程と、を含む(またはこれらの工程からなる)。

(もっと読む)

シリコン基板上に形成されるCMOSデバイスおよびIII−V族デバイスのための電気コンタクト

半導体構造体は、基板(12)と、基板を覆うシード層(13)と、シード層上に配置されるシリコン層(22)と、シリコン層中のトランジスタデバイス(27)と、シード層上に配置されるIII−V族デバイスと、複数の電気コンタクトと、を備え、それぞれの電気コンタクトは、TiNまたはTaNの層(32)と、TaNまたはTiNの層上の銅またはアルミニウムの層(34)と、を備え、電気コンタクトの1つは、トランジスタ(27)に電気的に接続され、電気コンタクトの別の1つは、III−V族デバイスに電気的に接続される。 (もっと読む)

半導体装置および半導体装置の製造方法

【課題】寄生容量を低減しつつ、トランジスタが形成される半導体層に歪応力を与える。

【解決手段】半導体層3に形成されたコレクタ層3aの表面および裏面にストレス印加層5を形成し、ストレス印加層5を介して埋め込み絶縁層6上に配置されたベース層9をコレクタ層3aの側壁に選択的に形成し、ベース層9の側壁を絶縁膜10から露出させる開口部12を形成し、開口部12を介してベース層9の側壁に接続されたエミッタ層13aを埋め込み絶縁層6上に形成する。

(もっと読む)

半導体基板の製造方法、半導体基板、電子デバイスの製造方法、および反応装置

【課題】耐熱性の低い部分を有する基板であっても加熱処理が可能となる、基板の熱処理方法を提供する。

【解決手段】熱処理される被熱処理部を備えるベース基板を熱処理して半導体基板を製造する方法であって、電磁波を吸収して熱を発生し、被熱処理部を選択的に加熱する被加熱部をベース基板上に設ける段階と、ベース基板に電磁波を照射する段階と、被加熱部が電磁波を吸収することにより発生する熱によって、被熱処理部の格子欠陥密度を低減する段階とを備える半導体基板の製造方法を提供する。

(もっと読む)

半導体基板の製造方法、半導体基板、電子デバイスの製造方法、および反応装置

【課題】耐熱性の低い部分を有する基板に加熱処理をして半導体基板を製造する。

【解決手段】単結晶層を有し熱処理される被熱処理部と、熱処理で加えられる熱から保護されるべき被保護部とを備えるベース基板を熱処理して半導体基板を製造する方法であって、被保護部の上方に、ベース基板に照射される電磁波から被保護部を保護する保護層を設ける段階と、ベース基板の全体に電磁波を照射することにより被熱処理部をアニールする段階とを備える半導体基板の製造方法を提供する。

(もっと読む)

半導体デバイス用基板、半導体デバイス装置、設計システム、製造方法、および設計方法

【課題】結晶薄膜の膜質および膜厚を均一にする。

【解決手段】半導体デバイスを形成するためのデバイス用薄膜と、デバイス用薄膜を囲み、デバイス用薄膜の前駆体が結晶に成長することを阻害する阻害部と、前駆体が結晶に犠牲成長することによって形成された犠牲成長部であって、デバイス用薄膜の周辺に阻害部で隔てられて設けられた犠牲成長部と、犠牲成長部の上部を覆い、かつデバイス用薄膜の上部を露出する保護膜を備えた。保護膜はポリイミドであってもよい。

(もっと読む)

1 - 20 / 76

[ Back to top ]