Fターム[5F004DA26]の内容

半導体のドライエッチング (64,834) | 処理に用いるガス (14,486) | O2 (2,010)

Fターム[5F004DA26]に分類される特許

2,001 - 2,010 / 2,010

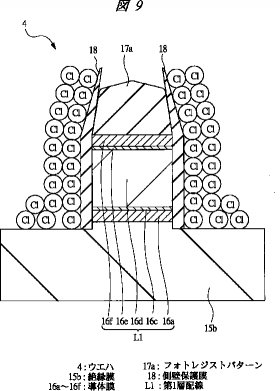

半導体集積回路装置の製造方法

【課題】 アルミニウムを主成分とする導体膜パターンを有する半導体集積回路装置の信頼性を向上させる。

【解決手段】 アルミニウムを主成分とする導体膜16dを有する第1層配線L1をドライエッチング法によってパターニングした後、その加工側壁の側壁保護膜18およびエッチングマスクとして使用したフォトレジストパターン17aをプラズマアッシング処理によって除去する。続いて、絶縁膜15bおよび第1層配線L1の表面に付着した塩素成分を、酸素ガスとメタノールガスとの混合ガスを用いたプラズマアッシング処理によって除去する。この際、フォトレジストパターン17a等のアッシング除去処理時は、ウエハの主面温度が相対的に低くなるようにし、塩素成分の除去処理時は、ウエハの主面温度が相対的に高くなるようにする。また、それらのプラズマアッシング処理を別々の処理室で行う。

(もっと読む)

プラズマプロセス用装置

【技術課題】 基板に損傷や表面汚染を与えることなく、エッチングや成膜が行え、チャンバや電極等の構造は同一であるにも拘らず、導入するガスやプラズマ励起周波数を変えることにより、エッチングや成膜にも応用可能であり、生産性に優れるとともに、低価格で高性能なプラズマプロセス用装置を提供すること。

【解決手段】 容器内105に対向するように設けられ夫々平板状に形成された第1及び第2電極102,104と、プラズマに対して安定な材料から成り第1電極102上を覆うように設けられる保護部材101と、第2電極104上に被処理物103を取り付けるための保持手段と、第1電極102に接続される第1の高周波電源111と、第2電極104に接続される第2の高周波電源110と、容器105内に所望のガスを導入するためのガス供給手段とを少くとも備え、第1の高周波電源の周波数が前記第2の高周波電源の周波数より高いことを特徴とする。

(もっと読む)

プラズマ処理装置およびプラズマ処理装置の性能確認システム

【課題】 プラズマ処理をおこなうチャンバ全体としては、電気的高周波的な特性が考慮されていなかった。

【解決手段】 プラズマを励起するための電極を有するプラズマチャンバCNと、この電極4,8に接続された高周波電源1と、プラズマチャンバCNと高周波電源1とのインピーダンス整合を得るための整合回路2とを具備し、整合回路2Aをその出力端PRから切り離し、給電板3で測定したプラズマチャンバCNの第1直列共振周波数f0 の3倍が、高周波電源1からプラズマチャンバCNに供給される電力周波数fe より大きな値の範囲に設定されてなる。

(もっと読む)

強誘電体膜を有する半導体装置の製造方法

【課題】強誘電体膜をエッチングする際に生じる反応副生成物を形成される素子に悪影響を与えることなく除去する。

【解決手段】強誘電体膜をエッチングしたあと、燐酸水溶液を用いてウェット処理をする。レジストをマスクとして強誘電体膜をエッチングしたあと、レジストアッシング後またはアッシング前後の両方に燐酸水溶液を用いてウェット処理をする。

(もっと読む)

局所処理装置

【課題】 絶縁保持が効果的になされ、もれ電流を最小化することができる局所処理装置を提供する。

【解決手段】 外部からの電磁的遮蔽をなすケーシングを有する。前記ケーシングの管通路上に放電管を設ける。前記放電管の一端をガス供給源に接続して放電管内に処理用気体を導入可能とする。前記放電管の他端にノズルを脱着自在に連結して、当該ノズルより処理用気体を外部に放出可能とする。前記放電管を挟むように一対の電極を対向配置して、当該電極の一方にリードの一端を接続し、当該リードの他端をケーシング部材外部の高周波電力源に接続して伝導経路を形成しする。これにより、ケーシング内を密閉空間とするとともに前記伝導経路の周囲に中空部分を設けて絶縁空間を形成した。

(もっと読む)

多結晶シリコン薄膜の平坦化方法

【課題】 多結晶シリコン薄膜の表面に形成された突起を容易且つ確実に除去することができる多結晶シリコン薄膜の平坦化方法を提供することを目的とする。

【解決手段】 多結晶シリコン薄膜を炭素(C)とフッ素(F)と水素(H)とを少なくとも含有するガスのプラズマに曝すことにより突起を除去して多結晶シリコン薄膜の表面を容易且つ確実に平坦化することができる。

(もっと読む)

半導体装置の製造方法

【課題】 欠陥のないエピタキシャル膜を形成する

【解決手段】 異物除去処理を有し、ドライエッチング処理を行って形成した開口部5内の単結晶シリコン基板1に、SiGeエピタキシャルベース7を成長させる半導体装置の製造方法である。異物除去処理は、前記ドライエッチング処理後からSiGeエピタキシャルベース7の成長までの間に、被成長基板を酸素雰囲気中において、熱処理を行い、ドライエッチング処理によって、シリコン酸化膜2に堆積した炭素系付着物10を、シリコン酸化膜2から完全に除去し、これによって、欠陥のないエピタキシャル膜を形成する。

(もっと読む)

半導体装置の製造方法

【課題】 シリル化プロセスを用いて微細なパターンの形成を可能とし、しかもシリル化部表面に形成されるSiOx 層の除去を支障なく行うことのできる、半導体装置の製造方法が提供が望まれている。

【解決手段】 下地基板20上の被パターニング層23上にレジスト層24を形成し、次にレジスト層24の所定箇所を露光し、次いでこの露光工程後のレジスト層24における未露光部分をシリル化する。続いて、露光した箇所のレジスト層24をドライ現像によって除去し、シリル化された部分に対応した積層パターン30を得る。次いで、積層パターン30からその表層部に形成されたSiOx層29を除去してレジストパターン32を形成する。その後、レジストパターン32をマスクにして被パターニング層23をエッチングする。

(もっと読む)

多層配線構造の形成方法

【課題】 SOG膜のSi原子と有機基(例えばCH3基)やH基の結合がアッシング時に切れるのを抑制して誘電率を低く抑える。

【解決手段】 低誘電率の有機又は無機SOG膜にパターン化レジスト膜をマスクとしてエッチングを行って配線溝を形成し、この後、枚葉式ダウンストリーム型のプラズマアッシング装置を用いて、酸素ガスプラズマによるアッシング処理を例えば1.2Torrの圧力雰囲気下で施してレジスト膜を除去し、この後配線溝にバリヤメタル形成後、Cuを電界メッキ法にて埋設して配線を形成する。

(もっと読む)

回路基板

【課題】 内部配線パターンを電源/グランド層によりシールドすることにより特性インピーダンスやクロストークノイズの影響を改善でき、また厚さを薄く形成できる回路基板を提供する。

【解決手段】 コア基板1の両面に内部配線パターン2が形成されており、該内部配線パターン2の上に絶縁樹脂層3を介して電源/グランド層5が各々形成されてなる回路基板4であって、表層の絶縁樹脂層3がドライエッチングにより除去されて形成された凹部6に露出する内部配線パターン2に電子部品7が表面実装可能になっている。

(もっと読む)

2,001 - 2,010 / 2,010

[ Back to top ]