Fターム[5F004DB07]の内容

半導体のドライエッチング (64,834) | 被エッチング物 (6,778) | Si3N4 (525)

Fターム[5F004DB07]に分類される特許

141 - 160 / 525

プラズマ処理方法

【課題】半導体デバイスを製造する際のプラズマ処理工程において、ウエハに付着する異物を大幅に低減し、歩留まりを向上させる。

【解決手段】プラズマ分布を制御可能なプラズマ源を備えたプラズマ処理装置において、プラズマOn/Off時に、ウエハ上のシース/バルク境界面の形状を凸型に制御する。プラズマOn/Off時に、低めのソース電力とウエハバイアス電力を印加し、プラズマ分布を外高に制御するステップを入れることにより、ウエハの中心付近では厚いシースが、外周付近ではそれより薄いシースが形成される。

(もっと読む)

基板処理装置および基板処理方法

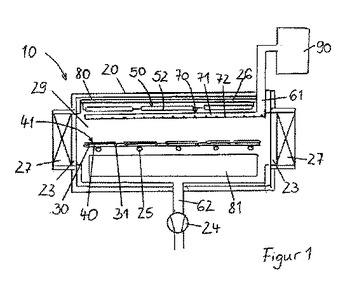

本発明は、少なくとも1つの基板を担持した少なくとも1つの基板キャリアを中に導入することができる少なくとも1つの排気可能なプロセス・チャンバと、プラズマ発生モジュールと、少なくとも1つのガス供給部と、少なくとも1つのガス排出部とを備える基板処理装置に関する。さらに、本発明は、少なくとも1つの基板を担持した少なくとも1つの基板キャリアが少なくとも1つの排気可能なプロセス・チャンバに導入され、プロセス・チャンバ内で、プラズマ・プロセスにおいてプラズマ発生モジュールによってガスまたはガス混合物中でプラズマが発生され、基板のコーティング、エッチング、表面改質、および/または洗浄が行われる基板処理方法に関する。本発明の目的は、十分に表面テクスチャ加工された基板でさえ高いスループットおよび高品質で等方性エッチングすることができる、上記の一般的なタイプの基板処理装置および基板処理方法を提供することである。この目的は、まず、上記の一般的なタイプの基板処理装置であって、気相エッチング・モジュールがプロセス・チャンバ内に組み込まれた基板処理装置によって実現される。さらに、この目的は、上記の一般的なタイプの基板処理方法であって、プロセス・チャンバ内で、少なくとも1つの基板の気相エッチングが、プラズマ・プロセスの前に、および/またはプラズマ・プロセスの後に、および/またはプラズマ・プロセスと交互に行われる基板処理方法によって実現される。  (もっと読む)

(もっと読む)

半導体集積回路装置の製造方法

【課題】Cuダマシン多層配線構造におけるセミ・グローバル配線の形成方法において、ダマシン配線構造を形成する際、ドライ・エッチングによりビア底のエッチ・ストップ絶縁膜を除去した後、ビア底表面上のカーボン系堆積物等を抑制する為に、窒素プラズマ処理を行うことが一般的である。その後、連続放電によって窒素プラズマ除電を行ってウエハ搬送するシーケンスを実行すると、ビア・チェーン終端部にて、ある閾値以上の長さを有するパッド引き出し配線に接続された終端部のビア底で、Cuえぐれが発生ことが、本願発明者らの検討によって明らかとなった。

【解決手段】本願発明は、ダマシン・セミ・グローバル配線等のビア・ホール形成工程において、ビア底エッチ・ストップ膜に対するドライ・エッチング処理後、同処理室内で行われる窒素プラズマ処理に引き続いて、アルゴン・プラズマによる除電処理を実行するものである。

(もっと読む)

多層膜の形成方法及び表示パネルの製造方法

【課題】予め定めた形状にパターニングされた導電層の上下に配置されている絶縁層のそれぞれにコンタクトホールを形成し、これらコンタクトホールを介して互いに異なる層として形成された2つの導電層を互いに電気的に接続する場合であっても、導電不良が生じ難い多層膜の形成方法及び表示パネルの製造方法を提供する。

【解決手段】基板2上に成膜された第1導電層40上に第1絶縁層20を成膜し、前記第1絶縁層20上に第2導電層41を成膜し、前記成膜した第2導電層41をパターニングし、パターニングされた前記第2導電層41を覆うように前記基板2上に第2絶縁層25を成膜し、前記第2絶縁層25上に該第2絶縁層25よりもエッチング速度が速い第3絶縁層26を成膜し、前記第1絶縁層20、前記第2絶縁層25及び前記第3絶縁層26に対して前記第1導電層40の少なくとも一部を露出させるコンタクトホールを一括形成する。

(もっと読む)

プラズマ処理装置

【課題】種々の被エッチング材料、プロセス条件に対応可能なエッチング特性分布調整手段を提供する。

【解決手段】内部を減圧可能な減圧処理室8と、該減圧処理室内に処理ガスを供給するガス供給手段と、前記減圧処理室内にマイクロ波を供給してプラズマを生成するマイクロ波供給手段1と、前記減圧処理室内に静磁場を生成する磁場生成用コイル18,19と、前記減圧処理室内に被処理材である試料を載置して保持する試料載置電極11と、前記減圧処理室に接続され該減圧処理室内のガスを排気する真空排気手段14を備え、前記減圧処理室、ガス供給手段の処理室へのガス供給部、マイクロ波供給手段の処理室へのマイクロ波導入部、試料載置電極、および真空排気手段を前記減圧処理室の中心軸に対して同軸上に配置し、前記マイクロ波導入部は、直線偏波のマイクロ波を円偏波のマイクロ波に変換するマイクロ波回転発生器22を備え、前記磁場生成用コイルに励磁電流を供給する励磁回路には励磁電流を反転して供給する手段33を備えた。

(もっと読む)

高選択性、低損傷の電子ビーム・デリニエーション・エッチング

【課題】集束ビームを使用して基板を選択的にエッチングする方法および装置を提供する。

【解決手段】ステップ102では、少なくとも2種類の材料を有する基板を用意する。この基板は、その上に集積回路が製造されたシリコン・ウェーハとし、この基板はさらに、集積回路の一部分の断面を露出させるために集束イオン・ビームによって切削されたトレンチを含む。ステップ104では、エッチングする基板表面の一部分に、エッチング剤前駆体ガスの流束を供給する。ステップ106では、基板表面に、エッチング抑制前駆体ガスの流束を供給する。ステップ108では、電子ビームなどの集束ビームを基板に向かって、少なくとも2種類の材料を含む領域上に誘導する。このエッチング前駆体ガス、エッチング抑制ガスおよび集束ビームの組合せは、第1の材料を第2の材料に比べて選択的にエッチングする。

(もっと読む)

窒化珪素膜のドライエッチング方法

【課題】スループットを向上できる窒化珪素膜のドライエッチング方法を提供すること。

【解決手段】窒化珪素膜103をドライエッチングする窒化珪素膜103のドライエッチング方法であって、窒化珪素膜103が形成された被処理体100に対して、少なくともフッ化水素ガス(HFガス)とフッ素ガス(F2ガス)とを含む処理ガスを用いて、プラズマを生成することなく、窒化珪素膜103をドライエッチングする。

(もっと読む)

プラズマクリーニング方法

【課題】主にカソード電極の放電面に付着した堆積物を残留させずに効率よく、かつ電極にダメージを与えることなく除去することができるプラズマクリーニング方法を提供すること。

【解決手段】平板状のカソード電極1およびアノード電極2を平行に対向して内部に有するチャンバーC1内にクリーニングガスG2を導入し、カソード電極1とアノード電極2の間でクリーニングガスG2を介してプラズマ放電させ、プラズマ放電を維持しながらカソード電極1とアノード電極2の間の電極間距離を所定の電極間距離まで広げる方向にカソード電極1とアノード電極2を相対的に徐々に移動させる電極クリーニング工程を含むことを特徴とするプラズマクリーニング方法。

(もっと読む)

窒化シリコン膜のドライエッチング方法および薄膜トランジスタの製造方法

【課題】 SF6等の地球温暖化の一因となるガスを用いずに、真性アモルファスシリコン膜上の窒化シリコン膜を良好にドライエッチングする。

【解決手段】 成膜された真性アモルファスシリコン膜21の上面には窒化シリコン膜22が成膜され、その上面にはレジスト膜23が形成されている。そして、エッチングガスとしてフッ素ガス(100sccm)および酸素ガス(100〜400sccm)の混合ガスを用いた反応性イオンエッチングを行なうと、レジスト膜23下以外の領域における窒化シリコン膜22がドライエッチングされ、そのエッチングレートは約2000Å/minであった。この場合、窒化シリコン膜22が完全に除去されると、下地の真性アモルファスシリコン膜21が露出され、この露出された真性アモルファスシリコン膜21がある程度ドライエッチングされるが、そのエッチングレートは約400Å/minであった。したがって、この場合の選択比は約5である。

(もっと読む)

半導体装置の製造方法及び基板処理装置

【課題】 処理室内のドライクリーニング直後の薄膜形成工程における成膜速度の低下を抑制しつつ、処理室内の金属汚染や石英部材の破損を抑制すると共に、装置稼働率を向上させる。

【解決手段】 第1の温度に加熱された処理室内にクリーニングガスとして、フッ素ガスを単独で、もしくは不活性ガスで希釈されたフッ素ガスを単独で供給し、処理室内に堆積した薄膜を熱化学反応により除去する工程と、第2の温度に加熱された処理室内にクリーニングガスとして、フッ素ガスを単独で、もしくは不活性ガスで希釈されたフッ素ガスを単独で供給し、薄膜の除去後に処理室内に残留した付着物を熱化学反応により取り除く工程と、を有し、第2の温度を第1の温度と同等の温度とする。

(もっと読む)

半導体装置の製造方法

【課題】基板の外観特性を改善できるようにした半導体装置の製造方法を提供する。

【解決手段】上部電極21と、上部電極21と向かい合って配置される下部電極23とを有し、上部電極21と下部電極23との間の空間35内に反応性ガス(例えば、CF4、CHF3等)を供給するRIE装置50の、下部電極23上にウエーハWを配置してパシベーション膜をエッチングする際に、排気スペース33の高さhを調整する。これにより、空間35内において、反応性ガスの含有量を調整することができる。

(もっと読む)

コンタクトホール形成方法、電気光学装置用基板、電気光学装置及び電子機器

【課題】コンタクトホールの微細化を図りつつ、コンタクトホールを形成する際のエッチング処理に起因する不具合を抑制する。

【解決手段】コンタクトホール形成方法は、第1レジストパターンをマスクとして、第2材料を含んでなる第2層を、エッチング液を用いてパターニングして、第1材料を含んでなる第1層を部分的に露出させる第1開口部を形成する第1エッチング工程と、第2レジストパターンをマスクとして、第4材料を含んでなる第4層を、エッチングガスを用いてパターニングして、形成された第1開口部の少なくとも一部に対応すると共に、第3材料を含んでなる第3層を部分的に露出させる第2開口部を形成する第2エッチング工程とを備える。第1材料は、エッチング液によりエッチングされる度合いが第2材料に比べて小さい材料であり、第3材料は、エッチングガスによりエッチングされる度合いが第4材料に比べて小さい材料である。

(もっと読む)

積層構造体及びその製造方法

【課題】生産性が向上し、かつ、半導体膜の導電膜からのはみ出し量が低減できる積層構造体及びその製造方法を提供すること。

【解決手段】本発明にかかる積層構造体は、半導体膜15、ゲート絶縁膜12、ソース電極17、及びドレイン電極18を有するものである。ゲート絶縁膜12は、半導体膜15下において、半導体膜15の端から徐々に膜厚が薄くなるテーパー部を有する。ソース電極17及びドレイン電極18は、半導体膜15上において、半導体膜15のパターンからはみ出さないように形成され、半導体膜15端からの距離が0以上0.3um以下である。

(もっと読む)

プラズマ処置装置

【課題】真空処理室内に生成されたのプラズマの発光強度の分布を簡易な構成で高速に測定する。

【解決手段】真空処理室2、該真空処理室内に試料を載置して保持する試料台7、および前記真空処理室内に導入されたプロセスガスに高周波エネルギを供給してプラズマを生成するプラズマ生成手段4を備えたプラズマ処理装置において、生成されたプラズマからの発光を前記真空処理室の外部で受光する受光器13と、前記受光器と真空処理室の間に設けられ、前記プラズマからの発光のうち前記受光器に導入されるプラズマの範囲を調整する受光調整器14と、前記受光調整器を調整して受光器による受光範囲を変更して得られた受光量をもとにプラズマ処理装置を制御する制御装置16を備えた。

(もっと読む)

遠隔の励起源を用いる堆積チャンバーのクリーニング技術

【課題】チャンバー内部のハードウェアに対してダメージを生じさせないインシチュウ・クリーニング方法及び装置を提供する。

【解決手段】電子デバイス製作に用いられる堆積チャンバー10のクリーニング方法は、以下のステップを含む:堆積チャンバーの外部にある遠隔チャンバー46に、前駆体ガス44を供給する;遠隔チャンバー46内で該前駆体ガス44を活性化させて反応性の化学種を形成する;遠隔チャンバー46から堆積チャンバー10へ該反応性の化学種を流す;および、遠隔チャンバー46から堆積チャンバー10へ流れ込んだ反応性の化学種を用いて、堆積チャンバー10の内部をクリーニングする。

(もっと読む)

固体撮像装置の製造方法及び固体撮像装置

【課題】パッド電極の腐食を抑制することによって、パッド電極とワイヤーボンド、若しくは、パッド電極とバンプとの接合強度が高い固体撮像装置を提供する。

【解決手段】アルミニウム材料からなるパッド電極3が設けられた半導体基板2と、半導体基板上に成膜され、パッド電極3の上方領域がフッ素系ガスをエッチングガスとするドライエッチング処理によって開口した絶縁膜4と、絶縁膜4の上層に成膜され、パッド電極3の表面を被覆する保護膜6とを備える固体撮像装置であり、保護膜6はドライエッチング処理時のエッチングガスを堆積させて成膜したフロロカーボンである。

(もっと読む)

フォトマスク、フォトマスクの製造方法、及びプラズマエッチングチャンバシステム

【課題】極紫外線フォトマスク、フォトマスクの製造方法、及びプラズマエッチングチャンバシステムを提供する。

【解決手段】極紫外線フォトマスク、フォトマスクの製造方法、及びプラズマエッチングチャンバシステム装置が提供される。極紫外線フォトマスクの製造方法は、フォトマスク基板10上に上部膜を形成した後、上部膜をパターニングして傾いた側壁を有する上部パターン45を形成する段階を含む。上部膜をパターニングする段階は、上部膜の上部面に傾いた第1方向に平行に運動する荷電された粒子を使用して、上部膜を異方性エッチングする段階を含む。

(もっと読む)

多層マスクの除去方法および半導体装置の製造方法

【課題】シリコン含有膜を有する多層マスクを、シリコン化合物を含む残渣を残存させることなく、容易に確実に除去できる多層マスクの除去方法および半導体素子の製造方法を提供する。

【解決手段】シリコンを含有しない第1膜13と、シリコン含有膜からなる第2膜14と、レジスト層からなる第3膜15とを順に形成してなる多層膜の第3膜15をパターニングし、パターニングされた第3膜15を有する多層膜に不具合がない場合には、第3膜15をマスクとして、ドライエッチングにより第2膜14をパターニングし、多層膜に不具合がある場合には、多層膜に不具合のない場合におけるドライエッチングよりも、第1膜13のエッチング速度と第2膜14のエッチング速度との差が大きいドライエッチングにより第2膜14を除去する多層マスクの除去方法とする。

(もっと読む)

半導体装置の製造方法

【課題】微細化された3次元的なデバイスを実現し得る、半導体装置の製造方法を提供する。

【解決手段】開示される、本発明の一実施形態による、半導体装置の製造方法によれば、ライン・アンド・スペース状の第2の層12を、第2の層12が延在する方向と交わる方向に延びるライン・アンド・スペース状の第8の層25をマスクとしてエッチングすることにより、二次元的に配列される第2の層12を得、これにより下地層をエッチングすることにより、二次元的に配列されるピラーを形成することができる。

(もっと読む)

半導体素子の製造方法

【課題】パターニングされた被エッチング膜のシリサイド化を簡便に行うことのできる半導体素子の製造方法を提供する。

【解決手段】本発明の半導体素子の製造方法は、ポリシリコン膜21上にSiO2 膜22をパターンニングし、SiO2 膜22を覆うようにポリシリコン膜23を堆積した後、SiO2 膜22の側壁部分にポリシリコン電極23aを形成する。次いで、SiO2 膜22を除去した後、堆積したSiO2 膜24をエッチバックして電極23aの側壁部にSiO2 からなるサイドウォール24aを形成する。次いで、サイドウォール24aの間にポリシリコンを埋め込むことによってポリシリコン電極23bを形成し、サイドウォール24aを除去して、ポリシリコン膜21およびポリシリコン電極23a,23bをエッチバックすることでポリシリコン膜21をパターンニングする。

(もっと読む)

141 - 160 / 525

[ Back to top ]