Fターム[5F004EA12]の内容

半導体のドライエッチング (64,834) | パターン形成手法 (4,711) | サイドウォール (408) | 残留形成 (91)

Fターム[5F004EA12]に分類される特許

61 - 80 / 91

自己組織化材料を使用するピッチマルチプリケーション

ブロック共重合体などの自己組織化材料は、ピッチマルチプリケーションのためのマンドリル(162)として使用される。共重合体は、基板(110)上に堆積され、所望のパターンへと自己組織化を促される。ブロック共重合体を形成するブロックのうちの一つ(164)は、選択的に除去される。残っているブロックは、ピッチマルチプリケーションのためのマンドリル(162)として使用される。スペーサ材料は、ブロック(162)上にブランケット堆積される。スペーサ材料は、マンドリル(162)の側壁上にスペーサを形成するために、スペーサエッチングに暴露される。マンドリル(162)は、独立したスペーサを残すために選択的に除去される。スペーサは、下部基板(110)内にパターンを画定するために、ピッチ増倍化マスク機構として使用されうる。  (もっと読む)

(もっと読む)

半導体素子のハードマスクパターン形成方法

【課題】半導体素子のハードマスクパターン形成方法に関するものであり、露光装備の解像力以下のピッチを有するマスクを形成し得る半導体素子のハードマスクパターン形成方法を提供する。

【解決手段】半導体素子のハードマスクパターン形成工程時に露光工程を用いたフォトレジストパターンを用いて第1のハードマスクパターン103を形成し、第1のハードマスクパターンを含む全体構造上に分離膜104を形成した後、第1のハードマスクパターンの間の空間に第2のハードマスクパターンを形成して露出される分離膜をエッチング除去することにより、露光装備の解像力以下のピッチを有するマスクを形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】本発明は、パターン形成時のパターン不良発生を防止してライン・アンド・スペースが的確に形成される半導体装置を提供することを目的とする。

【解決手段】複数のトランジスタを有する少なくとも2個のトランジスタブロックと、前記複数のトランジスタにそれぞれ接続された複数のゲートと、を有し、前記複数のゲートは、概略U字型の開ループ形状を有し、前記トランジスタブロック内に配置される前記複数のゲートは、隣接する2個のトランジスタブロック間で、それぞれ前記開ループ形状の開口部が対向して対称的に配置されることを特徴とする半導体装置。

(もっと読む)

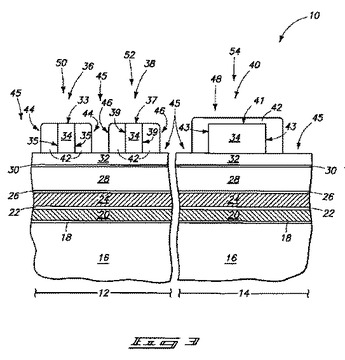

多重チャネルを有する半導体素子及びその製造方法

【課題】本発明は、ゲート電極を形成する以前に半導体基板の活性領域の形態を変化させて多数のチャネルを有するようにする。

【解決手段】本発明は、素子分離膜が形成された半導体基板、半導体基板の活性領域内に形成された多数のトレンチ及びそれぞれのトレンチ領域内の対向する側壁を連結し、表面がチャネル領域として用いられるチャネル活性領域を含む多重チャネルを有する半導体素子からなる。

(もっと読む)

半導体装置及びその製造方法

【課題】メモリセルアレイ領域となるリソグラフィの解像限界以下の直線部と、その直線部を接続する接続部とを有するソース・ドレイン拡散層を簡易に形成することが可能な半導体装置の製造方法を提供する。

【解決手段】シリコン窒化膜50上に第1ハードマスク60、X軸方向に直線状に延びる第2ハードマスク70を複数並列して形成する。次に、第2ハードマスク70のヒンジ領域Hにイオン注入しエッチングレートを変化させる。次に、第2ハードマスク70をマスクとして第1ハードマスク60をエッチングし、イオン注入されていない第2ハードマスク70のみエッチング除去する。次に、第1ハードマスク60に側壁膜80を形成し、第2ハードマスク70に覆われていない第1ハードマスク60をエッチング除去する。そして、側壁膜80及び第1ハードマスク60をマスクとしてシリコン窒化膜50をエッチング除去する。

(もっと読む)

半導体構造、複数のラインを形成する方法、および高密度構造と低密度構造を単一フォトマスクで形成する方法

いくつかの実施形態は、犠牲材料に沿ったポリマースペーサーの形成、犠牲材料の除去、および集積回路の製造中におけるマスクとしてのポリマースペーサーの利用、を含む。ポリマースペーサーマスクは、例えばフラッシュメモリアレイのフラッシュゲートをパターン化するために利用されてもよい。いくつかの実施形態では、ポリマーは大きな犠牲構造と小さな犠牲構造にわたって同時に形成される。ポリマーは、小さな犠牲構造にわたってよりも、大きな犠牲構造にわたっての方が厚く、こうした厚さの差を利用して、高密度構造と低密度構造を単一フォトマスクで製造する。  (もっと読む)

(もっと読む)

半導体素子のパターン形成方法

【課題】ポリシリコン物質と酸化物質との間の食刻選択比を利用したパターン形成方法の提供。

【解決手段】半導体基板100の被食刻層上にハードマスク層、第1酸化膜パターン、その上に窒化膜パターンを形成、ハードマスク層を選択的に露出,ハードマスク層,第1酸化膜及び窒化膜パターンの露出部分上に第1厚の第1ポリシリコン層,第1ポリシリコン層上に第2厚の第2酸化膜,第2酸化膜上に第3厚の第2ポリシリコン層を形成。窒化膜パターンの露出まで第2ポリシリコン層,第2酸化膜及び第1ポリシリコン層を平坦化。窒化膜パターンを除去し第1酸化膜パターンを露出。酸化物・ポリシリコン間の食刻選択比に従い第1酸化膜パターンと第2酸化膜を食刻。第1ポリシリコン層と第2ポリシリコン層を食刻マスクにハードマスク層を食刻してハードマスク層パターンを形成し,ハードマスク層パターンをマスクに被食刻層を食刻して微細パターン110aを形成。

(もっと読む)

電子装置の製造方法および半導体装置の製造方法

【課題】露光装置の解像限界を超えた微細なパターンを有するDRAMやFeRAMおよびクロスバー素子等の電子装置の製造方法を提供する。

【解決手段】基板10上にダミー11膜を基板10上の素子領域10Aおよびその外側の外部領域10Bを覆うように形成してパターニングし、ダミーパターン11を素子領域10Aにおいては第1の高さH1に、外部領域10Bにおいては第1の高さH1よりも小さい第2の高さH2を有するように形成し、基板10上に別の膜12をダミーパターン11A,Bを覆うように形成し、膜12を異方性エッチングして素子領域中のダミーパターン11Aの側壁面に沿って第1および第2のパターン12A、Bを形成し、かつ、外部領域10Bにおいては膜12消失させ、素子領域10Aにおいて、第1および第2のパターン12A,Bを使って電子装置を形成する。

(もっと読む)

微細ピッチのハードマスクパターンの形成方法及びそれを用いた半導体素子の微細パターン形成方法

【課題】 フォトリソグラフィ工程での解像限界を超える微細ピッチのパターン形成を実現可能とする、微細ピッチのハードマスクパターンの形成方法を提供する。

【解決手段】基板上に第1ハードマスク層を形成する。第1ハードマスク層20上に複数の第1犠牲パターンを形成し、第1犠牲パターンのうち相互隣接した2個の第1犠牲パターン間にリセスの形成された上面を有する第2ハードマスク40層を形成し、リセス内に第2犠牲パターンを形成する。第1犠牲パターンの上面を露出させて第1及び第2犠牲パターンを除去する。第2ハードマスク層40の上部をエッチングマスクとして第2及び第1ハードマスク層40及び20をエッチングしハードマスクパターン60を形成する。ハードマスクパターン60をエッチングマスクとして利用し半導体素子の微細パターンを形成する。

(もっと読む)

半導体装置の製造方法

【課題】ドライエッチングを用いて絶縁膜等の被加工膜の高精度加工を行うことのできる半導体装置の製造方法を提供する。

【解決手段】半導体基板上に第1の膜厚を有する被加工膜を形成する工程と、前記被加工膜の一部を加工して、前記第1の膜厚よりも薄い第2の膜厚を有する領域を形成する工程と、プラズマの特性値の変化をモニターしながら、前記第2の膜厚を有する領域が形成された前記被加工膜をドライエッチングにより加工する工程と、前記プラズマの特性値の変化から、前記被加工膜の前記第2の膜厚を有する領域の直下の部材が露出し始める第1のタイミングを検知する工程と、前記第1のタイミングに基づいて、前記被加工膜の前記第1の膜厚を有する領域の直下の部材が露出する直前の第2のタイミングを予測し、前記第2のタイミングで前記ドライエッチングのエッチング条件を変更する工程と、

を含むことを特徴とする半導体装置の製造方法。

(もっと読む)

半導体素子の微細パターン形成方法

【課題】リソグラフィー限界以上のピッチを有する微細パターンを形成する製造方法を提供する。

【解決手段】被食刻層13を有する半導体基板11上に化学増幅型フォトレジストパターン15を形成し、この上にシリコン含有ポリマーをスピンコーティングする。露光、ベークしフォトレジストパターンとシリコン含有ポリマーの界面に架橋結合層19を形成する。これを現像し架橋結合がなされていないシリコン含有ポリマーを除去し、フォトレジストパターンの周辺のみに架橋結合層を形成する。フォトレジストパターンの上部が露出するまで架橋結合層をエッチバックし、フォトレジストパターンの側壁に架橋結合層を残す。フォトレジストパターンを除去して架橋結合層からなる微細パターンとする。これを食刻マスクにして被食刻層をパターニングする。

(もっと読む)

高アスペクト比ビアエッチング

【課題】基板に高アスペクト比のビアをパターニングする方法を提供する。特に、高アスペクト比の深いビアまたはビアをパターニングして、ハードマスクのアンダーカットを無くしたドライエッチング方法を提供する。

【解決手段】3次元の積層半導体装置および/または構造に使用される、深い穴を基板に形成することを目的とする。特に、スムースなビア側壁と、メタライゼーションを可能とする十分な傾斜を備えた、アスペクト比が10までの深いビアをSi基板にパターニングすることを目的とする。

(もっと読む)

半導体装置の多層金属配線の形成方法

【課題】金属スペーサを用いて金属配線の特性向上及びオーバラップマージンを改善できる多層金属配線の形成方法を提供する。

【解決手段】下層上に第1金属配線を形成する段階、前記第1金属配線を含む下層上に第1絶縁膜を形成する段階、前記第1絶縁膜をエッチングして前記第1金属配線の高さより低いように段差を形成する段階、前記第1絶縁膜上の第1金属配線の側壁に金属スペーサを形成する段階、前記金属スペーサを含む下層上に平坦化膜を形成する段階、前記平坦化膜をエッチングして前記第1金属配線が露出するようにコンタクト孔を形成する段階、及び、前記コンタクト孔を介して第1金属配線とコンタクトする第2金属配線を形成する段階を備えることを特徴とする。

(もっと読む)

半導体装置及びその製造方法

【課題】リソグラフィの解像限界以下の配線パターンと、それ以外の任意の寸法の配線パターン等を簡易に形成することが可能な半導体装置の製造方法を提供する。

【解決手段】被エッチング部材であるポリシリコン膜25上に第1ハードマスク30が形成され、更にこの上にアモルファスシリコンからなる第2ハードマスク40が形成される。第2ハードマスク40の所望の一部にボロン等のイオン注入を行った後、第2ハードマスク40をマスクとして第1ハードマスク30をエッチングする。ウエットエッチングにより第2ハードマスク40のイオン注入されていない部分をエッチング除去する。第1ハードマスク30の側壁に側壁膜70を形成した後、第2ハードマスク40に覆われず上部が露出している第1ハードマスク30を選択的にエッチング除去する。

(もっと読む)

ピッチの低減

【課題】ピッチの低減

【解決手段】エッチング層内に特徴を設けるための方法が提供される。エッチング層の上に、犠牲特徴を有する犠牲パターン形成層が提供される。犠牲特徴内に、共形側壁が形成される。これは、少なくとも2サイクルの側壁形成プロセスを含み、各サイクルは、側壁デポジション段階および側壁プロファイル成形段階を含む。共形側壁間の犠牲パターン形成層は、除去され、犠牲パターン形成層の部分を選択除去されたところの共形側壁間にギャップを有するような共形側壁が残される。共形側壁をエッチングマスクとして使用して、エッチング層内に特徴がエッチングされる。このとき、エッチング層内の特徴は、犠牲パターン形成層の部分を選択除去されたところの共形側壁間のギャップを通してエッチングされる。

(もっと読む)

シリコンに対する誘電材料の選択エッチング方法及びシステム

ドライプラズマエッチングシステム内で誘電体層をシリコン及びポリシリコンに対して選択的な均一エッチングを行う方法及びシステムが記載されている。エッチング用化学は、たとえばCH2F2やCHF3のようなフルオロハイドロカーボンを有する。高いエッチング選択性及び受容可能な均一性は、CH2F2の流速やドライプラズマエッチングシステムと結合する出力を含むプロセス条件を選択することによって実現されて良い。それにより、エッチングプラズマ中での活性エッチングラジカルとポリマー生成ラジカルとの適切なバランスがとられる。  (もっと読む)

(もっと読む)

半導体素子の微細パターン形成方法

【課題】 CD制御を可能にし且つセルのライン間のスペースを異にするための半導体素子の微細パターン形成方法の提供。

【解決手段】 半導体基板の上部に第1酸化膜、下部反射防止膜及び第1感光膜パターンを形成した後、前記第1感光膜パターンをマスクとして前記下部反射防止膜及び前記第1酸化膜をエッチングする段階と、前記第1感光膜パターン及び前記下部反射防止膜を除去した後、全体構造の上部に窒化膜を蒸着する段階と、前記窒化膜を全面エッチングして前記第1酸化膜の側壁にスペーサを形成する段階と、全体構造の上部に第2酸化膜を蒸着した後、研磨して平坦化させる段階と、全体構造の上部に第2感光膜パターンを形成した後、前記第2感光膜パターンをマスクとして前記窒化膜を除去して酸化膜パターンを形成する段階とを含む、半導体素子の微細パターン形成方法を提供する。

(もっと読む)

半導体装置及びその製造方法

【課題】 接続孔での接続信頼性を向上させることができる半導体装置の製造方法を提供する。

【解決手段】本発明に係る半導体装置の製造方法は、第1の絶縁膜10上に配線20を形成する工程と、第1の絶縁膜10上及び配線20上に、第2の絶縁膜30を形成する工程と、第2の絶縁膜30に、配線20上に位置する接続孔30aを形成する工程と、接続孔30aの底に位置する配線20をスパッタリングすることにより、接続孔30aの側面に被覆膜31を形成する工程と、第2の絶縁膜30上及び被覆膜31上にバリア膜41を形成する工程と、接続孔30aに導電膜42を埋め込む工程とを具備する。

(もっと読む)

相互接続構造体及びその製造方法

【課題】 改善された拡散障壁で覆われた相互接続構造体を提供すること。

【解決手段】 ダマシン配線及び該配線を形成する方法である。この方法は、誘電体層の上面にマスク層を形成するステップと、マスク層内に開口部を形成するステップと、誘電体層がマスク層によって保護されていない誘電体層内に、トレンチを形成するステップと、マスク層の下でトレンチの側壁を凹ませるステップと、トレンチ及びマスク層の全ての露出面上に、共形の導電性ライナを形成するステップと、トレンチをコア導電体で充填するステップと、誘電体層の上面の上に延びている導電性ライナの部分を除去し、マスク層を除去するステップと、コア導体の上面に導電性キャップを形成するステップとを含む。この構造体は、導電性ライナ内のコア導体クラッドと、導電性ライナで覆われていないコア導体の上面と接触している導電性キャップ層と、を含む。

(もっと読む)

半導体装置構造および半導体装置の製造方法

【課題】 塗布絶縁膜からの脱ガス反応を押さえ、塗布絶縁膜の変形やクラック等を回避して半導体装置としての信頼性向上をはかる。

【解決手段】 ヒューズ素子の側壁部もしくはそれを覆う絶縁談をテーパ形状に加工することにより、ヒューズ素子の近隣に存在する塗布絶縁膜との距離を大きくすることで塗布絶縁膜へ加わる熱ストレスを緩和し、塗布絶縁談からの脱ガス反応を押さえ塗布絶縁談の変形やクラック等を避ける。また、ヒューズ素子の側壁部もしくはそれを覆う絶縁膜にサイドスペーサを形成し、あるいはヒューズ素子の側壁部とさらにそれを覆う絶縁談にもサイドスペーサを形成することにより、一層、ヒューズ素子の近隣に存在する塗布絶縁膜との距離を大きくする。

(もっと読む)

61 - 80 / 91

[ Back to top ]