Fターム[5F032AA09]の内容

素子分離 (28,488) | 絶縁物を用いる分離 (9,448) | 素子領域側面、底面を絶縁物で分離するもの (1,104) | 絶縁物上に素子領域を成長させるもの (91)

Fターム[5F032AA09]の下位に属するFターム

単結晶絶縁物を用いるもの(例;SOS) (16)

Fターム[5F032AA09]に分類される特許

1 - 20 / 75

半導体装置およびその製造方法

半導体装置およびその製造方法

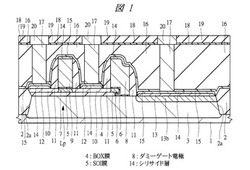

【課題】隣接するSOI領域とバルクシリコン領域とが短絡することを防止する。

【解決手段】一つの活性領域内にSOI領域およびバルクシリコン領域が隣接する半導体装置において、それぞれの領域の境界にダミーゲート電極8を形成することにより、BOX膜4上のSOI膜5の端部のひさし状の部分の下部の窪みにポリシリコン膜などの残渣が残ることを防ぐ。また、前記ダミーゲート電極8を形成することにより、それぞれの領域に形成されたシリサイド層14同士が接触することを防ぐ。

(もっと読む)

半導体装置及びその製造方法

【課題】動作速度を向上し消費電力を低減しうる半導体装置及びその製造方法を提供する。

【解決手段】半導体基板に第1の領域を画定する第1の素子分離絶縁膜と、半導体基板の第1の領域に形成された第1導電型の第1の導電層と、半導体基板上に形成され、第1の領域の一部である第2の領域に第1の導電層に接続して形成された第1導電型の第2の導電層と、第1の領域の他の一部である第3の領域に第1の導電層に接続して形成された第1導電型の第3の導電層とを有する半導体層と、半導体層内に設けられ、第2の導電層と第3の導電層とを分離する第2の素子分離絶縁膜と、第2の導電層上に形成されたゲート絶縁膜と、ゲート絶縁膜上に形成され、第3の導電層を介して第1の導電層に電気的に接続されたゲート電極とを有する。

(もっと読む)

半導体装置およびその製造方法

【課題】トレンチ構造の表面に不要な溝が形成されず、また、素子の面積効率を良好なものとすることができる半導体装置の製造方法の提供。

【解決手段】トレンチ内にポリシリコンが充填され、当該ポリシリコンの上部がシリコン酸化膜により覆われたトレンチ構造を有する半導体装置の製造方法であって、シリコン活性層の上面に第1のシリコン酸化膜が積層されてなる基板に異方性エッチングを行うことにより、上記第1のシリコン酸化膜の上面から上記シリコン活性層内に伸びるトレンチを形成するトレンチ形成工程と、上記トレンチの側壁全体を一体的に覆う第2のシリコン酸化膜を形成する側壁酸化膜形成工程と、上記第2のシリコン酸化膜の形成後に、上記トレンチ内にポリシリコンを充填する充填工程と、上記トレンチ内に充填したポリシリコンの上部露出面を酸化させてキャップを形成するキャップ形成工程と、を備える。

(もっと読む)

半導体装置及びその製造方法

【課題】SOI構造のフラッシュメモリーの提供

【解決手段】

半導体基板1上にシリコン窒化膜2及びシリコン酸化膜3が選択的に設けられ、シリコン酸化膜3上には、選択的に横(水平)方向エピタキシャルSi層5が設けられ、Si層5の両側面には、それぞれ側面を接して横(水平)方向エピタキシャルSi層6が設けられた構造からなる半導体層が素子分離領域のシリコン窒化膜4により絶縁分離されている。Si層6の残りの周囲には第1のゲート酸化膜10を介して包囲型フローティングゲート電極11が設けられ、包囲型フローティングゲート電極11の周囲には第2のゲート酸化膜12を介して包囲型コントロールゲート電極13(ワード線)が設けられ、Si層5には概略ソースドレイン領域9が設けられている2重包囲型ゲート電極を有するMIS電界効果トランジスタより構成したフラッシュメモリー。

(もっと読む)

固体撮像装置及びその製造方法、電子機器

【課題】画素分離部の幅を縮小することや光電変換部の面積の拡大することを可能にする固体撮像装置を提供する。

【解決手段】第1導電型の電荷蓄積領域23を含む光電変換部及び画素トランジスタTr1から成る画素38と、画素38が複数配列された画素領域と、この画素領域内の隣接する画素38間の半導体層22に設けられたトレンチ42の内壁部に形成された、エピタキシャル成長による第1導電型の半導体層43と、この第1導電型の半導体層43の内部に形成され、隣接する画素38の電荷蓄積領域23を分離する、画素分離部41とを含んで、固体撮像装置21を構成する。

(もっと読む)

半導体の製造方法及び半導体装置

【課題】複雑な工程を経ることなく、通常の半導体製造装置を使用して、低コストで、半導体装置の、低電圧動作、高集積性を実現する。

【解決手段】次の工程(1)〜(5)で半導体装置を製造する。(1)シリコン結晶製の半導体支持基板の表面を洗浄し、酸化被膜を除去して、結晶面を露出させる工程、(2)該結晶面上に高誘電率非晶質薄膜を低温で堆積する工程、(3)該高誘電率非晶質薄膜の結晶化開始温度よりも低いプレアニール温度で該高誘電率非晶質薄膜をプレアニールする工程、(4)該半導体支持基板を選択的に急速加熱することにより該高誘電率非晶質薄膜内部に基板界面から該薄膜表面方向に向けて温度が低くなる急峻な温度勾配を形成することにより該高誘電率非晶質薄膜を結晶化して、エピタキシャル薄膜を形成する工程、(5)該エピタキシャル薄膜の上面に半導体結晶の配向膜を形成する工程を有する。

(もっと読む)

半導体装置およびその製造方法

【課題】埋め込み絶縁層により活性層と支持基板とが電気的に絶縁された半導体基板において、支持基板の電位を活性層の表面から取り出すための基板コンタクトの低抵抗化を図ることができる半導体装置およびその製造方法を提供すること。

【解決手段】活性層16に素子領域4およびコンタクト領域5が形成された厚膜SOI基板2において、CMOSトランジスタ7のB/L層29およびL/I層37、npnバイポーラトランジスタ8のコレクタ層49と同一層に、n型基板コンタクト12の貫通コンタクト58を取り囲むn型コンタクト埋め込み層57を形成する。

(もっと読む)

埋め込みドープ層を有する完全空乏型SOIデバイス

【課題】完全空乏型SOIデバイスの製造に適したセミコンダクタオンインシュレータ(SeOI)ウェーハおよびそれを用いたデバイスを提供すること。

【解決手段】本発明は、第1の基板の表面領域にドープ層、ドープ層上に埋め込み酸化物層、埋め込み酸化物層上に半導体層を形成してSeOIウェーハを得る。SeOIウェーハの第2の領域の埋め込み酸化物層および半導体層を維持しながらSeOIウェーハの第1の領域から埋め込み酸化物層および半導体層を除去し、第2の領域に上部トランジスタを形成する。第1の領域にリセスチャネルアレイトランジスタを形成し、第2の領域にpチャネルトランジスタおよび/またはnチャネルトランジスタを形成する。ドープ層内またはこの近傍にバックゲートを形成し、第1の領域にリセスチャネルアレイトランジスタを形成し、ドープ層内またはその近傍にソース領域およびドレイン領域を形成する。

(もっと読む)

半導体装置

【課題】デカップリング容量及びガードリング等のノイズを低減する構造物を設けるための専用配置領域を必要としない半導体集積回路装置を提供する。

【解決手段】P−型シリコンからなる支持基板2を設け、この支持基板2上にP+型シリコン層3を設け、その上にN+型シリコン層4及びP+型シリコン層12を相互に同層に設ける。P+型シリコン層3及びN+型シリコン層4の不純物濃度は支持基板2の不純物濃度よりも高くする。また、N+型シリコン層4及びP+型シリコン層12上の全面に、埋込酸化膜5及びSOI層6を設ける。そして、P+型シリコン層3を接地電位配線GNDに接続し、N+型シリコン層4を電源電位配線VDDに接続する。これにより、P+型シリコン層3とN+型シリコン層4との間に、電源に並列に接続されたデカップリング容量C1が形成される。

(もっと読む)

半導体装置の製造方法

【課題】ソース/ドレイン領域と基板との間の容量の低下を防止でき、パンチスルー現象を低減することができる半導体装置の製造方法を提供する。

【解決手段】本発明の半導体装置の製造方法は、半導体基板上に第1絶縁膜を介してゲート電極を形成する工程と、前記ゲート電極の上面及び側面を覆う第2絶縁膜を形成する工程と、前記第2絶縁膜をマスクとして前記半導体基板の表面に溝部を形成する工程と、前記溝部の底面上に、該溝部の側壁の上部の露出を残す厚さで第3絶縁膜を形成する工程と、前記露出された溝部の側壁の上部を起点としたエピタキシャル成長により、前記第3絶縁膜上に前記半導体のエピタキシャル層を形成する工程と、前記エピタキシャル層に不純物を導入してソース/ドレイン領域を形成する工程と、を有することを特徴とする

(もっと読む)

CMOS用歪トランジスタの集積化

【課題】n型MOSデバイス(NMOS)の電子の移動度の向上、およびp型MOSデバイス(PMOS)のホールの移動度の向上した半導体装置および製造方法の提供。

【解決手段】(1)選択的に蒸着されたシリコン材料が、第1の領域における傾斜シリコンゲルマニウム基板材料の格子面間隔より小さい、シリコン材料の格子面間隔によって引き起こされる引っ張り歪を経験するべく、傾斜シリコンゲルマニウム基板の第1の領域上に選択的に蒸着されたシリコン材料のNMOSチャンネル、および(2)選択的に蒸着されたシリコンゲルマニウム材料が、第2の領域における傾斜シリコンゲルマニウム基板の格子面間隔よりも大きい、選択的に蒸着されたシリコンゲルマニウム材料の格子面間隔によって引き起こされる圧縮歪を経験すべく、基板の第2の領域上に選択的に蒸着されたシリコンゲルマニウム材料のPMOSチャンネルを有する。

(もっと読む)

半導体装置、半導体装置の製造方法、半導体基板、および半導体基板の製造方法

【課題】化合物半導体と絶縁性材料との界面に形成される界面準位が低減した半導体装置を提供する。

【解決手段】閃亜鉛鉱型の結晶構造を有する3−5族化合物半導体と、3−5族化合物半導体の(111)面、(111)面と等価な面、または、(111)面もしくは(111)面と等価な面から傾いたオフ角を有する面に接する絶縁性材料と、絶縁性材料に接し、金属伝導性材料を含むMIS型電極とを備える半導体装置を提供する。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】結晶欠陥が少なく結晶性の高い単結晶シリコン層が絶縁膜上に形成されてなる半導体装置の製造方法及び半導体装置を得るという課題があった。

【解決手段】基板1の一面1aに絶縁膜2を形成する工程と、絶縁膜2を開口して基板1を露出させる穴2cを形成する工程と、穴2cの内壁面を覆うように結晶成長補助膜3を形成する工程と、穴2cを充填するとともに、絶縁膜2の前記基板と反対側の面2aを覆うように非結晶シリコン層を形成する工程と、前記非結晶シリコン層を、レーザーアニール法により単結晶シリコン層5とする工程と、を有する半導体装置101の製造方法を用いることにより、上記課題を解決できる。

(もっと読む)

半導体装置及びその製造方法

【課題】半導体部材が単結晶の半導体材料からなり、特性が良好な半導体装置及びその製造方法を提供する。

【解決手段】単結晶のシリコンからなるシリコン基板11上に絶縁膜12を形成し、絶縁膜12に開口部12aを形成し、絶縁膜12上に開口部12aを介してシリコン基板11と接触するようにアモルファスシリコン膜を形成し、このアモルファスシリコン膜をシリコン基板11を起点として固相エピタキシャル成長させて、その後パターニングする。これにより、開口部12aの直上域から外れた領域の一部に、単結晶のシリコンからなるシード層を形成する。次に、このシード層を覆うようにアモルファスシリコン膜を堆積させ、このアモルファスシリコン膜をシード層を起点として固相エピタキシャル成長させて、単結晶シリコン膜を形成する。そして、この単結晶シリコン膜をパターニングすることにより、シリコンピラー33を形成する。

(もっと読む)

半導体装置

【課題】コンタクト抵抗が低い半導体装置を提供する。

【解決手段】半導体装置は、第1導電型の半導体基板と、埋め込み酸化膜と、第2導電型の半導体層と、を備えるSOI基板に作られ、前記埋め込み酸化膜は、自己に穿設された、前記半導体基板と前記半導体層とを連通する、第1の開口を有し、前記半導体基板は、その表面部分に埋め込み状態に形成され、前記第1の開口内の前記半導体層の埋設部と互いに電気的に接続している、第2導電型の接続層を有し、前記半導体層及び前記埋め込み酸化膜を貫通して、前記接続層の表面部分に至る第2の開口内に埋め込まれて、側面において前記半導体層と電気的に接続し、底面において前記接続層と電気的に接続する、コンタクト電極と、を備える。

(もっと読む)

半導体装置及びその製造方法

【課題】高集積、高速且つ高性能な歪みSOI構造の縦型MISFETを得ること。

【解決手段】Si基板1上に酸化膜2を介して、横方向エピタキシャルSiGe層3が設けられ、SiGe層3は素子分離領域形成用の埋め込み絶縁膜4及び酸化膜2により島状に絶縁分離されている。SiGe層3上には選択的に縦方向エピタキシャルSiGe層7が設けられ、SiGe層7の側面には格子定数がやや小さい横方向エピタキシャル歪みSi層8が周設され、歪みSOI基板を形成しており、SiGe層7及び歪みSi層8の上部にはドレイン領域(10、11)が設けられ、SiGe層3全体、SiGe層7及び歪みSi層8の下部にはソース領域9が設けられ、歪みSi層8の側面にはゲート酸化膜12を介してゲート電極13が周設され、ドレイン領域11、ソース領域9及びゲート電極13には、それぞれ導電プラグ20を介してCu配線23が接続されている歪みSOI構造の縦型のMISFETを構成すること。

(もっと読む)

SRAMデバイスにおけるHOTプロセスSTIおよび製造方法

【課題】H0T(ハイブリッド配向技術)プロセスおよび個々のデバイス間のSTI(シャロウトレンチアイソレーション領域)の組み合わせを使用して、同じ集積回路上のSRAMおよびロジック回路を提供する。

【解決手段】STIを備えたHOT基板上に複数のSRAM(1208)が形成され、さらに、複数のロジック回路が、複数のSOI(1202)領域上の一部のデバイスおよび複数のSOI(1202)領域上の他のデバイスと共に同じチップ上に形成される。

(もっと読む)

半導体構造の製造方法およびこの方法により得られる半導体構造

好ましい実施形態において、本発明は、半導電性支持体と、支持体の一部分上に配置された絶縁層と、絶縁層上に配置された半導電性表層とを有する半導体構造を提供する。表層と、絶縁層により覆われていない基板の半導電性バルク領域の露出部分とに電子デバイスが形成され得る。本発明はまた、連続した絶縁層上に配置された半導電性表層を含み、半導電性支持体上に両層が配置された基板から始まり、基板の露出された半導電性バルク領域を形成するように基板の少なくとも1つの選択領域を変形することによって、このような半導体構造を作製する方法を提供する。 (もっと読む)

半導体装置及びその製造方法

【課題】貼り合わせSOI基板を使用せずに容易な製造プロセスにより、微細で、高速且つ高性能なMIS電界効果トランジスタを提供する。

【解決手段】半導体基板1上に酸化膜2を介して、横方向エピタキシャル半導体層3が設けられ、素子分離領域形成用の埋め込み絶縁膜4及び酸化膜2により島状に絶縁分離されている。絶縁分離された横方向エピタキシャル半導体層3上に選択的に縦方向エピタキシャル半導体層7が設けられ、上部には高濃度ドレイン領域10及び低濃度ドレイン領域9が設けられ、下部には高濃度ソース領域8が設けられ、側面にはゲート酸化膜11を介してゲート電極12が設けられている。高濃度ドレイン領域10、高濃度ソース領域8及びゲート電極12には、それぞれバリアメタル18を有する導電プラグ19を介してバリアメタル21を有するCu配線22が接続されている。

(もっと読む)

1 - 20 / 75

[ Back to top ]