Fターム[5F032AA32]の内容

素子分離 (28,488) | 絶縁物を用いる分離 (9,448) | 素子領域側面を絶縁物で分離するもの (8,208) | 溝内埋込み分離 (7,414)

Fターム[5F032AA32]の下位に属するFターム

溝の断面形状 (2,101)

埋込み材料 (3,229)

溝内の導電層に電位を与えるもの (55)

溝堀りに工夫(DAで具体的に) (344)

埋込みに工夫 (1,675)

Fターム[5F032AA32]に分類される特許

1 - 10 / 10

固体撮像装置および固体撮像装置の製造方法

【課題】本発明の一つの実施形態の目的は、素子分離特性を向上可能な固体撮像装置および固体撮像装置の製造方法を提供することである。

【解決手段】実施形態によれば、固体撮像装置の製造方法が提供される。固体撮像装置の製造方法は、素子分離領域形成工程と、電荷蓄積領域形成工程とを含む。素子分離領域形成工程では、第1導電型の半導体層をエピタキシャル成長させて光電変換素子間を分離する素子分離領域を形成する。電荷蓄積領域形成工程では、第2導電型の半導体層をエピタキシャル成長させて前記光電変換素子における電荷蓄積領域を形成する。

(もっと読む)

窒化ガリウム半導体装置およびその製造方法

【課題】回路全体の小型化を実現し、高温環境下で使用することができる窒化ガリウム半導体装置およびその製造方法を提供すること。

【解決手段】半導体基板1の表面には、絶縁層2、アンドープの第1GaN層3、AlGaN層4がこの順で積層されている。第1GaN層3とAlGaN層4の界面には、2次元電子ガスで形成された表面障壁層5が形成されている。AlGaN層4の表面層には、第1GaN層3に達し、かつ貫通しない程度の凹部(第1凹部)が形成されている。このような半導体基板1に、第1高耐圧トランジスタ110および制御回路120が一体的に形成されている。第1高耐圧トランジスタ110は、第1凹部およびAlGaN層4の表面に形成されている。また、制御回路120は、第1凹部の一部に形成されたnチャネルMOSFETと、AlGaN層4の表面に形成されたデプレッション型nチャネルMOSFETとで構成されている。

(もっと読む)

半導体素子の形成方法

【課題】 フォトリソグラフィ工程を用いることなく広い領域に単結晶半導体領域を有する半導体素子の形成方法を提供する。

【解決手段】 第1基板150上に互いに離隔するように配置されるボンディング表面を形成する。第1基板150のボンディング表面に第2基板100を接合する。その後、第1基板100の上部面に互いに離隔するように配置されたボンディング表面のそれぞれに第2基板100から各半導体領域が残るように第2基板100を分離する。前記ボンディング表面は、第1基板150上に少なくとも一つの絶縁領域の表面を含む。そして、少なくとも一つのアクティブ領域は、前記少なくとも一つの半導体領域内に形成される。素子分離領域は、少なくとも一つの前記半導体領域と隣接するように形成される。これにより、別途、フォトリソグラフィ工程を行わずに済み、工程が簡略化される。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】本発明は、先に形成されている絶縁膜(例えば、ゲート絶縁膜など)の品質に悪影響を及ぼさず、また、欠陥が少ない絶縁膜をトレンチに埋め込むことができる半導体装置の製造方法および半導体装置を提供する。

【解決手段】反応ガスを分解して基板のトレンチに絶縁膜の埋め込みを行う工程を備えた半導体装置の製造方法であって、前記反応ガスと、少なくともD2(重水素)ガスを含む希釈ガスとを供給して、前記絶縁膜の埋め込みを行うことを特徴とする半導体の製造方法が提供される。

(もっと読む)

半導体装置の製造方法

【課題】装置構成に合わせて、最終的なゲート電極の寸法が均一になるように複数の工程を管理して、ゲート電極の加工寸法のウエハ面内ばらつきを最小化することができる製造技術を提供する。

【解決手段】第1のプロセス装置101と、1つ以上後の第2のプロセス装置111とを有する半導体製造システムを用い、プロセス装置101で処理されたウエハ105の計測データを基に、ウエハ上に形成された薄膜膜厚もしくは構造体の高さがウエハ面内で均一になるように、プロセス装置111におけるウエハ115の処理方向を制御する。すなわち、ゲート寸法のモデル式にしたがいゲート電極の下地構造形成時のウエハ処理方向を制御(または素子分離等の下地構造を考慮して露光装置においてレジスト転写形成時にショット毎にドーズ量を制御)することで、エッチング加工後のゲート長をウエハ面内で均一化する。

(もっと読む)

半導体装置およびその製造方法

【課題】基板断面の縦方向における耐圧を改善し、700V以上の高い耐圧を有する半導体装置およびその製造方法を提供する。

【解決手段】埋め込み酸化膜3上にあるSOI層1aの表層部に、横型MOSトランジスタ(LDMOS)が形成されてなる半導体装置10であって、シリコン(Si)より誘電率の低い低誘電率領域5が、埋め込み酸化膜3に当接して、LDMOSのソースSとドレインDの間で形成されてなる半導体装置とする。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】コンタクトレス方式が採用されたメモリセルアレイにおける共用コンタクト領域においてリーク電流を抑制する。

【解決手段】不揮発性半導体記憶装置は、複数の埋め込み拡散ビット線2と、埋め込み酸化膜と、複数のワード線5と、ワード線5とビット線2間領域との交差領域に形成された電荷保持膜からなる複数のメモリセルと、コンタクト7を上面に有する複数の拡散層8があり、複数のブロックに区分されたビット線2同士は拡散層8を介して電気的に接続されており、コンタクト領域となる拡散層8の近傍領域に形成されたビット線2間に形成された素子分離領域9とを備える。さらに、ビット線2上及び素子分離領域9上に跨り、側壁絶縁膜を有するダミーワード線14を備え、側壁絶縁膜は、素子分離領域9と、埋め込み酸化膜と、ビット線2との境界領域上を覆う。

(もっと読む)

シャロー・トレンチ・アイソレーションの応力効果および光学的近接効果を相殺することによって半導体デバイスを製造する方法

【課題】半導体デバイス製造工程における形状の欠陥を補償する方法を提供する。

【解決手段】本発明は第1の半導体デバイスの分離構造応力効果を決定する工程、第2の半導体デバイスの光学的近接効果を決定する工程、製造モデル上で分離構造応力効果が光学的近接効果で相殺されるようにモデリング設計パラメータを選択する工程、および選択された設計パラメータを用いて第3の半導体デバイスを構成する工程とを含む半導体デバイスを製造する方法を提供する。

(もっと読む)

半導体基板、半導体装置、半導体基板の製造方法および半導体装置の製造方法

【課題】 膜厚を精度よく制御することを可能としつつ、半導体層を絶縁体上に安価に形成する。

【解決手段】 エピタキシャル成長を行うことにより、第1半導体層2を半導体基板1上に形成し、第1半導体層2が覆われるようにして半導体基板1上に第2半導体層3を形成し、第2半導体層3上に酸化防止膜5を形成した後、素子分離領域上の酸化防止膜5を除去し、第1半導体層2の端部の一部を露出させる開口部6を第1半導体層2の一対の辺に沿って形成し、開口部6を介してエッチングガスまたはエッチング液を第1半導体層2に接触させることにより、第1半導体層2をエッチング除去し、酸化防止膜5をマスクとして半導体基板1および第2半導体層3の熱酸化を行うことにより、半導体基板1と第2半導体層3との間の空洞部7に埋め込み酸化膜8aを形成するとともに、第2半導体層3の周囲に素子分離酸化膜8bを形成する。

(もっと読む)

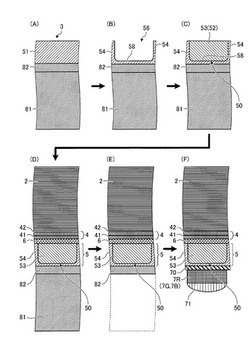

半導体基板、半導体装置、半導体基板の製造方法および半導体装置の製造方法

【課題】 絶縁体上に形成される半導体層の配置位置に制約を伴うことなく、信頼性の高い半導体層を安価に絶縁体上に形成する。

【解決手段】 第1半導体層2上に第2半導体層3を形成し、開口部8を介してエッチングガスまたはエッチング液を第1半導体層2に接触させることにより、第1半導体層2の一部をエッチング除去し、半導体基板1と第2半導体層3との間に空洞部9を形成した後、化学気相成長法により酸化膜を堆積することにより、空洞部9内に酸化膜10を形成する。

(もっと読む)

1 - 10 / 10

[ Back to top ]