Fターム[5F032AA33]の内容

素子分離 (28,488) | 絶縁物を用いる分離 (9,448) | 素子領域側面を絶縁物で分離するもの (8,208) | 溝内埋込み分離 (7,414) | 溝の断面形状 (2,101)

Fターム[5F032AA33]の下位に属するFターム

垂直側面を有するもの (1,970)

垂直側面を有しないもの (72)

Fターム[5F032AA33]に分類される特許

1 - 20 / 59

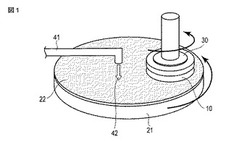

基板処理方法

【課題】 溝パターン内への絶縁層や配線層等の埋め込みを簡易に行うことができ、工程短縮やコスト低減をはかる。

【解決手段】 基板10の表面に形成された溝内に溶媒を埋め込むための基板処理方法であって、基板10の表面上に溶媒42を供給しながら、基板10の表面に弾性材料で形成された溶媒保持材22を接触させた状態で、基板10の表面と溶媒保持材22とが摺動するように、基板10及び前記溶媒保持材22をそれぞれ回転させる。

(もっと読む)

半導体装置およびその製造方法

【課題】第1のトランジスタと第2のトランジスタが、ぞれぞれのドレイン領域とソース領域を共有して同一の半導体基板上に形成される構成の半導体装置の製造において、それぞれのトランジスタのソース領域およびドレイン領域の直下に埋め込み絶縁膜を効率的に形成できる製造方法を提供する。

【解決手段】半導体基板上にそれぞれのトランジスタのソース領域およびドレイン領域に対応してトレンチを形成し、前記トレンチをSiGe混晶層と半導体層を順次形成することにより充填し、さらに第1のトランジスタのソース領域および第2のトランジスタのドレイン領域直下のSiGe混晶層を、素子分離溝を介して選択エッチングにより除去し、第1のトランジスタのドレイン領域および第2のトランジスタのソース領域として共有される拡散領域直下のSiGe混晶層を、前記拡散領域に形成した孔を介して選択エッチングし、除去する。

(もっと読む)

半導体装置及びその製造方法

【課題】ゲート電極とボディ領域とを接続したトランジスタを有する半導体装置に関し、動作速度を向上し消費電力を低減しうる半導体装置及びその製造方法を提供する。

【解決手段】第1の素子分離絶縁膜と、第1の素子分離絶縁膜により画定され、第1の素子分離絶縁膜よりも浅いウェルと、ウェル内に形成され、ウェルよりも浅く、ウェルの第1の部分とウェルの第2の部分とを画定する第2の素子分離絶縁膜と、第1の部分上に形成されたゲート絶縁膜と、ゲート絶縁膜上に形成されたゲート電極と、第2の部分においてウェルに電気的に接続され、ゲート電極とウェルとを電気的に接続する配線層とを有し、第2の素子分離絶縁膜下の領域のウェルの電気抵抗が、ウェルの他の領域の同じ深さにおける電気抵抗よりも低くなっている。

(もっと読む)

半導体装置

【課題】SOI−MISFETにおいて、多結晶シリコンの残存による電気的な短絡、ゲート電極の寄生容量の増大を防止する。逆狭チャネル効果の抑制。

【解決手段】シリコン膜13を有するSOI基板上にゲート絶縁膜14、第1の多結晶シリコン膜15、ストッパー窒化膜(16)を順次堆積する。シリコン膜13、第1の多結晶シリコン膜15の側面に逆テーパー面(テーパー角θが鈍角)が形成されるようにエッチングして素子分離溝を形成する。STI埋め込み絶縁膜17を堆積し、CMPにより平坦化した後、等速性のRIEによりストッパー窒化膜(16)と絶縁膜17をエッチングして平坦な表面を得、その上に第2の多結晶シリコン膜18を堆積し(e)、積層多結晶シリコン膜をエッチングして積層ゲート電極(15、18)を形成する(f)。以下、ソース・ドレイン領域21、シリサイド膜22、層間絶縁膜23及びメタル配線24等を形成する(g)。

(もっと読む)

半導体装置の製造方法

【課題】MOSトランジスタの形成工程を利用して、トレンチアイソレーションを形成できるようにした半導体装置の製造方法を提供する。

【解決手段】シリコン基板1にDTI層20とMOSトランジスタとを有する半導体装置の製造方法であって、シリコン基板1に深いトレンチを形成し、トレンチが形成されたシリコン基板1に熱酸化を施して、PMOSトランジスタ50のゲート酸化膜13を形成すると同時に、トレンチの内側面にSiO2膜14を形成する。次に、トレンチを埋め込むようにシリコン基板1上にポリシリコン膜15を堆積し、このポリシリコン膜15をパターニングする。これにより、PMOSトランジスタ50のゲート電極17を形成すると同時に、トレンチ内にSiO2膜14とポリシリコン膜18とを含むDTI層20を形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】工程が簡単で、よりラッチアップに強いCMOS構造を得る。

【解決手段】1×1018cm−3から1×1019cm−3の高不純物濃度の半導体基板2を用い、CMOS構造のP型ウェル4とN型ウェル5の境界に設けられた溝分離部13の先端部分がその高不純物濃度領域に達する(エピタキシャル層3を貫通して半導体基板2の領域に至る)ように深く形成することにより、従来のように溝分離部13よりも更に深い領域(溝分離部13の下側)を電子が通過することなく、従来のようにウェル領域内にN+埋め込み層やP+埋め込み層を基板深く埋め込む必要もなく、簡便な方法で、よりラッチアップに強いCMOS構造を得ることができ、コスト性能の両方に優れた半導体装置1を得ることができる。

(もっと読む)

液晶表示装置、及びその作製方法

【課題】作製工程を削減し、低コストで生産性の良い液晶表示装置を提供する。消費電力が少なく、信頼性の高い液晶表示装置を提供する。

【解決手段】島状半導体層を形成するためのフォトリソグラフィ工程及びエッチング工程を省略し、ゲート電極(同一層で形成される配線等を含む)を形成する工程、ソース電極及びドレイン電極(同一層で形成される配線等含む)を形成する工程、コンタクトホールを形成する(コンタクトホール以外の絶縁層等の除去を含む)工程、画素電極(同一層で形成される配線等を含む)を形成する工程の4つのフォトリソグラフィ工程で液晶表示装置を作製する。コンタクトホールを形成する工程において、半導体層が除去された溝部を形成することで、寄生チャネルの形成を防ぐ。

(もっと読む)

半導体装置とその製造方法

【課題】下側半導体層と埋込み絶縁層と上側半導体層が積層した積層体を有する半導体装置の耐圧を向上させることを目的としている。

【解決手段】半導体装置10は、下側半導体層20と埋込み絶縁層30と上側半導体層40が積層したSOI基板50を有する。下側半導体層20の埋込み絶縁層30と接する面の一部に凹部66が形成されている。凹部66内の比誘電率は、下側半導体層20の比誘電率よりも低い。

(もっと読む)

シングルゲートフィンFET及びその製造方法

【課題】新規なFinFET構造及びその製造方法を提供する。

【解決手段】シングルゲートフィンFET構造100は、2つの拡大された頭部、及び当該拡大された頭部と下層の超薄型ボディとを連結する2つの徐々に細くなる首部を有するアクティブフィン構造を含む。2つのソース/ドレイン領域102,104が、2つの拡大された頭部にそれぞれドープされる。絶縁領域26が、2つのソース/ドレイン領域の間に挿入される。溝分離構造24が、音叉形状のフィン構造の一方の側に配置される。片面サイドウォールゲート電極12bが、アクティブフィン構造における、溝分離構造とは反対側の垂直なサイドウォールに配置される。

(もっと読む)

ラジカル成分CVD用のインサイチュオゾン硬化

誘電体層を形成する方法を説明する。この方法は、ケイ素を含有する前駆体をプラズマ廃水と混合するステップと、ケイ素と窒素を含有する層を基板上に堆積するステップとを含む。ケイ素と窒素を含有する層は、ケイ素と窒素を含有する層を堆積するために使用したのと同じ基板処理領域内においてオゾン含有雰囲気中で硬化することによって、ケイ素と酸素を含有する層に転換される。さらなるケイ素と窒素を含有する層を、ケイ素と酸素を含有する層の上に堆積することができ、ここでも基板を基板処理領域から取り出すことなく、層のスタックをオゾン中で硬化させることができる。複数回の堆積−硬化サイクル後、ケイ素と酸素を含有する層のスタックの転換は、より高い温度で酸素含有環境中においてアニールすることができる。  (もっと読む)

(もっと読む)

半導体装置およびその製造方法

【課題】形成する素子に要求される素子間耐圧や素子内部耐圧に応じたディープトレンチ膜を有する半導体装置を提供する。

【解決手段】P型のシリコン基板11上に、N+型埋め込み層12と、N型半導体層13と、が積層された基板10と、基板10にN+型埋め込み層12の形成位置よりも深く形成され、基板10内の素子形成領域内を区画するディープトレンチ20と、ディープトレンチ20の内壁に沿って形成される側壁酸化膜23,24と、ディープトレンチ20内を埋めるTEOS膜を含むディープトレンチ膜26と、ディープトレンチ膜26で区画される素子形成領域に形成されるLDMOSと、を備え、ディープトレンチ20は、N+型埋め込み層12の上面よりも浅い位置の境界深さまでの第1のディープトレンチ21と、境界深さから底部までの第1のディープトレンチ21よりも小さい開口径を有する第2のディープトレンチ22によって構成される。

(もっと読む)

半導体デバイスの絶縁

【課題】半導体デバイスの絶縁構造の構造、および、形成方法を提供する。

【解決手段】当該絶縁構造は、底部が最上部よりも広くなっており、半導体デバイスの大きさを調整できる。第1のエッチングプロセスが、第1のトレンチ部分226を形成するために用いられ、第2のエッチングプロセスまたは酸化工程が、第1のトレンチ部分226の下に第2のトレンチ部分228を形成するために用いられる。第2のトレンチ部分は、第1のトレンチ部分よりも広い。一形態では、下地膜222が、第1のトレンチ部分の間、第1のトレンチ部分の側壁上に形成されてもよい(この第1のトレンチ部分は、第2のエッチングプロセスの間、第1のトレンチ部分の側壁を保護する)。あるいは、他の形態では、下地膜222が、第1のトレンチ部分の側壁上に堆積されていてもよい。

(もっと読む)

太陽電池の分離用トレンチライン

本発明は、基板上部の半導体層と側部の半導体層とを効率よく分離させ、且つ分離の信頼性を向上することができる太陽電池の分離用トレンチラインに関し、本発明に係る太陽電池の分離用トレンチラインは、太陽電池基板の上部及び側部に形成された半導体層を電気的に分離させる太陽電池の分離用トレンチラインにおいて、太陽電池基板の上面に交差、配置される複数の単位トレンチラインからなり、交差する単位トレンチラインの交差点は、単位トレンチライン上に位置すると共に単位トレンチラインの始点または終点から内側に所定の距離離間した地点に位置することを特徴とする。  (もっと読む)

(もっと読む)

ポリシロキサン系トレンチ埋め込み用縮合反応物及びトレンチ埋め込み膜の製造方法

【課題】基体に形成されたトレンチ内にシリコン酸化物を埋め込むために使用するのに好適な溶液の保存安定性が良く、埋め込み性が高く、厚膜化ができ、かつ良好なクラック耐性を有するトレンチ埋め込み用縮合反応物、及びトレンチ埋め込み膜の製造方法を提供すること。

【解決手段】ポリシロキサン化合物とシリカ粒子との縮合反応物、並びに20℃における蒸気圧が530Pa以上であり、かつ、沸点が80℃以上130℃未満である有機溶媒(A)、及び20℃における蒸気圧が530Pa未満であり、かつ、沸点が130℃以上200℃以下である有機溶媒(B)から成る混合溶媒、又は20℃における蒸気圧が530Pa以上であり、かつ、沸点が130℃以上200℃以下である有機溶媒(C)を含むことを特徴とするトレンチ埋め込み用縮合反応物。

(もっと読む)

半導体装置

【課題】素子分離端における薄膜化を抑制しつつ、第1半導体層と格子定数の異なる第2半導体層を第1半導体層に埋め込む。

【解決手段】Ox、NまたはCの斜めイオン注入16を第1半導体からなる半導体基板11に行うことにより、半導体基板11を構成する第1半導体よりもエッチングレートが小さなエッチブロック層17を素子分離溝12の側壁に形成し、第1半導体よりも格子定数が大きな第2半導体を凹部25内にエピタキシャル成長させることにより、第2半導体からなる埋め込み層26を凹部25内に選択的に形成する。

(もっと読む)

半導体装置の製造方法

【課題】 従来の半導体装置の製造方法では、製造工程を煩雑とせず、遮光性の膜に対するアライメントマークを形成することが困難であるという問題があった。

【解決手段】 本発明の半導体装置の製造方法では、基板3、エピタキシャル層4に溝部9、分離用トレンチ16を形成する工程を利用し、スクライブライン領域2にアライメントマーク形成用の溝部15を形成する。溝部15内には、HTO膜19、多結晶シリコン膜20を堆積し、加工することで、アライメントマークとしての凹部24、25を形成する。この製造方法により、製造工程を簡略化し、アライメントマークを形成できる。

(もっと読む)

半導体装置、半導体製造装置および半導体装置の製造方法

【課題】半導体基板上の凹部が逆テーパ形状やオーバーハング形状を有する場合においても、埋め込み性や膜質の劣化を抑制しつつ、埋め込み絶縁膜の応力を低減することが可能な半導体装置及びその製造方法を提供する。

【解決手段】半導体基板1上にトレンチ5を形成し、熱CVD法を用いることで、トレンチ5内の一部を埋め込む埋め込み絶縁膜6を半導体基板1上に成膜し、埋め込み絶縁膜6の成膜時よりも高い温度にて埋め込み絶縁膜6を熱処理した後、熱CVD法を用いることで、トレンチ5内の一部を埋め込む埋め込み絶縁膜7を埋め込み絶縁膜6上に成膜し、埋め込み絶縁膜7の成膜時よりも高い温度にて埋め込み絶縁膜7を熱処理した後、熱CVD法を用いることで、トレンチ5内を完全に埋め込む埋め込み絶縁膜を埋め込み絶縁膜7上に成膜し、埋め込み絶縁膜の成膜時よりも高い温度にて埋め込み絶縁膜を熱処理する。

(もっと読む)

半導体装置

【課題】パッケージ工程における応力を緩和し、パッケージ工程前後での特性変化を抑制する半導体装置を提供する。

【解決手段】半導体装置100を構成する素子のうち特に精度が要求されパッケージからの応力を受けたくない素子領域3を応力緩和のための緩衝領域8で囲むことにより、パッケージ工程で発生する引っ張り応力あるいは圧縮応力の影響を抑制し、パッケージ工程前後での特性の変化を低減する。

(もっと読む)

半導体装置の製造方法

【課題】ゲート加工後の酸化工程等において、酸化剤がフローティングゲート電極を構成するポリシリコン膜の下部を酸化することを極力防止する。

【解決手段】本発明の半導体装置の製造方法は、半導体基板1上にゲート絶縁膜5、ポリシリコン膜6及びシリコン窒化膜10を積層形成する工程と、ドライエッチングにより素子分離用溝4を形成する工程と、HDP−CVDにより素子分離用溝4内に高密度の第1の酸化膜9を堆積して埋め込む工程であって、メモリセル部の素子分離用溝4に埋め込む第1の酸化膜9を、上面の高さが半導体基板1の活性領域2よりも上の位置まで堆積し、且つ、トレンチ4の上方を塞がないよう堆積する工程と、素子分離用溝4内に第1の酸化膜の密度より密度が低い第2の酸化膜12を埋め込む工程と、シリコン窒化膜10をストッパとして第1および第2の酸化膜を平坦化する工程と、メモリセル部の素子分離用溝4に埋め込まれた第2の酸化膜12を除去する工程とを備えたものである。

(もっと読む)

半導体装置及びその製造方法

【課題】

誘電体分離型半導体装置において、高耐圧素子の特性を損なわずにサブミクロン領域の微細MOSトランジスタを実現する実用化に有効な構造を提案する。

【解決手段】

SOI基板の活性層に形成された深い分離溝の側壁酸化膜を活性層表面に延在して形成することでゲート用多結晶シリコンの絶対段差を大幅に低減させ微細加工を可能とし、素子分離溝近傍に配置される電極は上記の溝側壁酸化膜の厚さの4倍以上の厚さを有する絶縁膜でシリコン表面と分離され、高耐圧素子の絶縁破壊を回避できる。

(もっと読む)

1 - 20 / 59

[ Back to top ]