Fターム[5F032AA39]の内容

素子分離 (28,488) | 絶縁物を用いる分離 (9,448) | 素子領域側面を絶縁物で分離するもの (8,208) | 溝内埋込み分離 (7,414) | 溝の断面形状 (2,101) | 垂直側面を有しないもの (72)

Fターム[5F032AA39]の下位に属するFターム

V溝及びその変形 (21)

Fターム[5F032AA39]に分類される特許

1 - 20 / 51

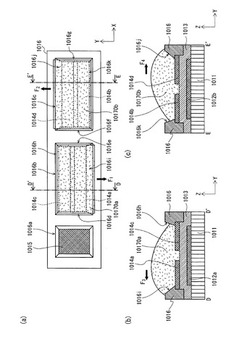

薄膜トランジスタ装置とその製造方法、有機EL表示素子、および有機EL表示装置

【課題】有機半導体層の形成に際して、不所望の領域への有機半導体層の形成を抑制し、且つ、隣接する開口部間でのインクの混合を抑制することにより、高い品質を備える薄膜トランジスタ装置とその製造方法、有機EL表示素子、および有機EL表示装置を提供する。

【解決手段】隔壁1016には、3つの開口部1016a,1016b,1016cが開けられている。開口部1016b,1016cの各底部には、ソース電極1014a,1014b、ドレイン電極1014c,1014dが露出し、各々がチャネル部として機能する部分である。開口部1016bを臨む側面部のうち、側面部1016d,1016eは、側面部1016iに比べ、傾斜が相対的に急峻な斜面である。開口部1016cを臨む側面部のうち、側面部1016fは、側面部1016jに比べ、傾斜が相対的に急峻な斜面である。

(もっと読む)

半導体記憶装置およびその製造方法

【課題】STIの形成によるウェル拡散層の不純物濃度の変化を抑制し、かつ、ウェル拡散層のドーズロスを抑制した半導体記憶装置およびその製造方法を提供する。

【解決手段】半導体記憶装置は、半導体基板を備える。メモリセル領域には、複数のメモリセルが半導体基板上に形成されている。周辺回路領域には、複数のメモリ素子を制御する複数の半導体素子が形成されている。素子分離領域は、複数のメモリセル間を分離し、あるいは、複数の半導体素子間を分離する。周辺回路領域において半導体素子が形成されているアクティブエリアの不純物濃度は、半導体基板の表面に対して水平方向に素子分離領域の側面からアクティブエリアの内部へ向かって低下している。

(もっと読む)

半導体装置及びその作製方法

【課題】酸化物半導体を用いるトランジスタにおいて、電気的特性の良好なトランジスタ及びその作製方法を提供することを課題の一とする。

【解決手段】基板上に酸化物半導体膜及び絶縁膜を有し、酸化物半導体膜の端部は絶縁膜と接しており、酸化物半導体膜は、チャネル形成領域と、チャネル形成領域を挟んで形成されたドーパントを含む領域とを含み、酸化物半導体膜上に接して形成されたゲート絶縁膜と、ゲート絶縁膜上に形成され、サイドウォール絶縁膜を有するゲート電極と、サイドウォール絶縁膜、酸化物半導体膜、および絶縁膜に接して形成されたソース電極およびドレイン電極とを有する半導体装置である。

(もっと読む)

半導体装置

【課題】SOI−MISFETにおいて、多結晶シリコンの残存による電気的な短絡、ゲート電極の寄生容量の増大を防止する。逆狭チャネル効果の抑制。

【解決手段】シリコン膜13を有するSOI基板上にゲート絶縁膜14、第1の多結晶シリコン膜15、ストッパー窒化膜(16)を順次堆積する。シリコン膜13、第1の多結晶シリコン膜15の側面に逆テーパー面(テーパー角θが鈍角)が形成されるようにエッチングして素子分離溝を形成する。STI埋め込み絶縁膜17を堆積し、CMPにより平坦化した後、等速性のRIEによりストッパー窒化膜(16)と絶縁膜17をエッチングして平坦な表面を得、その上に第2の多結晶シリコン膜18を堆積し(e)、積層多結晶シリコン膜をエッチングして積層ゲート電極(15、18)を形成する(f)。以下、ソース・ドレイン領域21、シリサイド膜22、層間絶縁膜23及びメタル配線24等を形成する(g)。

(もっと読む)

半導体装置及びその製造方法

【課題】パワーデバイスの高耐圧とオン抵抗の低減とを同時に実現する。

【解決手段】実施形態に係わる半導体装置は、半導体基板101内のソース領域107A、ドレイン領域107B、及びドレイン領域107Bに接したドリフト領域105と、ソース領域107A及びドレイン領域107B間のドリフト領域105内のSTI絶縁層I−2と、STI絶縁層I−2上、ドリフト領域105上、並びに、ソース領域107A及びドレイン領域107B間のチャネル領域上のゲート電極110とを備える。STI絶縁層I−2は、第1及び第2のトレンチの内面上の第1の酸化膜102及び窒化膜103と、第1及び第2のトレンチを満たす窒化膜103上の第2の酸化膜104とを備える。第2のトレンチは、第1のトレンチ内に形成され、第1のトレンチの底面よりも低い底面を有し、第1のトレンチの幅よりも狭い幅を有する。

(もっと読む)

半導体装置およびその製造方法

【課題】チャネル領域となるSOI構造を有する半導体線条突出部の形状のばらつきを抑制し、トランジスタ特性のばらつきを減少することができる半導体装置を提供する。

【解決手段】半導体基板1の素子分離用の溝に埋込み絶縁膜が埋め込まれてなる素子分離領域2と、素子分離領域2によって区画されてなり、素子分離用の溝を区画する側壁面と半導体基板の1一面とを有し、かつ側壁面には埋込み絶縁膜に向けて突出した半導体線条突出部1aが素子分離用の溝に沿って設けられてなる活性領域Tと、半導体線条突出部1aを残して活性領域Tを分断するように設けられたゲート電極用のゲート溝3と、ゲート溝3の内面に形成されたゲート絶縁膜4と、ゲート溝3に埋め込まれたゲート電極5と、ゲート電極5のゲート長方向両側の活性領域Tにそれぞれ形成され、半導体線条突出部1aによって連結される不純物拡散領域7と、を具備してなることを特徴とする。

(もっと読む)

半導体装置およびその製造方法

【課題】SOI基板に形成され、SOI基板を構成する半導体層の素子領域の周囲が素子分離により囲まれた半導体装置において、素子分離に起因する信頼度の低下を防ぐことのできる技術を提供する。

【解決手段】トレンチ分離を構成するディープトレンチ4の上部のトレンチ幅を、1.2μmよりも狭くすることにより、ディープトレンチ4の内部を絶縁膜5で埋め込んだ際に生じる中空7が、絶縁膜5の上面に現れるのを防ぐことができる。ディープトレンチ4の上部のトレンチ幅が狭くなることにより懸念される互いに隣接する素子領域間の耐圧の低下は、ディープトレンチ4の上部に、ディープトレンチ4の内部に埋め込まれた絶縁膜5と繋がるLOCOS絶縁膜6を形成することによって回避する。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】製造工程を簡略化しつつ、絶縁分離トレンチの破壊耐圧を向上させることができる半導体装置の製造方法および半導体装置を提供する。

【解決手段】半導体層13の素子形成領域に半導体素子が形成された半導体基板10を用意する工程と、半導体層13に、素子形成領域を取り囲み、絶縁膜12側と反対側の表面から当該絶縁膜12に達するトレンチ20を形成する工程と、トレンチ20の壁面に側壁絶縁膜21を形成する工程と、トレンチ20に、不純物を含む埋込絶縁膜22をCVD法により、当該埋込絶縁膜22にて囲まれる空洞22aを形成しつつ配置する工程と、半導体基板10を熱処理する工程と、を含む工程を行う。

(もっと読む)

半導体装置の製造方法

【課題】 フォトリソグラフィ技術の分解能にディープトレンチの大きさが依存しない、ディープトレンチを備える半導体装置の製造方法を提供する。

【解決手段】この発明によれば、半導体基板上にシャロートレンチを形成する工程と、前記シャロートレンチ内に絶縁層を形成する工程と、前記シャロートレンチ内に前記絶縁層を貫通し、前記シャロートレンチよりも深いディープトレンチを形成する工程と、を備え、前記ディープトレンチを形成する工程は、前記ディープトレンチの側面が前記半導体基板に対して第1テーパー角となる第1ディープトレンチを形成する工程と、その後、前記ディープトレンチの側面が前記半導体基板に対して第2テーパー角となる第2ディープトレンチを形成する工程と、で構成され、第2テーパー角が第1テーパー角と異なる角度であることを特徴とする半導体装置の製造方法が提供される。

(もっと読む)

半導体装置及びその製造方法

【課題】複数の素子分離領域で分離された複数の素子形成領域を有する半導体装置及びその製造方法において、素子分離領域に形成される膜厚の厚い素子分離膜による素子形成領域の表面のバーズビークの発生を防ぐこと、並びに素子分離膜の端部近傍の半導体層に結晶欠陥が発生することを防止し、且つ該半導体層が受けるストレスの低減を図る。

【解決手段】素子形成領域1に、半導体層11をエッチングして側壁5、5aを有する素子形成半導体層4を形成する。次に、前記素子形成領域1を被覆するポリシリ窒化膜マスク9aに加えて、前記ポリシリ窒化膜マスク9aの側壁及び底面、前記素子形成半導体層4の側壁5、5a及び前記半導体層11の一部を被覆するポリシリコンサイドスペーサ12b及び窒化膜サイドスペーサ13を形成する。その後、素子分離領域2に、前記素子形成領域1を取り囲む素子分離膜3を形成する。

(もっと読む)

トレンチ埋め込み用組成物

【課題】基板表面上のナノメートルレベルの開口幅を有し、アスペクト比が大きいトレンチ(溝)への埋め込み性に優れ、ボイドなどの欠陥の発生が抑制され、電気的絶縁性に優れたアイソレーション構造を製造するのに好適なトレンチ埋め込み用組成物、および該組成物を用いたトレンチ・アイソレーション構造の製造方法の提供。

【解決手段】アルキルトリアルコキシシランを50モル%以上含むアルコキシシラン原料を加水分解、縮合して得られる加水分解縮合物を含有し、該加水分解縮合物の重量平均分子量が1000〜50000であり、該加水分解縮合物の含有量が組成物全量に対して14質量%超30質量%以下であるトレンチ埋め込み用組成物の塗膜14により、基板10表面上に形成されたトレンチ12を埋め込む。

(もっと読む)

半導体装置およびその製造方法

【課題】簡易なプロセスで、高い埋め込み性を確保する必要のない半導体装置およびその製造方法を提供する。

【解決手段】本発明の半導体装置の製造方法では、まず支持基板SSと、埋め込み絶縁膜BOXと半導体層SLとがこの順で積層された構成を有する半導体基板SUBが準備される。半導体層SLの主表面に、導電部分を有する素子が完成される。上記素子を平面視において取り囲む溝DTRが、半導体層SLの主表面から埋め込み絶縁膜BOXに達するように形成される。上記素子上を覆うように、かつ溝DTR内に中空を形成するように素子上および溝DTR内に第1の絶縁膜(層間絶縁膜II)が形成される。上記第1の絶縁膜に素子の導電部分に達する孔であるコンタクトホールCHが形成される。

(もっと読む)

HOT(hybridorientationtechnology)を選択的エピタキシーに関連して用いて移動度を改善する方法およびそれに関連する装置

半導体装置が、第1の基板(102、202)と、第1の基板の第1の部分の上に位置し、埋め込み層(104、204)によって第1の基板から分離される第2の基板とを含む。この半導体装置はまた、第1の基板の第2の部分の上に位置し、第2の基板から隔離されるエピタキシャル層(108、220)を含む。この半導体装置はさらに、少なくとも部分的に第2の基板内に形成される第1のトランジスタ(116)と、少なくとも部分的にエピタキシャル層内またはその上に形成される第2のトランジスタ(128)とを含む。第2の基板およびエピタキシャル層は、異なる電子および正孔移動度を有するバルク特性を有する。トランジスタの少なくとも1つは、少なくとも約5Vの1つまたは複数の信号を受け取るように構成される。第1の基板は第1の結晶面方位を有し、第2の基板は第2の結晶面方位を有し得る。  (もっと読む)

(もっと読む)

フィン型電界効果トランジスタ

【課題】フィン型電界効果トランジスタを提供する。

【解決手段】本発明は、フィン型電界効果トランジスタの分離構造に関する。フィン型電界効果トランジスタの例は、主表面からなる基板と、基板の主表面から突出する複数のフィン構造と、フィン構造の間に位置する複数の分離構造と、からなる。各フィン構造は、変化位置により分けられる上部分と下部分からなり、この変化位置は、フィン構造の側壁と基板の主表面の角度85度のところにあり、上部分は、この基板の主表面と実質上、垂直な側壁、及び、第一幅を有する頂面を有し、下部分は、上部分の両側のテーパ型側壁、及び、第一幅より大きい第二幅を有する底部を有する。複数の分離構造は、それぞれ、基板の主表面から、変化位置上の点に延伸する。

(もっと読む)

半導体装置及びその製造方法

【課題】トレンチ溝を挟んで隣接する同一の導電型の拡散層同士の間の耐圧の低下を防止できるようにする。

【解決手段】半導体基板100には、PMOS領域AとNMOS領域Bとが形成されている。PMOS領域AとNMOS領域Bとは、該PMOS領域AとNMOS領域Bとを電気的に分離するための絶縁膜が充填された第1のトレンチ溝105によって区画されている。第1のトレンチ溝105は、その底部の幅が上部の幅よりも大きい。これにより、PMOS領域AとNMOS領域Bとの間の耐圧の劣化を防止することができる。

(もっと読む)

半導体装置及びその製造方法

【課題】チャネル領域を拡大し、駆動電流の増大を図ることを可能とした半導体装置及びその製造方法を提供する。

【解決手段】半導体基板2に埋め込まれた埋込み絶縁膜3により絶縁分離された活性領域5と、活性領域5上に形成されたゲート絶縁膜6を介して当該活性領域5を跨ぐように形成されたゲート電極7と、ゲート電極7を挟んだ両側の活性領域5にイオン注入することによって形成されたソース領域8及びドレイン領域9とを備え、活性領域5に溝部10が設けられて、この溝部10の内側にゲート絶縁膜6を介してゲート電極7の一部が埋め込まれてなるトレンチ型のチャネル構造を有し、活性領域5の両側面に凹部11が対向して設けられて、これら凹部11の間に幅狭部12が形成されることによって、少なくとも溝部10の底面と幅狭部12との間に当該幅狭部12よりも幅広となるチャネル領域13が形成されている。

(もっと読む)

半導体装置およびその製造方法

【課題】薄膜BOX−SOI基板に形成される電界効果型トランジスタの信頼性および動作特性の劣化を防ぐことのできる技術を提供する。

【解決手段】薄膜BOX−SOI基板の主面上に所定の間隔で配置されたnウェルnwおよびpウェルpwが形成されており、pウェルpwに形成されたnMIS1nは、SOI層1iの主面上に所定の距離を隔てて積み上げられた半導体層に形成された一対のn型ソース・ドレイン領域2nと、一対のn型ソース・ドレイン領域2nに挟まれたゲート絶縁膜3、ゲート電極4、およびサイドウォール5とを有しており、nウェルnwとpウェルpwとの間に素子分離10を形成し、素子分離10の側端部が、n型ソース・ドレイン領域2nの側端部(BOX層1bの側壁部)よりもゲート電極4側に広がっている。

(もっと読む)

集積化半導体装置及びその製造方法

【課題】 SOIウェーハを使用する集積化半導体装置の結晶欠陥の低減、耐圧向上、リーク電流の低減が要求されている。

【解決手段】 SOIウェーハにトレンチ16を形成する時に、トレンチ16の底に傾斜面17を有するように半導体層13を残存させる。この傾斜面17に沿って厚いシリコン酸化膜(第2の絶縁膜)25aを形成する。この厚いシリコン酸化膜(第2の絶縁膜)25aによって埋込み絶縁層12と半導体層13との界面への酸素の侵入を防ぐ。

(もっと読む)

半導体装置の製造方法

【課題】不揮発性記憶装置の記憶セル間のショートを抑制し、その特性のばらつきを抑制する。

【解決手段】基板上に配置させた第1の配線層の上層に、記憶セル層を形成し、記憶セル層を第2の方向に分離すると共に、第1の方向に延在する第1の配線を基板上に形成するために、第1の方向に連通する第1のトレンチを形成し、第1のトレンチ内に第1の素子分離層を埋設し、記憶セル層及び第1の素子分離層の上層に、第2の配線層を形成し、第2の配線層を加工し、第2の方向に延在する第2の配線を形成し、第1の素子分離層をエッチングして、第1の素子分離層の上面を所定の位置まで降下させて、記憶セル層を第1の方向に分離するために、第2の方向に連通する第2のトレンチを形成する。

(もっと読む)

半導体デバイス上に共形酸化物層を形成するための方法

半導体基板上に酸化物層を形成するための方法及び装置を開示する。1つ又は複数の実施形態では、半導体基板の温度を約100℃未満に制御することによって、プラズマ酸化を使用して、共形酸化物層を形成することができる。1つ又は複数の実施形態による半導体基板の温度を制御するための方法は、静電チャックならびに冷却剤及びガス対流を利用することを含む。  (もっと読む)

(もっと読む)

1 - 20 / 51

[ Back to top ]