Fターム[5F032AA69]の内容

素子分離 (28,488) | 絶縁物を用いる分離 (9,448) | 素子領域側面を絶縁物で分離するもの (8,208) | 溝内埋込み分離 (7,414) | 埋込みに工夫 (1,675)

Fターム[5F032AA69]の下位に属するFターム

数回の埋込みをするもの(DAで具体的に) (373)

埋込み材料を酸化するもの (56)

溝内への選択的埋込み (1,094)

Fターム[5F032AA69]に分類される特許

1 - 20 / 152

成膜装置及び半導体装置の製造方法

【課題】膜厚を確保することが可能な成膜装置及び半導体装置の製造方法を提供する。

【解決手段】実施形態にかかる成膜装置は溝を有する基板に液体材料を供給して前記溝内に前記液体材料を埋め込み、液層を形成する塗布部と、前記溶液層を乾燥させて固化する乾燥部と、前記乾燥中に前記液層の表面に蒸気を照射する蒸気供給部と、を備えることを特徴とする。

(もっと読む)

基板処理装置及び半導体装置の製造方法

【課題】膜応力の小さい低誘電率の絶縁膜を形成できる基板処理装置を提供する。

【解決手段】処理室内へ無機シリコンガスと酸素含有ガスを供給している状態で、励起エネルギーを処理室内へ供給して、基板表面にシリコン酸化膜を形成するシリコン酸化膜形成工程と、処理室内へ有機シリコンガスを供給している状態で、励起エネルギーを処理室内へ供給して、基板表面にシリコン膜を形成するシリコン膜形成工程と、を行うことにより、処理室内の基板表面に絶縁膜を形成するよう、基板処理装置を構成する。

(もっと読む)

集積回路装置及びその製造方法

【課題】FinFETの特性が均一な集積回路装置及びその製造方法を提供する。

【解決手段】実施形態に係る集積回路装置は、半導体基板の上面に形成され、第1方向に延びる複数本のフィンと、前記フィン間に配置された素子分離絶縁膜と、前記第1方向に対して交差した第2方向に延び、前記素子分離絶縁膜上に設けられたゲート電極と、前記フィンを前記ゲート電極から絶縁する絶縁膜と、を備える。そして、連続して配列された複数本の前記フィンが配置された第1領域においては、前記素子分離絶縁膜の上面は前記フィンの上端よりも下方の第1の位置に位置し、前記第1領域から見て前記第2方向に位置する第2領域においては、前記素子分離絶縁膜の上面は前記フィンの上端よりも上方の第2の位置に位置する。また、前記第2領域においては、前記素子分離絶縁膜が前記フィンの側面の全体を覆っている。

(もっと読む)

半導体装置

【課題】可撓性を有し、曲げ等の物理的変化に対して耐性を有する半導体装置および当該

半導体装置の作製方法を提供することを目的とする。

【解決手段】可撓性を有する基板上に設けられた、半導体膜、半導体膜上にゲート絶縁膜

を介して設けられたゲート電極およびゲート電極を覆って設けられた層間絶縁膜とを有す

る複数のトランジスタと、複数のトランジスタの間に設けられた屈折部分とを有し、屈折

部分は、層間絶縁膜に設けられた開口部に層間絶縁膜より弾性率が低い物質が充填されて

設けられている。また、本発明では、開口部に充填する物質として他にも、層間絶縁膜よ

りガラス転移点が低い物質や塑性を有する物質を設けることができる。

(もっと読む)

半導体装置およびその製造方法

【課題】 層間絶縁膜をCMP法で研磨、平坦化する際、MOS型トランジスタのチャネル領域に応力を与えるためにゲート電極を覆うように形成される応力ライナー膜が研磨されて、トランジスタ特性の変動やバラツキが発生しないようにする。

【解決手段】 第1活性領域(例えばPチャネルトランジスタ形成領域)上のゲート電極(シリコン膜14と金属シリサイド膜15との積層膜)上には第1応力膜(圧縮応力ライナー膜)16のみを形成し、第2活性領域(例えばNチャネルトランジスタ領域)上のゲート電極上には第2応力膜(引っ張り応力ライナー膜)18のみを形成する。一方、素子分離10上のゲート電極上には第1および第2応力膜16、18の積層膜を形成する。層間絶縁膜20のCMP法による研磨は、素子分離10上の第2応力膜18の露出後に停止する。

(もっと読む)

半導体装置

【課題】基板を介したクロストークを抑制でき、放熱性が高い半導体装置を提供する。

【解決手段】実施形態に係る半導体装置1は、半導体基板10を備える。前記半導体基板の内部には空洞11が形成されている。また、前記半導体基板の内部には、前記空洞を前記半導体基板の上面に連通させる連通孔12も形成されている。前記半導体装置は、さらに、前記空洞及び前記連通孔の内面上に設けられた絶縁膜13と、前記空洞及び前記連通孔の内部に埋め込まれ、熱伝導率が前記絶縁膜の熱伝導率よりも高い伝熱部材14と、前記半導体基板における前記空洞の直上域に形成された素子21,22と、を備える。

(もっと読む)

二酸化ケイ素膜の製造方法

【課題】低収縮かつ低応力である絶縁膜を製造することができる方法の提供。

【解決手段】基板表面にポリシラザン組成物を塗布して塗膜を形成させ、引き続き前記塗膜を過酸化水素雰囲気下、50〜200℃で加熱することを含んでなることを特徴とする、二酸化ケイ素膜の製造方法。この二酸化ケイ素膜の製造方法によって各種絶縁膜などのアイソレーション構造を形成させることができる。

(もっと読む)

半導体装置

【課題】正確にメインセルに流れる電流を検出することができると共に、高い電圧が用いられる場合でもその影響を受け難い半導体装置を提供する。

【解決手段】メインセルとセンスセルとをトレンチ分離構造1dによって絶縁分離する。これにより、メインセルのコレクタに対して100V以上の高電圧が印加されても、それに起因するノイズが電流検出用の出力端子に誘起されないようにできる。また、センスセルのエミッタ電位がセンス抵抗Rsに流れる電流によって上昇しても、メインセルのエミッタと電気的に完全に分離されているため、寄生トランジスタが動作することもない。勿論、抵抗層14から発生させられたノイズが電流検出用の出力端子に誘起されることも抑制できる。したがって、正確にメインセルに流れる電流を検出することができると共に、高い電圧が用いられる場合でもその影響を受け難い半導体装置とすることが可能となる。

(もっと読む)

半導体記憶装置及びその製造方法

【課題】メモリセルアレイおよび周辺回路領域の素子分離領域の深さを調節しつつ、周辺回路部の素子分離領域に形成されるマイクロトレンチ形状の影響を抑制し、信頼性の高い半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、半導体基板上に設けられデータを記憶する複数のメモリセルを含むメモリセルアレイと、半導体基板上に設けられメモリセルアレイを制御する周辺回路部とを備えている。素子分離部は、複数のメモリセルおよび周辺回路部が形成されるアクティブエリア間に設けられている。側壁膜は、周辺回路部におけるアクティブエリアの側面に設けられている。

(もっと読む)

半導体装置およびその製造方法

【課題】 本発明は、より寄生容量の少ない素子の実現が可能な素子分離構造を有する半導体装置およびその製造方法を提供することにある。

【解決手段】 SOI基板上に形成される半導体装置は、素子分離領域に形成される素子分離溝(空洞)17と、半導体層11と支持基板13の間に介在する埋め込み絶縁層の一部に素子分離溝(空洞)17に接する空洞領域20を有する。

【効果】寄生容量を低減でき、また、素子の耐圧を高めることができる。

(もっと読む)

半導体基板の製造方法及び半導体装置の製造方法

【課題】信頼性の高いLocalSOI構造を有する基板を低コストで作製する。

【解決手段】第1の半導体からなる基板10上に、結晶成長により第2の半導体からなる層及び前記第1の半導体からなる層12を順次形成する半導体層形成工程と、前記第2の半導体からなる層をエッチングにより除去し開口領域13を形成する開口領域形成工程と、前記開口領域に、窒化物膜、炭化物膜又は酸化物膜を含む材料により形成される酸化遅延膜14を前記開口領域の入口における膜厚が所定の膜厚となるように成膜する酸化遅延膜成膜工程と、前記第1の半導体からなる基板及び前記第1の半導体からなる層の前記第1の半導体の一部を熱酸化することにより、前記開口領域に熱酸化膜15を形成する熱酸化工程とを有することを特徴とする、Local SOI半導体基板の製造方法。

(もっと読む)

トレンチの埋め込み方法および成膜装置

【課題】 トレンチの微細化がさらに進展しても、トレンチの内部に、膨張可能な膜及び酸化障壁となる膜を形成することが可能なトレンチの埋め込み方法を提供すること。

【解決手段】 トレンチ内部に酸化障壁膜の形成工程(ステップ3)、酸化障壁膜上に膨張可能な膜の形成工程(ステップ4)、焼成することで収縮する埋め込み材でトレンチを埋め込む工程(ステップ5)、埋め込み材の焼成工程(ステップ6)と、を含み、ステップ3の工程が、アミノシラン系ガスを供給して、トレンチの内部に第1のシード層を形成する工程(ステップ31)、第1のシード層上に窒化シリコン膜を形成する工程(ステップ32)と、を含み、ステップ4の工程が、アミノシラン系ガスを供給して、窒化シリコン膜上に第2のシード層を形成する工程(ステップ41)と、第2のシード層上にシリコン膜を形成する工程(ステップ42)と、を含む。

(もっと読む)

不揮発性半導体記憶装置および不揮発性半導体記憶装置の製造方法

【課題】隣接する浮遊ゲート電極間の間隔を増大させることなく、隣接する浮遊ゲート電極間の寄生容量を低減する。

【解決手段】電極間絶縁膜7下において、埋め込み絶縁膜9が上下に分離されることで、ワード線方向DWに隣接する浮遊ゲート電極6間に空隙AG1が形成され、空隙AG1にて分離された上側の埋め込み絶縁膜9は電極間絶縁膜7下に積層し、下側の埋め込み絶縁膜9はトレンチ2内に配置する。

(もっと読む)

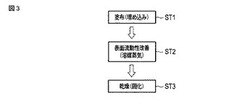

基板処理方法

【課題】基板に吸着したガスに含まれる不純物を効果的に除去しつつ基板処理することができる基板処理方法を提供する。

【解決手段】基板を処理室内へ搬入する搬入工程と、前記処理室内へ搬入された基板に、第1のガスを吸着させる第1ガス供給工程と、前記第1ガス供給工程の後、前記処理室内から第1のガスを排気する第1ガス排気工程と、前記第1ガス排気工程の後、前記基板に付着した第1のガスを、分解機構により分解する第1分解工程と、前記第1分解工程の後、前記処理室内へ第2のガスを供給しつつ、前記分解機構により第2のガスを分解する第2ガス供給工程と、前記第2ガス供給工程の後、前記基板を処理室内から搬出する搬出工程とから、基板処理方法を構成する。

(もっと読む)

素子分離材料用塗布液、素子分離材料用塗布液の作製方法、素子分離層用薄膜、及び、素子分離層用薄膜の形成方法

【課題】絶縁破壊電圧の高い素子分離層を形成することができる素子分離材料用塗布液等を提供する。

【解決手段】素子分離材料用塗布液は、一般式(I)で表される構造単位からなる骨格を有するポリシラザン等と、酸化物を形成できる金属元素を含む化合物と、溶媒とを備えている。金属元素は、チタン、ジルコニウム、ハフニウム、又は、タンタルであり、ポリシラザン等のSiのモル数に対し、0.5mol%〜19mol%となるように添加されている。 (もっと読む)

(もっと読む)

固体撮像装置及びその製造方法

【課題】素子を分離するための素子分離部による不具合の発生確率を低減する。

【解決手段】フォトダイオード310が内部に形成された半導体基板500と、素子分離部420とを備える。素子分離部420は、該素子分離部420の少なくとも一部が、半導体基板500に形成された溝410の内部に充填されるように形成される。素子分離部420は、溝410の内部の下方に形成されたシリコン酸化膜421と、溝410の内部の上方に形成されたシリコン酸化膜422とから構成される。シリコン酸化膜421の密度は、シリコン酸化膜422の密度より小さい。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】製造工程を簡略化しつつ、絶縁分離トレンチの破壊耐圧を向上させることができる半導体装置の製造方法および半導体装置を提供する。

【解決手段】半導体層13の素子形成領域に半導体素子が形成された半導体基板10を用意する工程と、半導体層13に、素子形成領域を取り囲み、絶縁膜12側と反対側の表面から当該絶縁膜12に達するトレンチ20を形成する工程と、トレンチ20の壁面に側壁絶縁膜21を形成する工程と、トレンチ20に、不純物を含む埋込絶縁膜22をCVD法により、当該埋込絶縁膜22にて囲まれる空洞22aを形成しつつ配置する工程と、半導体基板10を熱処理する工程と、を含む工程を行う。

(もっと読む)

半導体素子及びその製造方法

【課題】半導体素子及びその製造方法を提供する。

【解決手段】基板上で第1方向に延在するラインパターンと、ラインパターンの端部から、第1方向と異なる方向に延在する分岐ラインパターンとをそれぞれ含む第1導電ライン;第2導電ライン;第3導電ラインとを含む半導体素子であり、中間に位置する導電ラインの分岐ラインパターンは、他の導電ラインの分岐ラインパターン間に位置し、長さもさらに短い。これにより、コンタクト・パッドが、導電ラインの分岐ラインパターンと一体に形成されうる。

(もっと読む)

素子間分離領域の形成方法

【課題】 STIによる素子間分離において、ボイドが無く完全にトレンチを埋め込むことができ、処理時間の短縮化を図ることができる素子間分離領域の形成方法を提供する。

【解決手段】 本発明の素子間分離領域の形成方法は、酸化雰囲気中で熱処理することにより酸化して膨張し且つ絶縁性をもつに至る物質からなる半導体基板1に対し、その表面の一部分を除去して、素子間分離用のトレンチ4を形成するトレンチ形成工程と、トレンチ4を形成した半導体基板1を酸化雰囲気中で熱処理して、半導体基板1の表面を酸化膨張させ、酸化膨張により生成された絶縁物6によりトレンチ4を埋め込む酸化膨張工程と、酸化膨張工程の後に、絶縁物6により埋め込まれた部分を残して、半導体基板1のうち素子形成領域となる部分の表面を露出させる露出工程と、を含むことを特徴とする。

(もっと読む)

半導体装置の製造方法

【課題】半導体基板中に形成した素子分離溝の上部角部への電界集中によるトランジスタの電気的特性の劣化を抑制することが可能な半導体装置の製造方法を提供する。

【解決手段】半導体基板1に半導体基板1表面とは異なる結晶面方位有する素子分離溝2を形成する工程と、半導体基板1上に酸素ラジカル発生を促進する金属3又は酸素ラジカル発生を促進する金属3を含む膜を堆積する工程と、半導体基板1を酸化する工程と、金属または金属を含む膜を除去する工程とを有する。

(もっと読む)

1 - 20 / 152

[ Back to top ]