Fターム[5F032AA74]の内容

素子分離 (28,488) | 絶縁物を用いる分離 (9,448) | 素子領域側面を絶縁物で分離するもの (8,208) | 溝内埋込み分離 (7,414) | 埋込みに工夫 (1,675) | 埋込み材料を酸化するもの (56)

Fターム[5F032AA74]の下位に属するFターム

埋込み材料の一部を酸化するもの (18)

Fターム[5F032AA74]に分類される特許

1 - 20 / 38

SOIウエハおよびSOIウエハの製造方法

【課題】除電構造と素子分離構造とを有するSOIウエハを、従来より少ない工程で製造することができるSOIウエハの製造方法の提供。

【解決手段】SOIウエハの周縁部分に活性層用半導体層および絶縁酸化膜を貫通する除電用トレンチをエッチングで形成すると同時に、当該周縁部分より内側の内側部分に上記活性層用半導体層を貫通し上記絶縁酸化膜に到達する素子分離用トレンチをエッチングで形成するトレンチ形成ステップを備え、上記トレンチ形成ステップは、上記周縁部分におけるエッチングレートが、上記内側部分におけるエッチングレートよりも高いことを特徴とする。

(もっと読む)

二酸化ケイ素膜の製造方法

【課題】低収縮かつ低応力である絶縁膜を製造することができる方法の提供。

【解決手段】基板表面にポリシラザン組成物を塗布して塗膜を形成させ、引き続き前記塗膜を過酸化水素雰囲気下、50〜200℃で加熱することを含んでなることを特徴とする、二酸化ケイ素膜の製造方法。この二酸化ケイ素膜の製造方法によって各種絶縁膜などのアイソレーション構造を形成させることができる。

(もっと読む)

トレンチの埋め込み方法および成膜システム

【課題】 トレンチの内部に酸化障壁となる膜を形成しなくても、トレンチの内部に埋め込まれた埋め込み材料に空隙が発生することを抑制することが可能なトレンチの埋め込み方法を提供すること。

【解決手段】 少なくともトレンチ6の側壁に酸化膜7が形成されている半導体基板1を加熱し、半導体基板1の表面にアミノシラン系ガスを供給して半導体基板1上にシード層8を形成し、シード層8が形成された半導体基板1を加熱し、シード層8の表面にモノシランガスを供給してシード層8上にシリコン膜9を形成し、シリコン膜9が形成された半導体基板1のトレンチ6を、焼成することで収縮する埋め込み材料10を用いて埋め込み、トレンチ6を埋め込む埋め込み材料10を、水及び/又はヒドロキシ基を含む雰囲気中で焼成するとともに、シリコン膜9、及びシード層8をシリコン酸化物に変化させる。

(もっと読む)

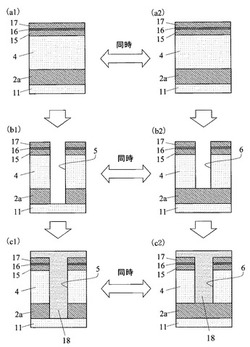

素子間分離領域の形成方法

【課題】 STIによる素子間分離において、ボイドが無く完全にトレンチを埋め込むことができ、処理時間の短縮化を図ることができる素子間分離領域の形成方法を提供する。

【解決手段】 本発明の素子間分離領域の形成方法は、酸化雰囲気中で熱処理することにより酸化して膨張し且つ絶縁性をもつに至る物質からなる半導体基板1に対し、その表面の一部分を除去して、素子間分離用のトレンチ4を形成するトレンチ形成工程と、トレンチ4を形成した半導体基板1を酸化雰囲気中で熱処理して、半導体基板1の表面を酸化膨張させ、酸化膨張により生成された絶縁物6によりトレンチ4を埋め込む酸化膨張工程と、酸化膨張工程の後に、絶縁物6により埋め込まれた部分を残して、半導体基板1のうち素子形成領域となる部分の表面を露出させる露出工程と、を含むことを特徴とする。

(もっと読む)

半導体装置の製造方法

【課題】半導体基板中に形成した素子分離溝の上部角部への電界集中によるトランジスタの電気的特性の劣化を抑制することが可能な半導体装置の製造方法を提供する。

【解決手段】半導体基板1に半導体基板1表面とは異なる結晶面方位有する素子分離溝2を形成する工程と、半導体基板1上に酸素ラジカル発生を促進する金属3又は酸素ラジカル発生を促進する金属3を含む膜を堆積する工程と、半導体基板1を酸化する工程と、金属または金属を含む膜を除去する工程とを有する。

(もっと読む)

半導体装置およびその製造方法

【課題】応力の発生が緩和され、かつ、良質な埋め込み構造を有する半導体装置、およびその製造方法を提供する。

【解決手段】第1の領域AR1、第2の領域AR2を有し、さらwに、第1の領域AR1が第1の溝TR1を、第2の領域AR2が第2の溝TR2、を有する基板の溝に絶縁膜を埋設する。このとき、第1の溝TR1、第2の溝TR2のそれぞれを、その溝の幅の相違に応じて、径の異なる第1のナノ粒子CS1、第2のナノ粒子CS2で、埋め込んで絶縁膜を形成する。

(もっと読む)

半導体装置の製造方法

【課題】分離トレンチ部分に発生する熱応力を緩和することが可能な半導体装置の製造方法を提供する。

【解決方法】SOI層20の表面に酸化膜30を形成する工程を備える。酸化膜30の表面に窒化膜40を形成する工程を備える。分離トレンチ領域R2内のSOI層20、酸化膜30、窒化膜40を除去し、第1トレンチ52を形成する工程を備える。第1トレンチ52の側壁に露出しているSOI層20を熱酸化することで、第1トレンチ52を幅狭第1トレンチ52aに変化させると共に、内部が熱酸化膜60により充填されている分離トレンチ領域R2を形成する工程を備える。窒化膜40を除去する工程を備える。アモルファスシリコン層70を形成することで、幅狭第1トレンチ52aの開口部をアモルファスシリコン層により閉塞する工程を備える。アモルファスシリコン層70を、熱酸化により熱酸化膜71へ変質させる工程を備える。

(もっと読む)

半導体装置の製造方法及び製造装置

【課題】高いアスペクト比で狭い幅の溝に、シリコン酸化膜を埋め込むことの可能な、スループットの高い半導体製造方法を提供する。

【解決手段】半導体装置の製造方法において、基板を処理室内へ搬入する工程と、炭素及び水素を含むシリコン化合物ガスを処理室内へ供給して、処理室内を第1の圧力の状態にする工程と、処理室内を前記第1の圧力にした状態において、処理室内へ供給されたシリコン化合物ガスに紫外光を照射して、基板上にシリコン酸化膜を形成する工程と、処理室内を前記第1の圧力よりも低い第2の圧力の状態にする減圧処理工程とを行う。これにより、高アスペクト比で狭い幅の溝内に、緻密なシリコン酸化膜を形成することができる。

(もっと読む)

半導体装置の製造方法

【課題】分離トレンチ部分に発生する熱応力を緩和することが可能な半導体装置の製造方法を提供する。

【解決手段】SOI層20の表面に酸化膜30を形成する工程を備える。酸化膜30の表面に窒化膜40を形成する工程を備える。分離トレンチ領域R2内のSOI層20、酸化膜30、窒化膜40を除去し、第1トレンチ52を形成する工程を備える。第1トレンチ52の側壁に露出しているSOI層20を熱酸化することで、内部が熱酸化膜60により充填されている分離トレンチ領域R2を形成する工程を備える。窒化膜40を除去する工程を備える。アモルファスシリコン層70を形成する工程を備える。分離トレンチ領域R2の熱酸化膜60およびアモルファスシリコン層70を除去し、第2トレンチ82を形成する工程を備える。アモルファスシリコン層70を熱酸化により熱酸化膜71へ変質することで、開口部72を閉塞する工程を備える。

(もっと読む)

トレンチ埋め込み用絶縁膜の形成方法

【課題】基体に形成された開口幅が狭く高アスペクトなトレンチ内に、埋め込み性が良好で、低いリーク電流を示す絶縁膜の形成方法を提供する。

【解決手段】第一の工程としてポリシロキサン化合物とシリカ粒子との縮合反応物をトレンチ構造を含む基板に塗布する塗布工程と、第二の工程として前記塗布された縮合反応物を焼成して絶縁膜を形成する焼成工程と、第三の工程として前記絶縁膜の表面を疎水化処理剤にさらす疎水化処理工程を順に行う。

(もっと読む)

ポリシラン系トレンチ埋め込み用組成物

【課題】基体に形成されたトレンチ内にシリコン酸化物を埋め込むために使用するのに好適な、トレンチへの埋め込み性が高く、硬化収縮率が小さく、かつ良好なクラック耐性を有するシリコン酸化物塗膜を与えるトレンチ埋め込み用組成物を提供すること。

【解決手段】水素化ポリシラン化合物と、シリカ粒子に由来する構造を有する反応物とを含むことを特徴とするトレンチ埋め込み用組成物を提供する。

(もっと読む)

ポリシラザン系トレンチ埋め込み用組成物

【課題】基体に形成されたトレンチ内にシリコン酸化物を埋め込むために使用するのに好適な、トレンチへの埋め込み性が高く、硬化収縮率が小さく、かつ良好なクラック耐性を有するシリコン酸化物塗膜を与えるトレンチ埋め込み用組成物を提供すること。

【解決手段】水素化ポリシラザン化合物と、シリカ粒子に由来する構造を有する反応物とを含むことを特徴とするトレンチ埋め込み用組成物を提供する。

(もっと読む)

半導体装置及びその製造方法

【課題】幅の狭い溝状領域への層間絶縁膜の形成にポリシラザンを用いた場合のシリコン酸化膜への改質が良好に行われる半導体装置及びその製造方法を提供する。

【解決手段】上面及び側面をキャップ絶縁膜107及びサイドウォール絶縁膜108で覆われた複数のビット線106間に形成された溝状領域109と、N(窒素)よりもO(酸素)を多く含み溝状領域109の内表面を連続的に覆うSiON膜10と、SiON膜10を介して溝状領域109内に埋め込まれ、ポリシラザンを改質することによって形成されたシリコン酸化膜11とを備える。

(もっと読む)

半導体装置

【課題】温度が上昇するほどキャリアの移動度を向上できる半導体装置を提供する。

【解決手段】半導体装置は、電子をキャリアとする第1絶縁ゲート型電界効果トランジスタnMOS1と、ホールをキャリアとする第2絶縁ゲート型電界効果トランジスタpMO S2と、前記半導体基板における素子分離領域の溝内に埋め込まれ、負の膨張係数を有し、動作熱により前記第1絶縁ゲート型電界効果トランジスタに引張り応力を加える第1素子分離絶縁膜11−1と、前記半導体基板における素子分離領域の溝内に埋め込まれ、正の膨張係数を有し、動作熱により前記第2絶縁ゲート型電界効果トランジスタに圧縮応力を加える第2素子分離絶縁膜11−2とを具備する。

(もっと読む)

半導体装置の製造方法

【課題】 シームを形成せず、トレンチ近傍に高い圧縮応力を生じさせることなく、トレンチ内に酸化シリコンを充填することができる半導体装置の製造方法を提供する。

【解決手段】 トレンチ30内に酸化シリコン22が充填された構造を有する半導体装置の製造方法であって、半導体基板50の表面にトレンチ30を形成する工程と、トレンチ30の中心部に隙間58が形成されるようにトレンチ30の内面に酸化シリコン層56を形成する工程と、前記隙間58にポリシリコン59を充填する工程と、半導体基板50を酸化雰囲気下で熱処理して、充填したポリシリコン59の全体を酸化シリコンに変化させる工程、を有する。

(もっと読む)

半導体装置の製造方法及び製造装置

【課題】高いアスペクト比で狭い幅の溝に、シリコン酸化膜を埋め込むことの可能な、スループットの高い半導体製造方法を提供する。

【解決手段】半導体装置の製造方法において、基板を処理室内へ搬入する工程と、炭素及び水素を含むシリコン化合物ガスを処理室内へ供給して、処理室内を第1の圧力の状態にする工程と、処理室内を前記第1の圧力にした状態において、処理室内へ供給されたシリコン化合物ガスに紫外光を照射して、基板上にシリコン酸化膜を形成する工程と、処理室内を前記第1の圧力よりも低い第2の圧力の状態にする減圧処理工程とを行う。これにより、高アスペクト比で狭い幅の溝内に、緻密なシリコン酸化膜を形成することができる。

(もっと読む)

半導体装置の製造方法

【課題】 基板の表面に微小な溝を形成することなく、トレンチ構造を形成することが可能な半導体装置の製造方法を提供する。

【解決手段】 半導体装置の製造方法であって、シリコン層と、層間絶縁膜と、マスク層を有する基板に対して、マスク層の表面からシリコン層内部に達するトレンチを形成する工程と、層間絶縁膜をトレンチ内に露出している壁面からエッチングして後退させる工程と、エッチングによってシリコン層の角部を面取りする工程と、層間絶縁膜をエッチングして側方空間を形成する工程と、トレンチ内及び側方空間内に露出しているシリコン層を酸化させてその表面にトレンチ絶縁膜を形成する工程と、トレンチ及び側方空間内にポリシリコンを充填する工程と、エッチングによってポリシリコンとマスク層の間に隙間を形成する工程と、ポリシリコンの表面にキャップ絶縁膜を形成する工程を実施する。

(もっと読む)

半導体基板の製造方法および半導体装置の製造方法

【課題】性能劣化を招く金属元素の半導体基板への侵入及び拡散を防ぐことのできる半導体基板の製造方法および半導体装置の製造方法を提供する。

【解決手段】本発明の一態様に係る半導体基板の製造方法は、半導体基板1の両面および側面に窒化膜2を形成する工程と、前記窒化膜2上の全面に、シリコンを含む酸化膜3および所定の金属を含む前駆体膜4Aを積層する工程と、前記酸化膜3と前記前駆体膜4Aとを反応させることにより、前記シリコンおよび前記所定の金属を含む自己形成バリア膜4を自己整合的に形成する工程と、を含む。

(もっと読む)

シリカ質膜の形成方法およびそれにより形成されたシリカ質膜

【課題】膜中窒素濃度が低いシリカ質膜の形成方法の提供。

【解決手段】凹凸を有する基板表面にポリシラザン組成物を塗布して塗膜を形成させ、

前記塗膜のうち、基板表面に隣接した部分のみを硬化させて、前記凹凸を有する基板の形状に沿った被覆薄膜を形成させ、

前記塗膜のうち、前記被覆薄膜形成工程において未硬化のまま残ったポリシラザン組成物を除去する

ことを含んでなるシリカ質膜の形成方法。この方法により形成されたシリカ質膜は、複数堆積することもできる。

(もっと読む)

半導体装置およびその製造方法

【課題】微細であり、かつ欠陥の少ない素子分離絶縁膜を有する半導体装置およびその製造方法を提供する。

【解決手段】半導体装置APは、シリコン基板SBと、熱酸化膜SIと、エピタキシャル膜EFとを有している。シリコン基板SBは第2の主面P2を有している。第2の主面P2に底面RCおよび側面SWを有する凹部が設けられている。熱酸化膜SIは凹部の側面SWを覆っている。エピタキシャル膜EFは、側面SWが熱酸化膜SIで覆われた凹部を第2の主面P2の高さまで埋めるように、底面RCからエピタキシャル成長している。

(もっと読む)

1 - 20 / 38

[ Back to top ]