Fターム[5F032AA70]の内容

素子分離 (28,488) | 絶縁物を用いる分離 (9,448) | 素子領域側面を絶縁物で分離するもの (8,208) | 溝内埋込み分離 (7,414) | 埋込みに工夫 (1,675) | 数回の埋込みをするもの(DAで具体的に) (373)

Fターム[5F032AA70]に分類される特許

1 - 20 / 373

SOIウエハおよびSOIウエハの製造方法

【課題】除電構造と素子分離構造とを有するSOIウエハを、従来より少ない工程で製造することができるSOIウエハの製造方法の提供。

【解決手段】SOIウエハの周縁部分に活性層用半導体層および絶縁酸化膜を貫通する除電用トレンチをエッチングで形成すると同時に、当該周縁部分より内側の内側部分に上記活性層用半導体層を貫通し上記絶縁酸化膜に到達する素子分離用トレンチをエッチングで形成するトレンチ形成ステップを備え、上記トレンチ形成ステップは、上記周縁部分におけるエッチングレートが、上記内側部分におけるエッチングレートよりも高いことを特徴とする。

(もっと読む)

半導体装置およびその製造方法

【課題】SOI基板上に形成されたMOSFETを有する半導体装置の信頼性を向上させる。

【解決手段】SOI基板SB上に形成されたマットMT内に複数のMOSFETを有する半導体装置において、BOX膜を貫き支持基板に達するコンタクトプラグCT2を形成することで、マットMTの周囲を、SOI基板SBの主面に沿う第1方向または第1方向に直交する第2方向に延在する複数のコンタクトプラグCT2により囲む。これにより、コンタクトプラグCT2をガードリングとして用い、マットMTの外部に流れる高周波信号に起因してマットMT内にノイズが発生することを防ぐ。

(もっと読む)

半導体装置の製造方法

【課題】半導体基板をエッチングする際、ハードマスクの肩落ちによるエッチング深さの基板面内での粗密差を低減する。

【解決手段】半導体基板1上に、絶縁層(10,11)とアッシング除去可能な材料層を形成する工程と、材料層をパターニングする工程と、パターニングされた材料層をマスクに、絶縁層を貫通し、少なくとも半導体基板の一部をエッチングする第1のエッチング工程と、材料層がなくなる前にエッチングを一旦停止し、残存する材料層(12)をアッシング除去する工程と、絶縁層をマスクに半導体基板を所定の深さにエッチングする第2のエッチング工程とを含む。

(もっと読む)

成膜装置及び半導体装置の製造方法

【課題】膜厚を確保することが可能な成膜装置及び半導体装置の製造方法を提供する。

【解決手段】実施形態にかかる成膜装置は溝を有する基板に液体材料を供給して前記溝内に前記液体材料を埋め込み、液層を形成する塗布部と、前記溶液層を乾燥させて固化する乾燥部と、前記乾燥中に前記液層の表面に蒸気を照射する蒸気供給部と、を備えることを特徴とする。

(もっと読む)

基板処理装置及び半導体装置の製造方法

【課題】膜応力の小さい低誘電率の絶縁膜を形成できる基板処理装置を提供する。

【解決手段】処理室内へ無機シリコンガスと酸素含有ガスを供給している状態で、励起エネルギーを処理室内へ供給して、基板表面にシリコン酸化膜を形成するシリコン酸化膜形成工程と、処理室内へ有機シリコンガスを供給している状態で、励起エネルギーを処理室内へ供給して、基板表面にシリコン膜を形成するシリコン膜形成工程と、を行うことにより、処理室内の基板表面に絶縁膜を形成するよう、基板処理装置を構成する。

(もっと読む)

半導体装置およびその製造方法

【課題】デバイス特性の向上を図る。

【解決手段】半導体装置の製造方法は、半導体基板10に基板部10aと前記基板部上のフィン部10bとを形成する工程と、前記フィン部の側面上に、第1シリコン酸化膜12を形成する工程と、前記第1シリコン酸化膜の側面上に、前記シリコン酸化膜の上面より低い上面を有するポリシラザン膜13を形成する工程と、前記ポリシラザン膜を窒化および酸化することでシリコン酸窒化膜13aに転換する工程と、全面に、前記フィン部を覆うように第2シリコン酸化膜14を形成する工程と、前記第1シリコン酸化膜および前記第2シリコン酸化膜をエッチングすることにより、前記第1シリコン酸化膜の上面を前記シリコン酸窒化膜の上面以下の高さにする工程と、前記フィン部内に高濃度半導体層40を形成する工程と、を具備する。

(もっと読む)

半導体装置、及び半導体装置の製造方法

【課題】ランプアニールによるレイアウトに起因した温度バラつきを低減する。

【解決手段】この半導体装置10は、基板100と、基板100に埋め込まれた素子分離領域200と、基板100のうち、素子分離領域200の無い領域に形成された不純物層(エクステンション領域322、ソース領域324、エクステンション領域342、及びドレイン領域344)と、を備える。この素子分離領域200は、たとえば、波長300nm以上890nm以下においてSiO2よりも光吸収係数が大きい材料から形成されている光吸収層220を含む。

(もっと読む)

半導体装置及びその製造方法

【課題】コンタクトホールの一部が素子分離領域上に配置された構造の半導体装置において、短絡及び接合漏れ電流の増大を抑制する。

【解決手段】半導体装置50は、半導体基板10における活性領域10aを取り囲むように形成された溝15bに素子分離絶縁膜15aが埋め込まれた素子分離領域15と、活性領域10aに形成された不純物領域26と、半導体基板10上を覆う層間絶縁膜28と、層間絶縁膜28を貫通し、活性領域10a上及び素子分離領域15上に跨って形成されたコンタクトプラグ34と、少なくともコンタクトプラグ34下方において、不純物領域26上に形成された金属シリサイド膜33とを備える。素子分離領域15は、コンタクトプラグ34の下方において、素子分離絶縁膜15と活性領域10aとの間に設けられた保護絶縁膜35を更に有する。

(もっと読む)

半導体装置およびその製造方法

【課題】第1のトランジスタと第2のトランジスタが、ぞれぞれのドレイン領域とソース領域を共有して同一の半導体基板上に形成される構成の半導体装置の製造において、それぞれのトランジスタのソース領域およびドレイン領域の直下に埋め込み絶縁膜を効率的に形成できる製造方法を提供する。

【解決手段】半導体基板上にそれぞれのトランジスタのソース領域およびドレイン領域に対応してトレンチを形成し、前記トレンチをSiGe混晶層と半導体層を順次形成することにより充填し、さらに第1のトランジスタのソース領域および第2のトランジスタのドレイン領域直下のSiGe混晶層を、素子分離溝を介して選択エッチングにより除去し、第1のトランジスタのドレイン領域および第2のトランジスタのソース領域として共有される拡散領域直下のSiGe混晶層を、前記拡散領域に形成した孔を介して選択エッチングし、除去する。

(もっと読む)

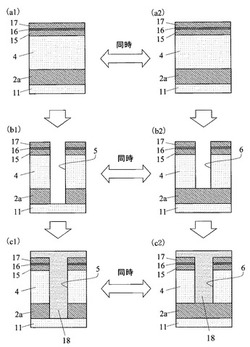

半導体装置及びその製造方法

【課題】製造プロセスが複雑になるといったことを防ぎつつ、n型及びp型MOSトランジスタについて両方の性能を向上させた半導体装置を提供する。

【解決手段】半導体基板1の面内に、n型MOSトランジスタと、p型MOSトランジスタとを備える半導体装置であって、n型MOS型トランジスタが形成される第1の拡散層2aの間を絶縁分離する第1の絶縁層3aと、p型MOS型トランジスタが形成される第2の拡散層2cの間を絶縁分離する第2の絶縁層3bとを備え、第1の絶縁層3aは、半導体基板1の表層に形成された第1の溝部4aに、シリコン窒化膜5と、このシリコン窒化膜5の上にシリコン酸化膜6とを埋め込むことによって形成され、第2の絶縁層3bは、半導体基板1の表層に第1の溝部4aよりも幅広となるように形成された第2の溝部4bに、シリコン酸化膜6を埋め込むことによって形成されている。

(もっと読む)

半導体装置およびその製造方法

【課題】ウェル給電領域の面積を縮小して、半導体装置の微細化を行う。素子形成領域間のウェル電位のばらつきを抑制する。分離部の幅を細くする。

【解決手段】半導体装置は、半導体基板の表面に形成され、底部がウェル領域内に位置する溝状の分離部を有する。分離部は、ウェル領域と電気的に接続された導体配線と、底部に導体配線を埋め込む絶縁膜とを有する。分離部に囲まれるようにして区画されたウェル領域の一部は素子形成領域を形成し、素子形成領域には半導体素子が配置される。

(もっと読む)

半導体装置及びその製造方法

【課題】半導体基板を貫通する貫通電極の周囲に形成される環状の絶縁分離部において、絶縁分離部を構成する酸化膜の応力により絶縁分離部周囲の半導体基板が変形する。

【解決手段】絶縁分離部の基板側に深さ方向に圧縮応力を与える第1の膜4を形成し、第1の膜4上に深さ方向に引張応力を与える第2の膜6膜を形成し、その際、第1及び第2の膜の膜厚を圧縮応力と引張応力とがほぼ釣り合うように調整する。

(もっと読む)

半導体装置

【課題】 素子特性の劣化を抑制する。

【解決手段】 実施形態による半導体装置は、トランジスタ領域を有する半導体装置であって、トランジスタ領域は、基板上に形成された半導体領域と、半導体領域に隣接する素子分離領域と、ラテラルエピタキシャル層を備え、半導体領域上及び半導体領域と素子分離領域との間で横方向に成長するエピタキシャル層と、を具備する。

(もっと読む)

不揮発性半導体記憶装置およびその製造方法

【課題】クラックや結晶欠陥の発生なしに高電圧トランジスタの素子領域間の耐圧を向上できるようにした不揮発性半導体記憶装置およびその製造方法を提供する。

【解決手段】不揮発性半導体記憶装置は、メモリセル領域の第1素子分離絶縁層が当該メモリセル領域の第1素子分離溝内に第1の酸化膜を埋め込んで構成され、第1の酸化膜の上面が半導体基板の上面と第1ゲート電極の上面との間に存在するように構成されている。

周辺領域の第2素子分離絶縁層は、周辺領域の第2素子分離溝内の全体に埋込まれると共にその上面が半導体基板の上面の上方に突出した第1の酸化膜と、当該第1の酸化膜上に積層され、その上面が第1導電膜の上面より上方に突出している第2の酸化膜とで構成されている。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】隣接セル間干渉を抑制した不揮発性半導体記憶装置及びその製造方法を提供する。

【解決手段】実施形態によれば、第1メモリストリングと、ソースコンタクトと、第2メモリストリングと、シールド導電層と、を備えた不揮発性半導体記憶装置を提供する。第1メモリストリングは、第1軸に沿って並ぶ第1メモリセル及び第2メモリセルを含む。ソースコンタクトは、第1メモリストリングのソース側の端に設けられる。第2メモリストリングは、第1軸に対して直交する第2軸に沿って第1メモリセルと並ぶ第3メモリセルを含み、第1軸に沿って延在する。シールド導電層は、第1メモリストリングと第2メモリストリングとの間において第1軸に沿って延在し、ソースコンタクトと電気的に接続される。

(もっと読む)

半導体装置およびその製造方法

【課題】素子分離用ゲート電極のみのしきい値電圧を高くすることができ、素子分離用ゲート電極の底部にチャネルが形成されない半導体装置を提供する。

【解決手段】半導体基板1に形成された複数の活性領域と、これら活性領域同士を区画する素子分離領域と、活性領域内を複数の素子領域に区画する第1素子分離用トレンチ32Aと、隣接する第1素子分離用トレンチ32A間に設けられ、第1素子分離用トレンチ32Aの深さよりも浅く形成されたゲートトレンチ31Aと、絶縁膜25を介して第1素子分離用トレンチ32A内に形成された素子分離用電極32と、ゲート絶縁膜26Aを介してゲートトレンチ31A内に形成されたゲート電極31と、を具備してなり、素子分離用電極32底部に成膜されている絶縁膜25の膜厚が、ゲート電極31の底部に成膜されているゲート絶縁膜26Aの膜厚よりも厚いことを特徴とする。

(もっと読む)

絶縁膜の形成方法

【課題】均一で高い充填密度を有し、かつ欠陥が少ない絶縁膜を形成することができる方法の提供。

【解決手段】基板表面に、二酸化ケイ素微粒子と、ポリマーと、界面活性剤と、分散媒とを含む二酸化ケイ素分散液を塗布し、次いでポリシラザン組成物を塗布した後、加熱して絶縁膜を形成させる、絶縁膜の形成方法。

(もっと読む)

半導体装置の製造方法

【課題】塗布法を用いて形成される酸化膜を溝の内部に充填した溝型の素子分離部を有する半導体装置において、溝の内部におけるボイドの発生を抑制して、埋め込み不良を低減することのできる技術を提供する。

【解決手段】0.2μm以下の溝幅を有する溝4Sの内部に埋まるポリシラザン膜の上面がパッド絶縁膜3の上面よりも高く、かつ1.0μm以上の溝幅を有する溝4Lの内部に埋まるポリシラザン膜の上面がパッド絶縁膜3の上面よりも低くなるように、半導体基板1の主面上にポリシラザン膜を形成し、続いて、300℃以上の熱処理を行うことにより、ポリシラザン膜を酸化シリコン(SiO2)からなる第1埋め込み膜8へ転化すると同時に、溝4Sの上部に局所的に生じたボイドを消滅させる。

(もっと読む)

半導体装置

【課題】バンド間トンネリングが横方向に起こる構造を有し、バンド間トンネリングが起こる領域が大きいトンネルトランジスタを備える半導体装置を提供する。

【解決手段】第1上面S1と、第1上面S1よりも高さの低い第2上面S2と、第1上面と第2上面との間に存在する段差側面S3と、を有する段差が形成された基板。さらに、基板の段差側面S3と第2上面S2とに連続して形成されたゲート絶縁膜と、基板の段差側面S3に形成されたゲート絶縁膜に接するよう、第2上面S2上にゲート絶縁膜131を介して形成されたゲート電極132とを備える。さらに、基板内において、第1上面の下方に形成された第1導電型のソース領域121と、第2上面の下方に形成された第2導電型のドレイン領域122と、段差側面S3とソース領域122との間に形成された第2導電型の側方拡散領域123とを備える。

(もっと読む)

半導体記憶装置及びその製造方法

【課題】メモリセルアレイおよび周辺回路領域の素子分離領域の深さを調節しつつ、周辺回路部の素子分離領域に形成されるマイクロトレンチ形状の影響を抑制し、信頼性の高い半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、半導体基板上に設けられデータを記憶する複数のメモリセルを含むメモリセルアレイと、半導体基板上に設けられメモリセルアレイを制御する周辺回路部とを備えている。素子分離部は、複数のメモリセルおよび周辺回路部が形成されるアクティブエリア間に設けられている。側壁膜は、周辺回路部におけるアクティブエリアの側面に設けられている。

(もっと読む)

1 - 20 / 373

[ Back to top ]