Fターム[5F032AA43]の内容

素子分離 (28,488) | 絶縁物を用いる分離 (9,448) | 素子領域側面を絶縁物で分離するもの (8,208) | 溝内埋込み分離 (7,414) | 埋込み材料 (3,229)

Fターム[5F032AA43]の下位に属するFターム

酸化シリコン (2,174)

窒化シリコン (320)

多結晶シリコン、非晶質シリコン (291)

ガラス(PSG、BSG、ASG) (158)

有機材料 (68)

その他 (197)

Fターム[5F032AA43]に分類される特許

1 - 20 / 21

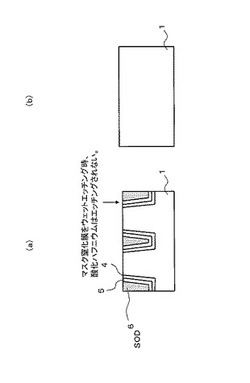

半導体装置及びその製造方法

【課題】エッチングによるマスク窒化膜除去時に、STI構造を構成しているライナー膜に劣化が発生することを防止する。

【解決手段】半導体基板に形成したトレンチ内に素子分離構造を形成する工程を含み、前記素子分離構造を形成する工程は、前記トレンチ内の前記半導体基板上にパッド酸化膜を形成する工程と、前記パッド酸化膜上にALD法によりライナー膜を形成する工程と、前記ライナー膜上にSOD膜を形成する工程と、を含む半導体装置の製造方法。ライナー膜は酸化ハフニウム膜が好ましい。

(もっと読む)

バルクFinFET中のSiフィンのフィン下部近くのSTI形状

【課題】半導体フィンとフィン型電界効果トランジスタの構造、及び、製造方法を提供する。

【解決手段】集積回路構造の形成方法は、頂面を有する半導体基板を提供するステップと、半導体基板中に、第1絶縁領域と第2絶縁領域を形成するステップと、第1絶縁領域と第2絶縁領域を陥凹するステップと、からなる。第1絶縁領域と第2絶縁領域の残り部分の頂面は平らな表面であるか、或いは、窪み表面である。第1絶縁領域と第2絶縁領域の除去部分間の半導体基板の部分、及び、隣接する部分は、フィンを形成する。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】素子分離構造の面積を増大させることなく、素子分離構造の表面の後退量を低減させる。

【解決手段】半導体基板11の表面よりも低い位置に埋め込み絶縁層12を埋め込み、埋め込み絶縁層12と材料の異なるキャップ絶縁層13を半導体基板11と埋め込み絶縁層12と間の段差12aの肩の部分にかからないようにして埋め込み絶縁層12上に形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】pnコラム領域を用いて複数の両面電極素子が構成された半導体装置において、装置を小型化しつつ過渡的信号による短絡の発生を抑制する。

【解決手段】絶縁分離トレンチにより、半導体基板において複数の素子形成領域が区分された半導体装置であって、両面電極素子の形成領域として、半導体基板にpnコラム領域を設けた。そして、両面電極素子を構成する各素子形成領域がpnコラム領域を構成するp導電型半導体領域とn導電型半導体領域を含むように絶縁分離トレンチを形成した。また、両面電極素子としてnチャネル型両面電極素子とpチャネル型両面電極素子を含み、nチャネル型両面電極素子の素子形成領域では、n導電型半導体領域が並設方向両端に位置して絶縁分離トレンチに接し、pチャネル型両面電極素子の素子形成領域では、p導電型半導体領域が並設方向両端に位置して絶縁分離トレンチに接するようにした。

(もっと読む)

光電変換装置及び撮像システム

【課題】光電変換部で発生した信号電荷であるホールを電荷蓄積領域に効率良く収集する。

【解決手段】光電変換装置は、半導体基板に配された複数の光電変換部を有し、前記光電変換部は、第1の不純物を含むP型の電荷蓄積領域と、前記P型の電荷蓄積領域とフォトダイオードを構成するN型のウエル部とを備える。前記ウエル部は、砒素を第1の濃度で含むN型の第1の半導体領域と、前記第1の半導体領域の下に配され、砒素を前記第1の濃度より低い第2の濃度で含むN型の第2の半導体領域と、前記第2の半導体領域の下に配され、第2の不純物を前記第1の濃度よりも高い第3の濃度で含むN型の第3の半導体領域とを含む。

(もっと読む)

半導体装置

【課題】温度が上昇するほどキャリアの移動度を向上できる半導体装置を提供する。

【解決手段】半導体装置は、電子をキャリアとする第1絶縁ゲート型電界効果トランジスタnMOS1と、ホールをキャリアとする第2絶縁ゲート型電界効果トランジスタpMO S2と、前記半導体基板における素子分離領域の溝内に埋め込まれ、負の膨張係数を有し、動作熱により前記第1絶縁ゲート型電界効果トランジスタに引張り応力を加える第1素子分離絶縁膜11−1と、前記半導体基板における素子分離領域の溝内に埋め込まれ、正の膨張係数を有し、動作熱により前記第2絶縁ゲート型電界効果トランジスタに圧縮応力を加える第2素子分離絶縁膜11−2とを具備する。

(もっと読む)

半導体素子の製造方法および半導体素子

【課題】 半導体素子の微細パターン製造方法を提供する。

【解決手段】フィーチャー層310の第1領域Aには第1マスク構造物を形成し、第2領域Bには第2マスク構造物を形成する。各々デュアルマスク層とエッチングマスク層とを含むように第1マスク構造物及び第2マスク構造物を形成する。第1マスク構造物及び第2マスク構造物のエッチングマスクパターンを等方性エッチングし、第1マスク構造物からエッチングマスクパターンを除去する。第1マスク構造物及び第2マスク構造物の両側壁にスペーサ350A、350Bを形成する。第2マスク構造物上にあるエッチングマスクパターンをマスクとして第1領域Aで間にボイドが形成されるように側壁スペーサ350Aを含む第1マスクパターンと、第2領域Bで間に第2マスク構造物が介在するように側壁スペーサ350B、350Cを含む第2マスクパターンを形成する。

(もっと読む)

低いエッチング速度の誘電体ライナを用いたギャップ充填の改善

トレンチを充填する方法が記述され、その方法は、フッ素を含むエッチング化学作用において、酸化シリコンと誘電体ライナのエッチング速度の比が高い状態で誘電体ライナを堆積させることを含む。酸化シリコンはトレンチの中に堆積され、トレンチの頂部付近のギャップを再び開くまたは広げるようにエッチングされる。誘電体ライナは、エッチングプロセスの間、下にある基板を保護し、したがって、ギャップをより広くすることができるようになる。トレンチの中に再び酸化シリコンを堆積させて、トレンチを実質的に充填する。  (もっと読む)

(もっと読む)

半導体装置

【課題】薄膜SOI領域を有する基板において、基板に第1半導体素子10と異なる第2半導体素子30、40を形成した際に、この第2半導体素子30、40の特性を従来の半導体装置より向上させることができる半導体装置を提供する。

【解決手段】基板のうち第1半導体素子10が形成される第1半導体素子形成領域1とは異なる部分を第2半導体素子形成領域2とし、第2半導体素子形成領域2に、基板の表裏を貫通する第1貫通トレンチ31を形成し、第1貫通トレンチ31の側壁に絶縁膜32を形成すると共に第1貫通トレンチ31の内部に第1埋込材料33を埋め込む。そして、第1埋込材料33を有する第2半導体素子30、40を形成して半導体装置を構成する。

(もっと読む)

半導体装置及びその製造方法

【課題】微細化しても動作特性の劣化が生じないSTI構造の半導体装置及びその製造方法を得る。

【解決手段】NMOSトランジスタのゲート電極部をNMOS仕事関数制御メタル層7及びゲート主電極5により構成する。NMOS仕事関数制御メタル層7をスパッタ法により形成され、ディボット部2dが設けられるエッジ近傍領域である領域bにおける膜厚は、他の領域である領域aにおける膜厚より薄く形成される。したがって、NMOS仕事関数制御メタル層7に関し、領域bにおける実効仕事関数が領域aにおける実効仕事関数に比べ、ミッドギャップよりに設定される。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】キャリアの移動度が高い歪SOI構造を、結晶欠陥少なく且つ安価に形成できるようにした半導体装置の製造方法及び半導体装置を提供する。

【解決手段】Si基板1上にSiGe層とSi層5とを順次形成し、その上にSi3N4膜9、13を形成する。次に、Si3N4膜9、13と、Si層5及びSiGe層を貫く支持体穴hを形成する。そして、支持体穴hを埋め込むようにSiO2膜21を形成する。次に、SiO2膜21とSi層5とを部分的にエッチングして、SiGe層を露出させる溝Hを形成する。そして、この溝Hを介してSiGe層をエッチングすることにより、Si層5とSi基板1との間に空洞部25を形成し、空洞部25を埋め込むようにSiO2膜を形成する。この際、Si3N4膜9が有する圧縮応力と、Si3N4膜13が有する引っ張り応力とをSi層5にそれぞれ作用させてSi層5の歪を増大させる。

(もっと読む)

半導体素子のハードマスクパターン形成方法

【課題】マトリックス状に配列された露光装備の解像度限界以下の活性領域を定義するためのハードマスクパターンの形成方法を提供する。

【解決手段】半導体基板101上に、ハードマスク膜103と第1のマスクパターン105を形成する。第1のマスクパターンと交差する第1のパターンと、第1のマスクパターン間に位置する第2のパターンを含む第2のマスクパターン107を形成する。第1のパターン間に第3のマスクパターンを形成する。第1のパターンと第1のマスクパターンが交差する領域に第1のマスクパターンが残留し、第1のパターンと第2のパターンが交差する領域に第2のパターンが残留するようにエッチングを行う。残留する第1のマスクパターン及び第2のマスクパターンをエッチングマスクとして用い、ハードマスクパターンを形成する。

(もっと読む)

フローティングボディ素子及びバルクボディ素子を有する半導体素子及びその製造方法

【課題】フローティングボディ素子及びバルクボディ素子を有する半導体素子及びその製造方法を提供する。

【解決手段】この半導体素子の製造方法は、バルクボディ素子領域及びフローティングボディ素子領域を有する基板を準備する工程を含む。バルクボディ素子領域の基板の活性領域を画定するとともに、フローティングボディ素子領域のうち第1素子領域の基板上に順に積層された第1犠牲パターン及び第1活性パターンを画定する素子分離膜を形成する。フォトリソグラフィ及びエッチング工程を用いて素子分離膜に第1犠牲パターンの一部分を露出させる第1リセス領域を形成する。第1犠牲パターンを除去して第1活性パターン下部に第1空間を形成する。第1空間の内壁及び第1リセス領域の内壁に第1埋込誘電膜を形成する。第1埋込誘電膜を有する基板上に少なくとも第1空間を埋め込む第1埋込パターンを形成する。

(もっと読む)

半導体装置およびトレンチの形成方法

【課題】素子の電気的特性を向上することのできる半導体装置およびトレンチの形成方法を提供する。

【解決手段】トレンチの形成方法は、SiCよりなるn-ドリフト層2にトレンチ3を形成するトレンチ形成方法であって、n-ドリフト層2の主表面2aに溝を形成する溝工程と、この溝をエッチングしてトレンチ3を形成するトレンチ工程とを備えている。溝の幅は深さ方向に向かって単調減少している。トレンチ3の各面3a、3bおよび3cは互いに鋭角をなして接することなく、深さ方向に湾曲している。

(もっと読む)

半導体集積回路基板の絶縁構造およびその製作方法

半導体基板の絶縁領域は誘電体で充填されたトレンチおよびフィールド酸化領域を含む。トレンチおよびフィールド酸化領域の主要部分の誘電体材料とは類似しない誘電体材料の保護キャップが用いられて後のプロセス工程中に構造を侵食から保護する。絶縁構造の上面は基板の表面と同一平面上にある。フィールドドーピング領域はフィールド酸化領域の下に形成されてもよい。異なる素子の要求に応えるために、絶縁構造は異なる幅および深さを有する。  (もっと読む)

(もっと読む)

半導体構造およびその製造方法(垂直SOIトレンチSONOSセル)

【課題】垂直トレンチ半導体・酸化物・窒化物・酸化物・半導体(SONOS)記憶セルがセミコンダクタ・オン・インシュレータ(SOI)基板に作られた半導体メモリ素子を提供すること。

【解決手段】この記憶セルは、埋込み絶縁層で互いに隔てられた上部半導体層と下部半導体層を含むセミコンダクタ・オン・インシュレータ基板と、前記セミコンダクタ・オン・インシュレータ基板の中に位置する少なくとも1つの垂直トレンチSONOS記憶セルと、を備え、前記少なくとも1つの垂直トレンチSONOS記憶セルは、前記垂直トレンチの下に位置するソース拡散と、前記垂直トレンチの一方の側に位置する選択ゲート・チャネルと、前記選択ゲート・チャネルの上に接触して位置している外方拡散/Si含有ブリッジと、前記ブリッジの上部に近接しかつ接触して位置しているシリサイド化ドープ領域とを含み、前記ブリッジは、前記上部半導体層、前記埋込み絶縁層および前記下部半導体層の中に存在している。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】素子分離領域から発生する結晶欠陥等の発生を低減するための半導体装置の製造方法を提供する。

【解決手段】本発明にかかる半導体装置は、(a)半導体層10に第1の溝210からなる第1認識マークを形成する工程と、(b)第1認識マーク210を用いて、半導体層にウェル20を形成する工程と、(c)半導体層の上に、少なくとも第1認識マークを含み、該第1認識マークの平面形状と比して大きい平面形状の第1の開口42を有するマスク層M1を形成する工程と、(d)マスク層M1を用いて、半導体層をエッチングすることにより第2の溝からなる第2認識マークと、を形成する工程と、(e)半導体層に、素子分離絶縁層22を形成する工程と、(f)半導体層に、第2認識マークを用いてトランジスタ100を形成する工程と、を含む。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】素子分離領域から発生する結晶欠陥等の発生を低減するための半導体装置の製造方法を提供する。

【解決手段】本発明の半導体装置の製造方法は、(a)半導体層10に、凹部の第1認識マーク210を形成する工程と、(b)第1認識マーク210を用いて、半導体層10にウェル20を形成する工程と、(c)半導体層10に素子分離絶縁層22を形成する工程と、(d)第1認識マーク210の凹部210の内面を覆う絶縁層214を形成する工程と、(e)絶縁層214の上に凹部210を埋め込む絶縁層216を形成し、第2認識マーク200を形成する工程と、(f)半導体層10に、第2認識マーク200を用いてトランジスタ100を形成する工程と、を含む。

(もっと読む)

半導体装置の製造方法

【課題】 半導体装置の製造方法に関し、製造工程を大幅に増加することなく、埋込酸化膜に起因する圧縮応力の影響を低減するとともに、ライナーSiN膜に起因するキャリアのトラップを解消する。

【解決手段】 半導体基板1表面上に研磨のストッパ層2を形成したのち、ストッパ層2を介して半導体基板1に素子分離用トレンチ3を形成し、次いで、少なくともトレンチ3の内表面を覆うようにSiN膜或いはSiON膜からなる窒化系ライナー膜4を堆積したのち、プラズマ照射によってトレンチ3内に堆積した窒化系ライナー膜4中の窒素を減少させ、次いで、酸化膜7を堆積させてトレンチ3を埋め込んだのち、ストッパ層2上に堆積した前記酸化膜7を研磨により除去する。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体装置の放熱特性を改善する。

【解決手段】素子分離絶縁体に絶縁性放熱材料10を用いることで、活性領域で発生した熱を横方向から放熱することが可能となる。さらに、外部から絶縁性放熱材料に繋がる放熱ビア11を設けることで、熱を半導体装置外部へと効率よく放熱する。

(もっと読む)

1 - 20 / 21

[ Back to top ]