Fターム[5F032AA50]の内容

素子分離 (28,488) | 絶縁物を用いる分離 (9,448) | 素子領域側面を絶縁物で分離するもの (8,208) | 溝内埋込み分離 (7,414) | 埋込み材料 (3,229) | 有機材料 (68)

Fターム[5F032AA50]に分類される特許

1 - 20 / 68

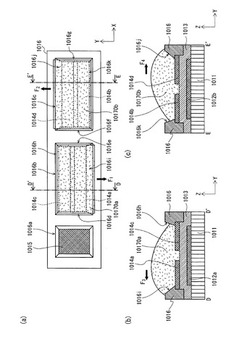

薄膜トランジスタ装置とその製造方法、有機EL表示素子、および有機EL表示装置

【課題】有機半導体層の形成に際して、不所望の領域への有機半導体層の形成を抑制し、且つ、隣接する開口部間でのインクの混合を抑制することにより、高い品質を備える薄膜トランジスタ装置とその製造方法、有機EL表示素子、および有機EL表示装置を提供する。

【解決手段】隔壁1016には、3つの開口部1016a,1016b,1016cが開けられている。開口部1016b,1016cの各底部には、ソース電極1014a,1014b、ドレイン電極1014c,1014dが露出し、各々がチャネル部として機能する部分である。開口部1016bを臨む側面部のうち、側面部1016d,1016eは、側面部1016iに比べ、傾斜が相対的に急峻な斜面である。開口部1016cを臨む側面部のうち、側面部1016fは、側面部1016jに比べ、傾斜が相対的に急峻な斜面である。

(もっと読む)

成膜装置及び半導体装置の製造方法

【課題】膜厚を確保することが可能な成膜装置及び半導体装置の製造方法を提供する。

【解決手段】実施形態にかかる成膜装置は溝を有する基板に液体材料を供給して前記溝内に前記液体材料を埋め込み、液層を形成する塗布部と、前記溶液層を乾燥させて固化する乾燥部と、前記乾燥中に前記液層の表面に蒸気を照射する蒸気供給部と、を備えることを特徴とする。

(もっと読む)

半導体装置

【課題】可撓性を有し、曲げ等の物理的変化に対して耐性を有する半導体装置および当該

半導体装置の作製方法を提供することを目的とする。

【解決手段】可撓性を有する基板上に設けられた、半導体膜、半導体膜上にゲート絶縁膜

を介して設けられたゲート電極およびゲート電極を覆って設けられた層間絶縁膜とを有す

る複数のトランジスタと、複数のトランジスタの間に設けられた屈折部分とを有し、屈折

部分は、層間絶縁膜に設けられた開口部に層間絶縁膜より弾性率が低い物質が充填されて

設けられている。また、本発明では、開口部に充填する物質として他にも、層間絶縁膜よ

りガラス転移点が低い物質や塑性を有する物質を設けることができる。

(もっと読む)

不揮発性半導体記憶装置およびその製造方法

【課題】クラックや結晶欠陥の発生なしに高電圧トランジスタの素子領域間の耐圧を向上できるようにした不揮発性半導体記憶装置およびその製造方法を提供する。

【解決手段】不揮発性半導体記憶装置は、メモリセル領域の第1素子分離絶縁層が当該メモリセル領域の第1素子分離溝内に第1の酸化膜を埋め込んで構成され、第1の酸化膜の上面が半導体基板の上面と第1ゲート電極の上面との間に存在するように構成されている。

周辺領域の第2素子分離絶縁層は、周辺領域の第2素子分離溝内の全体に埋込まれると共にその上面が半導体基板の上面の上方に突出した第1の酸化膜と、当該第1の酸化膜上に積層され、その上面が第1導電膜の上面より上方に突出している第2の酸化膜とで構成されている。

(もっと読む)

二酸化ケイ素膜の製造方法

【課題】低収縮かつ低応力である絶縁膜を製造することができる方法の提供。

【解決手段】基板表面にポリシラザン組成物を塗布して塗膜を形成させ、引き続き前記塗膜を過酸化水素雰囲気下、50〜200℃で加熱することを含んでなることを特徴とする、二酸化ケイ素膜の製造方法。この二酸化ケイ素膜の製造方法によって各種絶縁膜などのアイソレーション構造を形成させることができる。

(もっと読む)

トレンチの埋め込み方法および成膜装置

【課題】 トレンチの微細化がさらに進展しても、トレンチの内部に、膨張可能な膜及び酸化障壁となる膜を形成することが可能なトレンチの埋め込み方法を提供すること。

【解決手段】 トレンチ内部に酸化障壁膜の形成工程(ステップ3)、酸化障壁膜上に膨張可能な膜の形成工程(ステップ4)、焼成することで収縮する埋め込み材でトレンチを埋め込む工程(ステップ5)、埋め込み材の焼成工程(ステップ6)と、を含み、ステップ3の工程が、アミノシラン系ガスを供給して、トレンチの内部に第1のシード層を形成する工程(ステップ31)、第1のシード層上に窒化シリコン膜を形成する工程(ステップ32)と、を含み、ステップ4の工程が、アミノシラン系ガスを供給して、窒化シリコン膜上に第2のシード層を形成する工程(ステップ41)と、第2のシード層上にシリコン膜を形成する工程(ステップ42)と、を含む。

(もっと読む)

基板処理装置、及び成膜システム

【課題】1つの実施形態は、例えば、CVD装置による成膜処理に対する新規な前処理を行うことができる基板処理装置及び成膜システムを提供することを目的とする。

【解決手段】1つの実施形態によれば、CVD装置による成膜処理を行う基板の前処理を行なうための基板処理装置であって、前記基板を保持する基板ステージが配された基板処理室と、前記基板処理室内で前記基板ステージを介して前記基板を加熱する加熱部と、前記基板処理室内で、前記加熱部により加熱された前記基板の表面を酸化する酸化処理部と、前記基板処理室内で、前記酸化処理部により酸化された前記基板の表面に有機溶剤を塗布する塗布処理部とを備えたことを特徴とする基板処理装置が提供される。

(もっと読む)

シリカ系絶縁膜形成用塗布液

【課題】ポットライフが長く、焼成してシリコン酸化物としたときの硬化収縮率が小さく、更にクラック耐性に優れかつ耐電圧のばらつきが小さい絶縁膜を形成できる縮合反応物溶液の提供。

【解決手段】(I)(i)下記一般式(1):R1nSiX14-n (1){式中、nは0〜3の整数であり、R1は水素原子又は炭素数1〜10の炭化水素基であり、X1はハロゲン原子、炭素数1〜6のアルコキシ基又はアセトキシ基である}で表されるシラン化合物に由来するポリシロキサン化合物と、(ii)シリカ粒子と、を少なくとも含有する縮合成分を縮合反応させて得られる縮合反応物、及び(II)溶媒を含み、該一般式(1)で表されるシラン化合物が4官能シラン化合物及び3官能シラン化合物を少なくとも含有し、該シリカ粒子中の炭素量が0.05質量%以上0.65質量%未満である、縮合反応物溶液。

(もっと読む)

シャロートレンチアイソレーション膜のためのアミノシラン

【課題】記憶及び論理回路を含む半導体基材、例えば、1つ又は複数の集積回路構造をその上に有するシリコンウェハにおいて用いられるシャロートレンチアイソレーションのための高アスペクト比の特徴のギャップを充填するための酸化条件下で二酸化ケイ素含有膜をスピンオン堆積させる方法を提供する。

【解決手段】高アスペクト比の特徴を有する半導体基材を用意する工程、該半導体基材を低分子量のアミノシランを含む液体配合物と接触させる工程、該半導体基材上に該液体配合物を塗布することにより膜を形成する工程、及び該膜を酸化条件下において高温で加熱する工程を含む方法が提供される。この方法のための組成物もまた記載される。

(もっと読む)

半導体装置及びその製造方法

【課題】Cdsubの低減化を通じて、出力容量Cossの低減化に寄与する半導体装置及びその製造方法を提供する。

【解決手段】半導体基板1とこの半導体基板1上に埋め込み絶縁層を介して形成された第1導電型の半導体層とを有するSOI基板と、第1導電型の半導体層からなる活性領域3内に形成された素子領域と、素子領域の少なくとも1つに接続される外部取り出し用の電極(ドレインパッド9p)とを有する半導体装置において、外部取り出し用の電極9p下に位置する活性領域が、埋め込み絶縁層2に到達するように形成された絶縁分離領域11で囲まれており、絶縁分離領域11で分離された活性領域3と、外部取り出し用の電極9pとの間に絶縁体13が配されたことを特徴とする。

(もっと読む)

半導体装置の製造方法

【課題】低コストで高い信頼性を有する逆阻止型の半導体装置およびその製造方法を提供する。

【解決手段】半導体チップを構成する表面構造133、裏面構造134を形成した薄い半導体ウェハ101を両面粘着テープ137で支持基板141に貼り付け、薄い半導体ウェハ101にスクライブラインとなるトレンチを湿式異方性エッチングで結晶面を出して形成し、結晶面が露出したトレンチの側面に逆耐圧を維持する分離層145を裏面拡散層であるpコレクタ領域110と接して表面側に延在するようにイオン注入と低温アニールまたはレーザーアニールで形成する。レーザーダイシングを行って、分離層145の下でコレクタ電極111を過不足なくきれいに切断した後、両面粘着テープ137をコレクタ電極111から剥がして半導体チップとすることで逆阻止型の半導体装置を形成する。

(もっと読む)

トレンチの埋め込み方法および成膜システム

【課題】 トレンチの内部に酸化障壁となる膜を形成しなくても、トレンチの内部に埋め込まれた埋め込み材料に空隙が発生することを抑制することが可能なトレンチの埋め込み方法を提供すること。

【解決手段】 少なくともトレンチ6の側壁に酸化膜7が形成されている半導体基板1を加熱し、半導体基板1の表面にアミノシラン系ガスを供給して半導体基板1上にシード層8を形成し、シード層8が形成された半導体基板1を加熱し、シード層8の表面にモノシランガスを供給してシード層8上にシリコン膜9を形成し、シリコン膜9が形成された半導体基板1のトレンチ6を、焼成することで収縮する埋め込み材料10を用いて埋め込み、トレンチ6を埋め込む埋め込み材料10を、水及び/又はヒドロキシ基を含む雰囲気中で焼成するとともに、シリコン膜9、及びシード層8をシリコン酸化物に変化させる。

(もっと読む)

素子分離材料用塗布液、素子分離材料用塗布液の作製方法、素子分離層用薄膜、及び、素子分離層用薄膜の形成方法

【課題】絶縁破壊電圧の高い素子分離層を形成することができる素子分離材料用塗布液等を提供する。

【解決手段】素子分離材料用塗布液は、一般式(I)で表される構造単位からなる骨格を有するポリシラザン等と、酸化物を形成できる金属元素を含む化合物と、溶媒とを備えている。金属元素は、チタン、ジルコニウム、ハフニウム、又は、タンタルであり、ポリシラザン等のSiのモル数に対し、0.5mol%〜19mol%となるように添加されている。 (もっと読む)

(もっと読む)

半導体装置およびその製造方法

【課題】応力の発生が緩和され、かつ、良質な埋め込み構造を有する半導体装置、およびその製造方法を提供する。

【解決手段】第1の領域AR1、第2の領域AR2を有し、さらwに、第1の領域AR1が第1の溝TR1を、第2の領域AR2が第2の溝TR2、を有する基板の溝に絶縁膜を埋設する。このとき、第1の溝TR1、第2の溝TR2のそれぞれを、その溝の幅の相違に応じて、径の異なる第1のナノ粒子CS1、第2のナノ粒子CS2で、埋め込んで絶縁膜を形成する。

(もっと読む)

半導体装置の製造方法

【課題】基板に大きな応力が加わることがなく、ボイドの形成されない埋め込み酸化膜により形成された素子分離領域を有する半導体装置の製造方法を提供する。

【解決手段】素子分離領域を有する半導体装置の製造方法において、半導体基板の表面または、半導体基板の表面に形成された半導体層に、トレンチを形成するトレンチ形成工程と、シロキサン樹脂と有機樹脂からなる脱離材とを混合した塗布材料を前記半導体基板上または、半導体基板に形成された半導体層上に塗布し、前記トレンチを前記塗布材料により埋め込む塗布工程と、前記塗布工程の後、第1の温度で熱処理を行う第1の熱処理工程と、前記第1の熱処理工程の後、前記第1の温度よりも高い第2の温度で熱処理を行う第2の熱処理工程と、を有し、前記トレンチ内に埋め込み酸化膜を形成することにより素子分離領域を形成することを特徴とする半導体装置の製造方法を提供することにより上記課題を解決する。

(もっと読む)

ポリシロキサン縮合反応物を用いたトレンチ埋め込み用絶縁膜の形成方法

【課題】基板に形成された開口幅が狭く高アスペクトなトレンチ内に埋め込むために好適な縮合反応物溶液であって、ポットライフが長く、トレンチ埋め込み用として使用した場合のトレンチ内への埋め込み性が良好で、焼成して酸化シリコンとしたときの硬化収縮率が小さく、クラック耐性及びHF耐性に優れる縮合反応物溶液を用いる絶縁膜の形成方法を提供する。

【解決手段】半導体素子に形成されたトレンチ埋め込み用絶縁膜の形成方法であって、特定構造のシラン化合物に由来するポリシロキサン化合物と、シリカ粒子とを含有する縮合成分から得られる縮合反応物、及び溶媒を含み、該シラン化合物が4官能シラン化合物及び3官能シラン化合物を含有する縮合反応物溶液を、基板上に塗布して塗布基板を得る塗布工程と、該塗布工程で得た塗布基板を加熱する焼成工程とを含むトレンチ埋め込み用絶縁膜の形成方法。

(もっと読む)

トレンチ埋め込み用組成物

【課題】基板表面上のナノメートルレベルの開口幅を有し、アスペクト比が大きいトレンチ(溝)への埋め込み性に優れ、ボイドなどの欠陥の発生が抑制され、電気的絶縁性に優れたアイソレーション構造を製造するのに好適なトレンチ埋め込み用組成物、および該組成物を用いたトレンチ・アイソレーション構造の製造方法の提供。

【解決手段】アルキルトリアルコキシシランを50モル%以上含むアルコキシシラン原料を加水分解、縮合して得られる加水分解縮合物を含有し、該加水分解縮合物の重量平均分子量が1000〜50000であり、該加水分解縮合物の含有量が組成物全量に対して14質量%超30質量%以下であるトレンチ埋め込み用組成物の塗膜14により、基板10表面上に形成されたトレンチ12を埋め込む。

(もっと読む)

半導体装置の製造方法及び製造装置

【課題】高いアスペクト比で狭い幅の溝に、シリコン酸化膜を埋め込むことの可能な、スループットの高い半導体製造方法を提供する。

【解決手段】半導体装置の製造方法において、基板を処理室内へ搬入する工程と、炭素及び水素を含むシリコン化合物ガスを処理室内へ供給して、処理室内を第1の圧力の状態にする工程と、処理室内を前記第1の圧力にした状態において、処理室内へ供給されたシリコン化合物ガスに紫外光を照射して、基板上にシリコン酸化膜を形成する工程と、処理室内を前記第1の圧力よりも低い第2の圧力の状態にする減圧処理工程とを行う。これにより、高アスペクト比で狭い幅の溝内に、緻密なシリコン酸化膜を形成することができる。

(もっと読む)

ポリシラザンを含むコーティング組成物

【課題】埋設性と塗布性とに優れ、すぐれた膜物性を有するシリカ質膜を形成することができるコーティング組成物とそれを用いたシリカ質膜の形成方法の提供。

【解決手段】ペルヒドロポリシラザンと溶媒とを含んでなるコーティング組成物であって、前記ペルヒドロポリシラザンの分子量分布曲線が、分子量800〜2,500の範囲と、分子量3,000〜8,000の範囲とにそれぞれ極大を有し、重量平均分子量Mwと数平均分子量Mnの比Mw/Mnが6〜12である、コーティング組成物。このコーティング組成物ギャップを有する基板上に塗布し、1000℃以下で加熱することにより、ギャップ深部まで埋設されたシリカ質膜を形成させることができる。

(もっと読む)

半導体基板の平坦化方法

【課題】 シャロートレンチ内の絶縁膜表面と半導体基板表面とを平坦にする方法を提供する。

【解決手段】 微細なトレンチアイソレーションによって素子分離を行う半導体装置の製造方法であって、半導体装置基板上に微細トレンチアイソレーション用の溝を形成する第1の工程と、半導体基板全面にCVD法又はSOGを用いて絶縁膜を形成して、前記微細トレンチアイソレーション用の溝を埋め込むと共に、基板全体に前記絶縁膜を堆積させる第2の工程と、重合性基を有する重合性化合物(A)、光重合開始剤(B)、及び溶剤(C)を含む塗布組成物によって前記絶縁膜上に塗布膜を形成する第3の工程と、前記塗布膜を硬化させる第4の工程と表面を化学的機械的研磨(CMP)又はドライ若しくはウェットエッチングにより前記塗布膜及び前記トレンチアイソレーション用の溝外に存在する絶縁膜を同時に除去し、基板表面を平坦化する第5の工程を含む。

(もっと読む)

1 - 20 / 68

[ Back to top ]