Fターム[5F032AA54]の内容

素子分離 (28,488) | 絶縁物を用いる分離 (9,448) | 素子領域側面を絶縁物で分離するもの (8,208) | 溝内埋込み分離 (7,414) | 埋込み材料 (3,229) | その他 (197)

Fターム[5F032AA54]に分類される特許

1 - 20 / 197

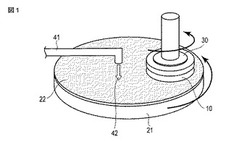

基板処理方法

【課題】 溝パターン内への絶縁層や配線層等の埋め込みを簡易に行うことができ、工程短縮やコスト低減をはかる。

【解決手段】 基板10の表面に形成された溝内に溶媒を埋め込むための基板処理方法であって、基板10の表面上に溶媒42を供給しながら、基板10の表面に弾性材料で形成された溶媒保持材22を接触させた状態で、基板10の表面と溶媒保持材22とが摺動するように、基板10及び前記溶媒保持材22をそれぞれ回転させる。

(もっと読む)

半導体装置

【課題】回路誤動作を防止できる半導体装置を提供する。

【解決手段】低電位基準回路部LVおよび高電位基準回路部HVを構成する絶縁分離された半導体素子の外周に、n型ガードリング42c等を形成する。また、活性層2cにて構成されるn-型層42a等の中にp型ウェル42d等を形成し、このp型ウェル42d内に半導体素子を形成する。また、外部電源61に接続されるラインを電源供給ラインとガードリング端子固定ラインとを分岐し、電源供給ラインの電流が流れないガードリング端子固定ラインに抵抗63を備えることで、バイパスコンデンサ64をディスクリート部品としなくても良い回路構成とする。

(もっと読む)

半導体装置及びその製造方法

【課題】 対象セルのワード線に隣接するワード線の電位の影響に伴う対象セルのビット線への電界を緩和する。

【解決手段】 半導体基板100に形成され、半導体素子101を形成するための活性領域と、半導体基板100内に形成され、活性領域を分離するための素子分離領域(STI102、NF104)と、素子分離領域(STI102、NF104)内に設けられた空洞部105を有する半導体装置。

(もっと読む)

半導体装置、及び半導体装置の製造方法

【課題】ランプアニールによるレイアウトに起因した温度バラつきを低減する。

【解決手段】この半導体装置10は、基板100と、基板100に埋め込まれた素子分離領域200と、基板100のうち、素子分離領域200の無い領域に形成された不純物層(エクステンション領域322、ソース領域324、エクステンション領域342、及びドレイン領域344)と、を備える。この素子分離領域200は、たとえば、波長300nm以上890nm以下においてSiO2よりも光吸収係数が大きい材料から形成されている光吸収層220を含む。

(もっと読む)

半導体装置

【課題】可撓性を有し、曲げ等の物理的変化に対して耐性を有する半導体装置および当該

半導体装置の作製方法を提供することを目的とする。

【解決手段】可撓性を有する基板上に設けられた、半導体膜、半導体膜上にゲート絶縁膜

を介して設けられたゲート電極およびゲート電極を覆って設けられた層間絶縁膜とを有す

る複数のトランジスタと、複数のトランジスタの間に設けられた屈折部分とを有し、屈折

部分は、層間絶縁膜に設けられた開口部に層間絶縁膜より弾性率が低い物質が充填されて

設けられている。また、本発明では、開口部に充填する物質として他にも、層間絶縁膜よ

りガラス転移点が低い物質や塑性を有する物質を設けることができる。

(もっと読む)

半導体装置およびその製造方法

【課題】ウェル給電領域の面積を縮小して、半導体装置の微細化を行う。素子形成領域間のウェル電位のばらつきを抑制する。分離部の幅を細くする。

【解決手段】半導体装置は、半導体基板の表面に形成され、底部がウェル領域内に位置する溝状の分離部を有する。分離部は、ウェル領域と電気的に接続された導体配線と、底部に導体配線を埋め込む絶縁膜とを有する。分離部に囲まれるようにして区画されたウェル領域の一部は素子形成領域を形成し、素子形成領域には半導体素子が配置される。

(もっと読む)

プラズマ処理方法、及び素子分離方法

【課題】 STIプロセスにおけるシリコンのトレンチの内壁面に沿って、酸素の拡散に対するバリア性を有する数nm程度の厚みの薄膜を形成する方法を提供する。

【解決手段】 プラズマ処理装置100では、平面アンテナ31からマイクロ波透過板28を経て処理容器1内に放射されたマイクロ波により、処理容器1内で電磁界が形成され、ArガスおよびN2ガスがそれぞれプラズマ化する。プラズマ中の活性種の作用によりウエハWのトレンチの内壁面が極薄く窒化されることにより、緻密なライナーSiN膜が形成される。

(もっと読む)

半導体装置及びその作製方法

【課題】酸化物半導体を用いるトランジスタにおいて、電気的特性の良好なトランジスタ及びその作製方法を提供することを課題の一とする。

【解決手段】基板上に酸化物半導体膜及び絶縁膜を有し、酸化物半導体膜の端部は絶縁膜と接しており、酸化物半導体膜は、チャネル形成領域と、チャネル形成領域を挟んで形成されたドーパントを含む領域とを含み、酸化物半導体膜上に接して形成されたゲート絶縁膜と、ゲート絶縁膜上に形成され、サイドウォール絶縁膜を有するゲート電極と、サイドウォール絶縁膜、酸化物半導体膜、および絶縁膜に接して形成されたソース電極およびドレイン電極とを有する半導体装置である。

(もっと読む)

半導体装置

【課題】基板を介したクロストークを抑制でき、放熱性が高い半導体装置を提供する。

【解決手段】実施形態に係る半導体装置1は、半導体基板10を備える。前記半導体基板の内部には空洞11が形成されている。また、前記半導体基板の内部には、前記空洞を前記半導体基板の上面に連通させる連通孔12も形成されている。前記半導体装置は、さらに、前記空洞及び前記連通孔の内面上に設けられた絶縁膜13と、前記空洞及び前記連通孔の内部に埋め込まれ、熱伝導率が前記絶縁膜の熱伝導率よりも高い伝熱部材14と、前記半導体基板における前記空洞の直上域に形成された素子21,22と、を備える。

(もっと読む)

半導体装置およびその製造方法

【課題】素子分離用ゲート電極のみのしきい値電圧を高くすることができ、素子分離用ゲート電極の底部にチャネルが形成されない半導体装置を提供する。

【解決手段】半導体基板1に形成された複数の活性領域と、これら活性領域同士を区画する素子分離領域と、活性領域内を複数の素子領域に区画する第1素子分離用トレンチ32Aと、隣接する第1素子分離用トレンチ32A間に設けられ、第1素子分離用トレンチ32Aの深さよりも浅く形成されたゲートトレンチ31Aと、絶縁膜25を介して第1素子分離用トレンチ32A内に形成された素子分離用電極32と、ゲート絶縁膜26Aを介してゲートトレンチ31A内に形成されたゲート電極31と、を具備してなり、素子分離用電極32底部に成膜されている絶縁膜25の膜厚が、ゲート電極31の底部に成膜されているゲート絶縁膜26Aの膜厚よりも厚いことを特徴とする。

(もっと読む)

半導体素子及びその形成方法

【課題】半導体素子及びその形成方法に関し、工程マージンを向上させる。

【解決手段】半導体素子は、半導体基板10に備えられるメインゲート20及び素子分離構造、前記素子分離構造の上部に備えられる分離パターン40及び前記分離パターンの両端に備えられるコンタクトプラグ54を含む。格納電極コンタクトと活性領域との間のフルオーバーラップを提供し、食刻工程でのオーバーレイ問題を解消し、格納電極の食刻線幅を増加させる。

(もっと読む)

半導体装置の製造方法

【課題】塗布法を用いて形成される酸化膜を溝の内部に充填した溝型の素子分離部を有する半導体装置において、溝の内部におけるボイドの発生を抑制して、埋め込み不良を低減することのできる技術を提供する。

【解決手段】0.2μm以下の溝幅を有する溝4Sの内部に埋まるポリシラザン膜の上面がパッド絶縁膜3の上面よりも高く、かつ1.0μm以上の溝幅を有する溝4Lの内部に埋まるポリシラザン膜の上面がパッド絶縁膜3の上面よりも低くなるように、半導体基板1の主面上にポリシラザン膜を形成し、続いて、300℃以上の熱処理を行うことにより、ポリシラザン膜を酸化シリコン(SiO2)からなる第1埋め込み膜8へ転化すると同時に、溝4Sの上部に局所的に生じたボイドを消滅させる。

(もっと読む)

半導体装置およびその製造方法

【課題】デバイス特性に優れた半導体装置およびその製造方法を提供する。

【解決手段】実施の一形態の半導体装置は、第1および第2の領域を有する機能膜と、前記基板の前記第1の領域に設けられ、第1の幅を有する第1の溝と、前記基板の前記第2の領域に設けられ、第1の幅よりも広い第2の幅を有する第2の溝と、前記第1の溝を埋めるように高分子材料を前駆体として形成された第1の絶縁膜と、前記第1の幅を上回る直径を有し、前記第2の溝を埋める微粒子と、前記第2の溝内で前記微粒子間および前記微粒子と前記第2の溝との間隙を埋める前記高分子材料とを前駆体として形成された第2の絶縁膜とを持つ。

(もっと読む)

半導体装置およびその製造方法

【課題】 本発明は、より寄生容量の少ない素子の実現が可能な素子分離構造を有する半導体装置およびその製造方法を提供することにある。

【解決手段】 SOI基板上に形成される半導体装置は、素子分離領域に形成される素子分離溝(空洞)17と、半導体層11と支持基板13の間に介在する埋め込み絶縁層の一部に素子分離溝(空洞)17に接する空洞領域20を有する。

【効果】寄生容量を低減でき、また、素子の耐圧を高めることができる。

(もっと読む)

シリカ系絶縁膜形成用塗布液

【課題】ポットライフが長く、焼成してシリコン酸化物としたときの硬化収縮率が小さく、更にクラック耐性に優れかつ耐電圧のばらつきが小さい絶縁膜を形成できる縮合反応物溶液の提供。

【解決手段】(I)(i)下記一般式(1):R1nSiX14-n (1){式中、nは0〜3の整数であり、R1は水素原子又は炭素数1〜10の炭化水素基であり、X1はハロゲン原子、炭素数1〜6のアルコキシ基又はアセトキシ基である}で表されるシラン化合物に由来するポリシロキサン化合物と、(ii)シリカ粒子と、を少なくとも含有する縮合成分を縮合反応させて得られる縮合反応物、及び(II)溶媒を含み、該一般式(1)で表されるシラン化合物が4官能シラン化合物及び3官能シラン化合物を少なくとも含有し、該シリカ粒子中の炭素量が0.05質量%以上0.65質量%未満である、縮合反応物溶液。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】埋め込みゲート型トランジスタの電流駆動能力の低下を防止可能な半導体装置を提供する。

【解決手段】本発明の半導体装置100は、半導体基板1において素子分離領域5によって複数の活性領域50が区画されると共に、前記半導体基板1内に埋め込まれたワード線8を有する半導体装置100であって、前記ワード線8は、第一の溝部8a内にゲート絶縁膜7aを介して埋め込まれた導電層8bからなり、前記素子分離領域5は、前記第一の溝部8aよりも幅の狭い第二の溝部5aに前記ゲート絶縁膜7bを介して埋め込まれた前記導電層5bからなることを特徴とする。

(もっと読む)

シャロートレンチアイソレーション膜のためのアミノシラン

【課題】記憶及び論理回路を含む半導体基材、例えば、1つ又は複数の集積回路構造をその上に有するシリコンウェハにおいて用いられるシャロートレンチアイソレーションのための高アスペクト比の特徴のギャップを充填するための酸化条件下で二酸化ケイ素含有膜をスピンオン堆積させる方法を提供する。

【解決手段】高アスペクト比の特徴を有する半導体基材を用意する工程、該半導体基材を低分子量のアミノシランを含む液体配合物と接触させる工程、該半導体基材上に該液体配合物を塗布することにより膜を形成する工程、及び該膜を酸化条件下において高温で加熱する工程を含む方法が提供される。この方法のための組成物もまた記載される。

(もっと読む)

半導体装置およびその製造方法

【課題】溝型の素子間分離部により囲まれた活性領域に形成される電界効果トランジスタにおいて、所望する動作特性を得ることのできる技術を提供する。

【解決手段】素子分離部SIOを、溝型素子分離膜6L,6Sと、溝型素子分離膜6L,6Sの上面に形成されたシリコン膜またはシリコン酸化膜からなる厚さ10〜20nmの拡散防止膜20と、拡散防止膜20の上面に形成された厚さ0.5〜2nmのシリコン酸化膜21L,21Sとから構成し、拡散防止膜20の組成をSiOx(0≦x<2)とし、溝型素子分離膜6L,6Sおよびシリコン酸化膜21L,21Sの組成をSiO2とする。

(もっと読む)

半導体装置およびその製造方法

【課題】チャネル領域となるSOI構造を有する半導体線条突出部の形状のばらつきを抑制し、トランジスタ特性のばらつきを減少することができる半導体装置を提供する。

【解決手段】半導体基板1の素子分離用の溝に埋込み絶縁膜が埋め込まれてなる素子分離領域2と、素子分離領域2によって区画されてなり、素子分離用の溝を区画する側壁面と半導体基板の1一面とを有し、かつ側壁面には埋込み絶縁膜に向けて突出した半導体線条突出部1aが素子分離用の溝に沿って設けられてなる活性領域Tと、半導体線条突出部1aを残して活性領域Tを分断するように設けられたゲート電極用のゲート溝3と、ゲート溝3の内面に形成されたゲート絶縁膜4と、ゲート溝3に埋め込まれたゲート電極5と、ゲート電極5のゲート長方向両側の活性領域Tにそれぞれ形成され、半導体線条突出部1aによって連結される不純物拡散領域7と、を具備してなることを特徴とする。

(もっと読む)

歪チャネルを有するMOSトランジスタを製造する方法

【課題】歪チャネルを有するMOS トランジスタを製造するための比較的簡単な方法を提供する。

【解決手段】歪チャネルを有するMOS トランジスタ(M) を製造する方法は、(a) 半導体基板(10)の表面に、ソース領域及びドレイン領域とMOS トランジスタを囲む絶縁領域(22)に部分的に延びる絶縁された犠牲ゲートとを備えたMOS トランジスタを形成するステップと、(b) 犠牲ゲートの上面と略同一の高さの上面を有する絶縁層を形成するステップと、(c) 犠牲ゲートを除去するステップと、(d) 露出した絶縁領域(22)の少なくとも上部分をエッチングしてトレンチを形成するステップと、(e) 半導体基板(10)を歪ませることが可能な材料(24)をトレンチに充填するステップと、(f) 犠牲ゲートの除去によって空いた空間にMOS トランジスタの絶縁ゲート(12)を形成するステップとを有する。

(もっと読む)

1 - 20 / 197

[ Back to top ]