Fターム[5F032AA49]の内容

素子分離 (28,488) | 絶縁物を用いる分離 (9,448) | 素子領域側面を絶縁物で分離するもの (8,208) | 溝内埋込み分離 (7,414) | 埋込み材料 (3,229) | ガラス(PSG、BSG、ASG) (158)

Fターム[5F032AA49]に分類される特許

1 - 20 / 158

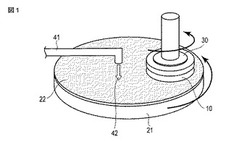

基板処理方法

【課題】 溝パターン内への絶縁層や配線層等の埋め込みを簡易に行うことができ、工程短縮やコスト低減をはかる。

【解決手段】 基板10の表面に形成された溝内に溶媒を埋め込むための基板処理方法であって、基板10の表面上に溶媒42を供給しながら、基板10の表面に弾性材料で形成された溶媒保持材22を接触させた状態で、基板10の表面と溶媒保持材22とが摺動するように、基板10及び前記溶媒保持材22をそれぞれ回転させる。

(もっと読む)

半導体装置及びその製造方法、並びにデータ処理システム

【課題】トランジスタのオン電流を十分に確保することが可能な信頼性の高い半導体装置を提供する。

【解決手段】活性領域6を分断する2つの埋め込みゲート用の溝部8a,8bにゲート絶縁膜9を介して埋め込まれたゲート電極7a,7bと、2つの埋め込みゲート用の溝部8a,8bによって分断された3つの活性領域6a,6b,6cのうち、中央部に位置する活性領域6bを分断するビットコンタクト用の溝部11の両側面に、埋め込みゲート用の溝部8a,8bの底面と同程度の深さで不純物を拡散させることによって形成された第1の不純物拡散層13a,13bと、中央部を挟んだ両側に位置する活性領域6a,6cに、ゲート電極7a,7bの上面と同程度の深さで不純物を拡散させることによって形成された第2の不純物拡散層14a,14bとを備える。

(もっと読む)

半導体装置

【課題】可撓性を有し、曲げ等の物理的変化に対して耐性を有する半導体装置および当該

半導体装置の作製方法を提供することを目的とする。

【解決手段】可撓性を有する基板上に設けられた、半導体膜、半導体膜上にゲート絶縁膜

を介して設けられたゲート電極およびゲート電極を覆って設けられた層間絶縁膜とを有す

る複数のトランジスタと、複数のトランジスタの間に設けられた屈折部分とを有し、屈折

部分は、層間絶縁膜に設けられた開口部に層間絶縁膜より弾性率が低い物質が充填されて

設けられている。また、本発明では、開口部に充填する物質として他にも、層間絶縁膜よ

りガラス転移点が低い物質や塑性を有する物質を設けることができる。

(もっと読む)

半導体装置

【課題】オン抵抗が低く、かつ、容易に素子分離もできる半導体装置を提供する。

【解決手段】第1絶縁膜2の上の第1導電型の第1半導体層3の表面を含む上部に設けられた第2導電型の第1半導体領域7と、第1半導体領域7の上部に設けられた第1導電型の第2半導体領域8と、側面が第1半導体層3と第1半導体領域7と第2半導体領域8に接する第1トレンチ4と、第1トレンチ4の側面に沿って設けられたゲート絶縁膜5と、第1トレンチ4内に埋め込まれたゲート電極6と、第1半導体領域7と第1トレンチ4から離れて第1半導体層3の上部に設けられた第1導電型の第3半導体領域9と、側面が第3半導体領域9に接し第3半導体領域9に対して第1半導体領域7の反対側に配置された第2トレンチ15と、第2トレンチ15の側面に沿って設けられた素子分離絶縁膜10と、第2トレンチ15内に埋め込まれたポリシリコン埋め込み領域11とを有する。

(もっと読む)

化合物半導体装置及び化合物半導体装置の製造方法

【課題】トレンチを用いて素子分離され、且つ、隣接素子の動作による影響が抑制された化合物半導体装置及び化合物半導体装置の製造方法を提供する。

【解決手段】半導体基板10と、キャリア走行層21とキャリア供給層22を有し、半導体基板上に配置された窒化物半導体層20と、上端部がキャリア走行層とキャリア供給層との界面よりも上方に位置する空洞40を内部に有する、窒化物半導体層の周囲を囲んで配置された素子分離絶縁膜30とを備える。

(もっと読む)

半導体装置およびその製造方法

【課題】 本発明は、より寄生容量の少ない素子の実現が可能な素子分離構造を有する半導体装置およびその製造方法を提供することにある。

【解決手段】 SOI基板上に形成される半導体装置は、素子分離領域に形成される素子分離溝(空洞)17と、半導体層11と支持基板13の間に介在する埋め込み絶縁層の一部に素子分離溝(空洞)17に接する空洞領域20を有する。

【効果】寄生容量を低減でき、また、素子の耐圧を高めることができる。

(もっと読む)

半導体装置及びその製造方法

【課題】閾値電圧調整用金属を含む高誘電率絶縁膜を有するゲート絶縁膜を備えたn型MISトランジスタを有する半導体装置において、ゲート幅が狭くなっても、n型MISトランジスタの閾値電圧が高くなることを防止する。

【解決手段】n型MISトランジスタnTrは、半導体基板1における素子分離領域32に囲まれた活性領域1aと、活性領域1a上及び素子分離領域32上に形成され且つ高誘電率絶縁膜12aを有するゲート絶縁膜13aと、ゲート絶縁膜13a上に形成されたゲート電極16aとを備えている。活性領域1aにおける素子分離領域32に接する部分のうち少なくともゲート絶縁膜13aの下側に位置する部分に、n型不純物領域28が形成されている。

(もっと読む)

不揮発性半導体記憶装置および不揮発性半導体記憶装置の製造方法

【課題】隣接する浮遊ゲート電極間の間隔を増大させることなく、隣接する浮遊ゲート電極間の寄生容量を低減する。

【解決手段】トレンチ2内に埋め込まれた第2の埋め込み絶縁膜4の一部が除去されることで、ワード線方向DWに隣接する浮遊ゲート電極6間に空隙AG1が形成され、浮遊ゲート電極6間が完全に埋め込まれないようにして制御ゲート電極8間にカバー絶縁膜10が掛け渡されることで、ビット線方向にDBに隣接する浮遊ゲート電極6間に空隙AG2が形成されている。

(もっと読む)

歪チャネルを有するMOSトランジスタを製造する方法

【課題】歪チャネルを有するMOS トランジスタを製造するための比較的簡単な方法を提供する。

【解決手段】歪チャネルを有するMOS トランジスタ(M) を製造する方法は、(a) 半導体基板(10)の表面に、ソース領域及びドレイン領域とMOS トランジスタを囲む絶縁領域(22)に部分的に延びる絶縁された犠牲ゲートとを備えたMOS トランジスタを形成するステップと、(b) 犠牲ゲートの上面と略同一の高さの上面を有する絶縁層を形成するステップと、(c) 犠牲ゲートを除去するステップと、(d) 露出した絶縁領域(22)の少なくとも上部分をエッチングしてトレンチを形成するステップと、(e) 半導体基板(10)を歪ませることが可能な材料(24)をトレンチに充填するステップと、(f) 犠牲ゲートの除去によって空いた空間にMOS トランジスタの絶縁ゲート(12)を形成するステップとを有する。

(もっと読む)

半導体装置の製造方法

【課題】加工膜と非加工膜をRIE法で選択的に加工するときに、非加工膜の加工量を低減させる半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法は、下地層1,7,8の上に非加工膜14を形成する工程と、非加工膜14および下地層1,7,8に溝4を形成する工程と、溝内を埋め込むように加工膜5を形成する工程と、非加工膜14を露出させるように加工膜5を平坦化する工程とを備える。更に、加工膜5および非加工膜14の上に保護膜16を形成する工程と、RIE法を用いて、保護膜16をエッチングすると共に、加工膜5を選択的にエッチングして溝内の加工膜5を落とし込む工程とを備える。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】製造工程を簡略化しつつ、絶縁分離トレンチの破壊耐圧を向上させることができる半導体装置の製造方法および半導体装置を提供する。

【解決手段】半導体層13の素子形成領域に半導体素子が形成された半導体基板10を用意する工程と、半導体層13に、素子形成領域を取り囲み、絶縁膜12側と反対側の表面から当該絶縁膜12に達するトレンチ20を形成する工程と、トレンチ20の壁面に側壁絶縁膜21を形成する工程と、トレンチ20に、不純物を含む埋込絶縁膜22をCVD法により、当該埋込絶縁膜22にて囲まれる空洞22aを形成しつつ配置する工程と、半導体基板10を熱処理する工程と、を含む工程を行う。

(もっと読む)

半導体装置及びその製造方法

【課題】工程マークやアライメントマーク等を形成するトレンチ内のSOG膜にクラックが発生した場合に、そのクラックが素子形成領域に到達するのを防止する。

【解決手段】半導体基板10の素子形成領域10Tの外側において、工程マーク30Cは、トレンチ31のパターンで形成されている。素子形成領域10Tと、その外側のトレンチ31は層間絶縁膜21に覆われており、層間絶縁膜21は、トレンチ31内を埋めるSOG膜22に覆われている。さらに、半導体基板10の表面上には、トレンチ31及びトレンチ31上のSOG膜22を囲む環状ポリシリコン膜18が形成されている。

(もっと読む)

トレンチにより制限された分離拡散領域を備えた相補型アナログバイポーラトランジスタ

【課題】表面上に素子をより高密度に実装する。

【解決手段】第1のトレンチと第2のトレンチとの間の位置において、エピタキシャル層の表面から基板へと下方に延在するドーパントのウェルは、エピタキシャル層の背景ドーピング濃度とは異なるドーピング濃度を有し、エピタキシャル層の残りの部分と第1および第2の接合を形成する。第1の接合は、第1のトレンチの底部から基板に延在し、第2の接合は、第2のトレンチの底部から前記基板に延在する。ウェルおよび第1および第2のトレンチは分離構造を構成し、分離構造は、分離構造の一方側のエピタキシャル層に形成された第1の素子と分離構造の他方側のエピタキシャル層に形成された第2の素子とを電気的に分離する。分離構造による電気的分離は第1および第2のトレンチとPN接合とによってもたらされ、ウェルは第1の導電型の材料でドープされ、基板およびエピタキシャル層は、第1の導電型とは反対の第2の導電型の材料でドープされ、第1および第2の接合はPN接合である。

(もっと読む)

半導体装置およびその製造方法

【課題】簡易なプロセスで、高い埋め込み性を確保する必要のない半導体装置およびその製造方法を提供する。

【解決手段】本発明の半導体装置の製造方法では、まず支持基板SSと、埋め込み絶縁膜BOXと半導体層SLとがこの順で積層された構成を有する半導体基板SUBが準備される。半導体層SLの主表面に、導電部分を有する素子が完成される。上記素子を平面視において取り囲む溝DTRが、半導体層SLの主表面から埋め込み絶縁膜BOXに達するように形成される。上記素子上を覆うように、かつ溝DTR内に中空を形成するように素子上および溝DTR内に第1の絶縁膜(層間絶縁膜II)が形成される。上記第1の絶縁膜に素子の導電部分に達する孔であるコンタクトホールCHが形成される。

(もっと読む)

ポリシラザンを含むコーティング組成物

【課題】埋設性と塗布性とに優れ、すぐれた膜物性を有するシリカ質膜を形成することができるコーティング組成物とそれを用いたシリカ質膜の形成方法の提供。

【解決手段】ペルヒドロポリシラザンと溶媒とを含んでなるコーティング組成物であって、前記ペルヒドロポリシラザンの分子量分布曲線が、分子量800〜2,500の範囲と、分子量3,000〜8,000の範囲とにそれぞれ極大を有し、重量平均分子量Mwと数平均分子量Mnの比Mw/Mnが6〜12である、コーティング組成物。このコーティング組成物ギャップを有する基板上に塗布し、1000℃以下で加熱することにより、ギャップ深部まで埋設されたシリカ質膜を形成させることができる。

(もっと読む)

半導体装置およびその製造方法

【課題】PMOS領域における素子分離膜のライナー窒化膜の除去を行う従来技術による問題を解決した半導体装置およびその製造方法を提供すること。

【解決手段】半導体装置の製造方法は、基板20をエッチングして複数のトレンチを形成するステップと、複数のトレンチ内に第1絶縁膜24Aを埋め込んで第1素子分離膜を形成するステップと、一部のトレンチ(CELL又はPERI NMOS領域のトレンチ)内に埋め込まれた第1絶縁膜24Aをリセスするステップと、リセスされたトレンチの全面にライナー膜26A、27Aを形成するステップと、ライナー膜26A、27Aが形成されたトレンチ内に第2絶縁膜28を埋め込んで第2素子分離膜を形成するステップとを含む。

(もっと読む)

異なる誘電材料を用いたインター装置STI領域とイントラ装置STI領域の形成

【課題】異なる誘電材料を用いたインター装置STI領域とイントラ装置STI領域の形成を提供する。

【解決手段】集積回路構造は、第1装置領域に第1部分、第2装置領域に第2部分を有する基板と、第1装置領域中で、且つ、基板上に位置する2つの絶縁領域と、からなる。2つの絶縁領域は、第1k値を有する第1誘電材料を含む。半導体ストリップは、2つの絶縁領域間に位置し、且つ、2つの絶縁領域に隣接し、2つの絶縁領域の頂面上に、半導体フィンを形成する半導体ストリップの上部分を有する。追加の絶縁領域が、第2装置領域中で、且つ、基板上に位置する。追加の絶縁領域は、第1k値より大きい第2k値を有する第2誘電材料を含む。

(もっと読む)

半導体基板の平坦化方法

【課題】 シャロートレンチ内の絶縁膜表面と半導体基板表面とを平坦にする方法を提供する。

【解決手段】 微細なトレンチアイソレーションによって素子分離を行う半導体装置の製造方法であって、半導体装置基板上に微細トレンチアイソレーション用の溝を形成する第1の工程と、半導体基板全面にCVD法又はSOGを用いて絶縁膜を形成して、前記微細トレンチアイソレーション用の溝を埋め込むと共に、基板全体に前記絶縁膜を堆積させる第2の工程と、重合性基を有する重合性化合物(A)、光重合開始剤(B)、及び溶剤(C)を含む塗布組成物によって前記絶縁膜上に塗布膜を形成する第3の工程と、前記塗布膜を硬化させる第4の工程と表面を化学的機械的研磨(CMP)又はドライ若しくはウェットエッチングにより前記塗布膜及び前記トレンチアイソレーション用の溝外に存在する絶縁膜を同時に除去し、基板表面を平坦化する第5の工程を含む。

(もっと読む)

平坦化後の高密度化

パターン付き基板上に高密度の間隙充填酸化ケイ素を形成するプロセスについて記載する。このようなプロセスは、特に狭いトレンチ内で間隙充填酸化ケイ素の密度を増大させる。密度は、広いトレンチおよび凹んだ開放領域内でも増大させることができる。処理の後では、狭いトレンチと広いトレンチ/開放領域内の間隙充填酸化ケイ素の密度は互いに接近し、エッチング速度の一致度が高まる。この効果は、パターンローディング効果の低減として説明することもできる。このプロセスは、酸化ケイ素を形成し、次いで平坦化するステップを伴う。平坦化により、狭いトレンチに近接して配置された新しい誘電体インターフェースが露出する。新しく露出されたインターフェースは、平坦化された表面をアニールし、かつ/またはプラズマに露出させることによって、高密度化処理を容易にする。  (もっと読む)

(もっと読む)

半導体デバイスの絶縁

【課題】半導体デバイスの絶縁構造の構造、および、形成方法を提供する。

【解決手段】当該絶縁構造は、底部が最上部よりも広くなっており、半導体デバイスの大きさを調整できる。第1のエッチングプロセスが、第1のトレンチ部分226を形成するために用いられ、第2のエッチングプロセスまたは酸化工程が、第1のトレンチ部分226の下に第2のトレンチ部分228を形成するために用いられる。第2のトレンチ部分は、第1のトレンチ部分よりも広い。一形態では、下地膜222が、第1のトレンチ部分の間、第1のトレンチ部分の側壁上に形成されてもよい(この第1のトレンチ部分は、第2のエッチングプロセスの間、第1のトレンチ部分の側壁を保護する)。あるいは、他の形態では、下地膜222が、第1のトレンチ部分の側壁上に堆積されていてもよい。

(もっと読む)

1 - 20 / 158

[ Back to top ]