Fターム[5F032AA47]の内容

素子分離 (28,488) | 絶縁物を用いる分離 (9,448) | 素子領域側面を絶縁物で分離するもの (8,208) | 溝内埋込み分離 (7,414) | 埋込み材料 (3,229) | 多結晶シリコン、非晶質シリコン (291)

Fターム[5F032AA47]の下位に属するFターム

不純物がドープされているもの (50)

Fターム[5F032AA47]に分類される特許

1 - 20 / 241

SOIウエハおよびSOIウエハの製造方法

【課題】除電構造と素子分離構造とを有するSOIウエハを、従来より少ない工程で製造することができるSOIウエハの製造方法の提供。

【解決手段】SOIウエハの周縁部分に活性層用半導体層および絶縁酸化膜を貫通する除電用トレンチをエッチングで形成すると同時に、当該周縁部分より内側の内側部分に上記活性層用半導体層を貫通し上記絶縁酸化膜に到達する素子分離用トレンチをエッチングで形成するトレンチ形成ステップを備え、上記トレンチ形成ステップは、上記周縁部分におけるエッチングレートが、上記内側部分におけるエッチングレートよりも高いことを特徴とする。

(もっと読む)

半導体装置の製造方法

【課題】能動素子または受動素子が一つの半導体基板に複数個形成されてなる半導体装置およびその製造方法であって、両面電極素子についても絶縁分離と集積化が可能であり、安価に製造することのできる半導体装置およびその製造方法を提供する。

【解決手段】半導体基板20が、当該半導体基板20を貫通する絶縁分離トレンチTに取り囲まれて、複数のフィールド領域F1〜F8に分割されてなり、複数個の能動素子31〜33,41〜43または受動素子51,52が、それぞれ異なるフィールド領域F1〜F8に分散して配置されてなり、二個以上の素子が、当該素子に通電するための一組の電極dr1,dr2が半導体基板20の両側の表面S1,S2に分散して配置されてなる、両面電極素子41〜43,51,52である半導体装置100とする。

(もっと読む)

半導体装置の製造方法

【課題】素子分離用の大きなエアギャップを容易に形成することが可能な半導体装置の製造方法を提供する。

【解決手段】一の実施形態による半導体装置の製造方法では、基板内に素子分離溝を形成し、前記素子分離溝の側壁面にアモルファス層を形成する。さらに、前記方法では、前記素子分離溝内に前記アモルファス層を介して犠牲膜を形成し、前記犠牲膜上にエアギャップ膜を形成する。さらに、前記方法では、前記エアギャップ膜の形成後に前記犠牲膜を除去することで、前記エアギャップ膜の下部の前記素子分離溝内にエアギャップを形成する。

(もっと読む)

半導体装置およびその製造方法

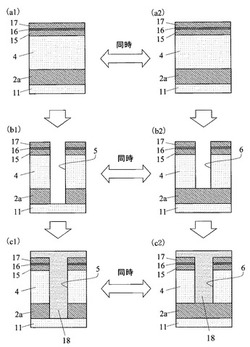

【課題】トレンチ構造の表面に不要な溝が形成されず、また、素子の面積効率を良好なものとすることができる半導体装置の製造方法の提供。

【解決手段】トレンチ内にポリシリコンが充填され、当該ポリシリコンの上部がシリコン酸化膜により覆われたトレンチ構造を有する半導体装置の製造方法であって、シリコン活性層の上面に第1のシリコン酸化膜が積層されてなる基板に異方性エッチングを行うことにより、上記第1のシリコン酸化膜の上面から上記シリコン活性層内に伸びるトレンチを形成するトレンチ形成工程と、上記トレンチの側壁全体を一体的に覆う第2のシリコン酸化膜を形成する側壁酸化膜形成工程と、上記第2のシリコン酸化膜の形成後に、上記トレンチ内にポリシリコンを充填する充填工程と、上記トレンチ内に充填したポリシリコンの上部露出面を酸化させてキャップを形成するキャップ形成工程と、を備える。

(もっと読む)

基板処理装置及び半導体装置の製造方法

【課題】膜応力の小さい低誘電率の絶縁膜を形成できる基板処理装置を提供する。

【解決手段】処理室内へ無機シリコンガスと酸素含有ガスを供給している状態で、励起エネルギーを処理室内へ供給して、基板表面にシリコン酸化膜を形成するシリコン酸化膜形成工程と、処理室内へ有機シリコンガスを供給している状態で、励起エネルギーを処理室内へ供給して、基板表面にシリコン膜を形成するシリコン膜形成工程と、を行うことにより、処理室内の基板表面に絶縁膜を形成するよう、基板処理装置を構成する。

(もっと読む)

半導体装置、及び半導体装置の製造方法

【課題】ランプアニールによるレイアウトに起因した温度バラつきを低減する。

【解決手段】この半導体装置10は、基板100と、基板100に埋め込まれた素子分離領域200と、基板100のうち、素子分離領域200の無い領域に形成された不純物層(エクステンション領域322、ソース領域324、エクステンション領域342、及びドレイン領域344)と、を備える。この素子分離領域200は、たとえば、波長300nm以上890nm以下においてSiO2よりも光吸収係数が大きい材料から形成されている光吸収層220を含む。

(もっと読む)

半導体装置

【課題】 素子特性の劣化を抑制する。

【解決手段】 実施形態による半導体装置は、トランジスタ領域を有する半導体装置であって、トランジスタ領域は、基板上に形成された半導体領域と、半導体領域に隣接する素子分離領域と、ラテラルエピタキシャル層を備え、半導体領域上及び半導体領域と素子分離領域との間で横方向に成長するエピタキシャル層と、を具備する。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】隣接セル間干渉を抑制した不揮発性半導体記憶装置及びその製造方法を提供する。

【解決手段】実施形態によれば、第1メモリストリングと、ソースコンタクトと、第2メモリストリングと、シールド導電層と、を備えた不揮発性半導体記憶装置を提供する。第1メモリストリングは、第1軸に沿って並ぶ第1メモリセル及び第2メモリセルを含む。ソースコンタクトは、第1メモリストリングのソース側の端に設けられる。第2メモリストリングは、第1軸に対して直交する第2軸に沿って第1メモリセルと並ぶ第3メモリセルを含み、第1軸に沿って延在する。シールド導電層は、第1メモリストリングと第2メモリストリングとの間において第1軸に沿って延在し、ソースコンタクトと電気的に接続される。

(もっと読む)

半導体装置及びその製造方法並びに抵抗器及び半導体素子

【課題】pn接合におけるリーク電流を抑制する。

【解決手段】N−型半導体層10と、シリサイド層20sがその表面に形成されたP−型半導体層20とが、絶縁体9上に形成される。半導体層10にはPMOSトランジスタを、半導体層20にはNMOSトランジスタを、それぞれ形成することができる。半導体層10,20がpn接合J50aを形成する場合、これはシリサイド層20sの端部から近く、結晶欠陥が小さい位置に存在するので、ここにおけるリーク電流は非常に小さい。半導体層10,20が形成するpn接合は、シリサイド層20sの端部から2μm以下の距離にあることが望ましい。

(もっと読む)

半導体装置

【課題】正確にメインセルに流れる電流を検出することができると共に、高い電圧が用いられる場合でもその影響を受け難い半導体装置を提供する。

【解決手段】メインセルとセンスセルとをトレンチ分離構造1dによって絶縁分離する。これにより、メインセルのコレクタに対して100V以上の高電圧が印加されても、それに起因するノイズが電流検出用の出力端子に誘起されないようにできる。また、センスセルのエミッタ電位がセンス抵抗Rsに流れる電流によって上昇しても、メインセルのエミッタと電気的に完全に分離されているため、寄生トランジスタが動作することもない。勿論、抵抗層14から発生させられたノイズが電流検出用の出力端子に誘起されることも抑制できる。したがって、正確にメインセルに流れる電流を検出することができると共に、高い電圧が用いられる場合でもその影響を受け難い半導体装置とすることが可能となる。

(もっと読む)

SOIウェハの製造方法

【課題】SOIウェハの支持基板ウェハの帯電を除去することのできるSOIウェハの製造方法を提供する。

【解決手段】活性層基板10と支持基板20との貼り合わせ面に酸化膜22を形成する酸化膜形成工程と、活性層基板10と支持基板20とを貼り合わせる貼り合わせ工程と、支持基板20に向けて活性層基板10に酸化膜22に達するまでのトレンチを形成するトレンチ形成工程と、トレンチから酸化膜22に向けて予め定められたイオンを注入するイオン注入工程と、トレンチ内部をポリシリコン3で充填する充填工程とを備える。

(もっと読む)

トレンチの埋め込み方法および成膜装置

【課題】 トレンチの微細化がさらに進展しても、トレンチの内部に、膨張可能な膜及び酸化障壁となる膜を形成することが可能なトレンチの埋め込み方法を提供すること。

【解決手段】 トレンチ内部に酸化障壁膜の形成工程(ステップ3)、酸化障壁膜上に膨張可能な膜の形成工程(ステップ4)、焼成することで収縮する埋め込み材でトレンチを埋め込む工程(ステップ5)、埋め込み材の焼成工程(ステップ6)と、を含み、ステップ3の工程が、アミノシラン系ガスを供給して、トレンチの内部に第1のシード層を形成する工程(ステップ31)、第1のシード層上に窒化シリコン膜を形成する工程(ステップ32)と、を含み、ステップ4の工程が、アミノシラン系ガスを供給して、窒化シリコン膜上に第2のシード層を形成する工程(ステップ41)と、第2のシード層上にシリコン膜を形成する工程(ステップ42)と、を含む。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】埋め込みゲート型トランジスタの電流駆動能力の低下を防止可能な半導体装置を提供する。

【解決手段】本発明の半導体装置100は、半導体基板1において素子分離領域5によって複数の活性領域50が区画されると共に、前記半導体基板1内に埋め込まれたワード線8を有する半導体装置100であって、前記ワード線8は、第一の溝部8a内にゲート絶縁膜7aを介して埋め込まれた導電層8bからなり、前記素子分離領域5は、前記第一の溝部8aよりも幅の狭い第二の溝部5aに前記ゲート絶縁膜7bを介して埋め込まれた前記導電層5bからなることを特徴とする。

(もっと読む)

半導体装置およびその製造方法

【課題】少工数で製造可能で且つ高い耐圧性能を有する半導体装置を提供する。

【解決手段】素子形成領域と、素子形成領域を外部領域から絶縁分離するべく素子形成領域表面から基板表面までの深さで素子形成領域側面を包囲するよう形成された第1絶縁トレンチ領域10aとを備える半導体装置であって、素子形成領域は、埋め込みコレクタ領域と、コレクタ耐圧領域4と、ベース領域5と、表面コレクタ領域8bと、エミッタ領域8aと、ベース領域と表面コレクタ領域との間におけるキャリアの直線的な移動を遮るよう、当該領域間において素子形成領域表面から基板表面にまでの深さで形成される第2絶縁トレンチ領域10bとを備え、半導体装置を平面視した際、第2絶縁トレンチと第1絶縁トレンチ領域との間には、キャリアが第2絶縁トレンチを迂回してベース領域と表面コレクタ領域との間を移動するためのキャリア迂回領域12a,12bが形成される。

(もっと読む)

半導体装置

【課題】従来に比してオン電圧性能に優れた横型IGBT、および順方向電圧特性に優れた横型FWDを同一基板上に構成可能とする半導体装置を提供する。

【解決手段】半導体基板上において、横型IGBTと、横型FWDとが、絶縁体であるトレンチ絶縁仕切り部を挟むように横方向に隣接配置されて成る半導体装置であって、横型IGBTは、平面視した場合に、エミッタ領域と当該横型IGBTのドリフト領域との境界面の幅がコレクタ領域と当該横型IGBTのドリフト領域との境界面の幅より狭くなるよう形成されており、横型FWDは、平面視した場合に、カソード領域と当該横型FWDのドリフト領域との境界面の幅がアノード領域と当該横型FWDのドリフト領域との境界面の幅より狭くなるよう形成されていることを特徴とする、半導体装置。

(もっと読む)

半導体装置の製造方法

【課題】MOSトランジスタの形成工程を利用して、トレンチアイソレーションを形成できるようにした半導体装置の製造方法を提供する。

【解決手段】シリコン基板1にDTI層20とMOSトランジスタとを有する半導体装置の製造方法であって、シリコン基板1に深いトレンチを形成し、トレンチが形成されたシリコン基板1に熱酸化を施して、PMOSトランジスタ50のゲート酸化膜13を形成すると同時に、トレンチの内側面にSiO2膜14を形成する。次に、トレンチを埋め込むようにシリコン基板1上にポリシリコン膜15を堆積し、このポリシリコン膜15をパターニングする。これにより、PMOSトランジスタ50のゲート電極17を形成すると同時に、トレンチ内にSiO2膜14とポリシリコン膜18とを含むDTI層20を形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】Cdsubの低減化を通じて、出力容量Cossの低減化に寄与する半導体装置及びその製造方法を提供する。

【解決手段】半導体基板1とこの半導体基板1上に埋め込み絶縁層を介して形成された第1導電型の半導体層とを有するSOI基板と、第1導電型の半導体層からなる活性領域3内に形成された素子領域と、素子領域の少なくとも1つに接続される外部取り出し用の電極(ドレインパッド9p)とを有する半導体装置において、外部取り出し用の電極9p下に位置する活性領域が、埋め込み絶縁層2に到達するように形成された絶縁分離領域11で囲まれており、絶縁分離領域11で分離された活性領域3と、外部取り出し用の電極9pとの間に絶縁体13が配されたことを特徴とする。

(もっと読む)

半導体装置およびその製造方法

【課題】工程が簡単で、よりラッチアップに強いCMOS構造を得る。

【解決手段】1×1018cm−3から1×1019cm−3の高不純物濃度の半導体基板2を用い、CMOS構造のP型ウェル4とN型ウェル5の境界に設けられた溝分離部13の先端部分がその高不純物濃度領域に達する(エピタキシャル層3を貫通して半導体基板2の領域に至る)ように深く形成することにより、従来のように溝分離部13よりも更に深い領域(溝分離部13の下側)を電子が通過することなく、従来のようにウェル領域内にN+埋め込み層やP+埋め込み層を基板深く埋め込む必要もなく、簡便な方法で、よりラッチアップに強いCMOS構造を得ることができ、コスト性能の両方に優れた半導体装置1を得ることができる。

(もっと読む)

半導体装置およびその製造方法

【課題】溝型の素子間分離部により囲まれた活性領域に形成される電界効果トランジスタにおいて、所望する動作特性を得ることのできる技術を提供する。

【解決手段】素子分離部SIOを、溝型素子分離膜6L,6Sと、溝型素子分離膜6L,6Sの上面に形成されたシリコン膜またはシリコン酸化膜からなる厚さ10〜20nmの拡散防止膜20と、拡散防止膜20の上面に形成された厚さ0.5〜2nmのシリコン酸化膜21L,21Sとから構成し、拡散防止膜20の組成をSiOx(0≦x<2)とし、溝型素子分離膜6L,6Sおよびシリコン酸化膜21L,21Sの組成をSiO2とする。

(もっと読む)

半導体装置の製造方法

【課題】低コストで高い信頼性を有する逆阻止型の半導体装置およびその製造方法を提供する。

【解決手段】半導体チップを構成する表面構造133、裏面構造134を形成した薄い半導体ウェハ101を両面粘着テープ137で支持基板141に貼り付け、薄い半導体ウェハ101にスクライブラインとなるトレンチを湿式異方性エッチングで結晶面を出して形成し、結晶面が露出したトレンチの側面に逆耐圧を維持する分離層145を裏面拡散層であるpコレクタ領域110と接して表面側に延在するようにイオン注入と低温アニールまたはレーザーアニールで形成する。レーザーダイシングを行って、分離層145の下でコレクタ電極111を過不足なくきれいに切断した後、両面粘着テープ137をコレクタ電極111から剥がして半導体チップとすることで逆阻止型の半導体装置を形成する。

(もっと読む)

1 - 20 / 241

[ Back to top ]