Fターム[5F032DA23]の内容

Fターム[5F032DA23]に分類される特許

1 - 20 / 915

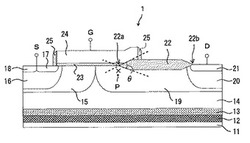

半導体装置およびその製造方法

半導体装置およびその製造方法

【課題】LOCOS酸化膜端部の直下の電界集中が容易に緩和され、LOCOS酸化膜直下の半導体導電層の良好な耐圧および抵抗を実現することのできる半導体装置を提供する。

【解決手段】半導体装置(1)は、LOCOS酸化膜(22)の半導体基板の表面に対してラテラル方向に終端しているエッジ(22a、22b)の少なくとも一部(22a、22b)が、上面と下面とに15度以上30度以下の角度(θ)で挟まれて終端するプロファイルを有している。

(もっと読む)

SOIウエハおよびSOIウエハの製造方法

【課題】除電構造と素子分離構造とを有するSOIウエハを、従来より少ない工程で製造することができるSOIウエハの製造方法の提供。

【解決手段】SOIウエハの周縁部分に活性層用半導体層および絶縁酸化膜を貫通する除電用トレンチをエッチングで形成すると同時に、当該周縁部分より内側の内側部分に上記活性層用半導体層を貫通し上記絶縁酸化膜に到達する素子分離用トレンチをエッチングで形成するトレンチ形成ステップを備え、上記トレンチ形成ステップは、上記周縁部分におけるエッチングレートが、上記内側部分におけるエッチングレートよりも高いことを特徴とする。

(もっと読む)

半導体装置の製造方法

【課題】微細化に対応した半導体装置を提供する。

【解決手段】半導体基板の第1の領域内に第1の方向に沿って交互に配置されるように第1及び第2の素子分離領域を形成する。この際、第1及び第2の素子分離領域のうち少なくとも一方の素子分離領域の側面は半導体基板の主面に対して垂直とならないように第1及び第2の素子分離領域を形成する。この後、第1及び第2の素子分離領域の上部を除去して、第1の素子分離領域と第2の素子分離領域の間の半導体基板をフィンとして形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】SOI基板上に形成されたMOSFETを有する半導体装置の信頼性を向上させる。

【解決手段】SOI基板SB上に形成されたマットMT内に複数のMOSFETを有する半導体装置において、BOX膜を貫き支持基板に達するコンタクトプラグCT2を形成することで、マットMTの周囲を、SOI基板SBの主面に沿う第1方向または第1方向に直交する第2方向に延在する複数のコンタクトプラグCT2により囲む。これにより、コンタクトプラグCT2をガードリングとして用い、マットMTの外部に流れる高周波信号に起因してマットMT内にノイズが発生することを防ぐ。

(もっと読む)

半導体装置およびその分離膜の製造方法

【課題】STI部からHigh−k膜部への酸化剤の侵入を効果的に抑制するための構造を有する半導体装置を提供する。

【解決手段】分離膜で素子分離されたシリコン基板上にゲート電極を有する半導体装置であって、該シリコン基板の分離膜が、酸化物層(酸化膜)の上に酸化剤を透過させにくい材料層を積層した構造を有することを特徴とする半導体装置。

(もっと読む)

半導体装置及びその製造方法

【課題】エッチングによるマスク窒化膜除去時に、STI構造を構成しているライナー膜に劣化が発生することを防止する。

【解決手段】半導体基板に形成したトレンチ内に素子分離構造を形成する工程を含み、前記素子分離構造を形成する工程は、前記トレンチ内の前記半導体基板上にパッド酸化膜を形成する工程と、前記パッド酸化膜上にALD法によりライナー膜を形成する工程と、前記ライナー膜上にSOD膜を形成する工程と、を含む半導体装置の製造方法。ライナー膜は酸化ハフニウム膜が好ましい。

(もっと読む)

半導体ウェハ、半導体装置及びその製造方法

【課題】アライメントマーク終端部への応力集中により基板にクラックが発生することを軽減する。

【解決手段】基板の第1の主面に、第1の主面に対向して見た場合に、環状の第1の溝及び終端部を有さない形状の第2の溝を形成する。第1及び第2の溝を埋め込むように絶縁膜を形成した後、基板の第1の主面にフォトレジスト膜を形成する。絶縁膜で埋め込まれた第2の溝の基板上での位置を基準として位置合わせした第1のパターンを、フォトレジスト膜に転写する。絶縁膜で埋め込まれた環状の第1の溝の内側に位置する基板に、基板を厚さ方向に貫通する貫通電極を形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】隣接するSOI領域とバルクシリコン領域とが短絡することを防止する。

【解決手段】一つの活性領域内にSOI領域およびバルクシリコン領域が隣接する半導体装置において、それぞれの領域の境界にダミーゲート電極8を形成することにより、BOX膜4上のSOI膜5の端部のひさし状の部分の下部の窪みにポリシリコン膜などの残渣が残ることを防ぐ。また、前記ダミーゲート電極8を形成することにより、それぞれの領域に形成されたシリサイド層14同士が接触することを防ぐ。

(もっと読む)

半導体装置の製造方法

【課題】半導体基板をエッチングする際、ハードマスクの肩落ちによるエッチング深さの基板面内での粗密差を低減する。

【解決手段】半導体基板1上に、絶縁層(10,11)とアッシング除去可能な材料層を形成する工程と、材料層をパターニングする工程と、パターニングされた材料層をマスクに、絶縁層を貫通し、少なくとも半導体基板の一部をエッチングする第1のエッチング工程と、材料層がなくなる前にエッチングを一旦停止し、残存する材料層(12)をアッシング除去する工程と、絶縁層をマスクに半導体基板を所定の深さにエッチングする第2のエッチング工程とを含む。

(もっと読む)

半導体装置の製造方法

【課題】素子分離用の大きなエアギャップを容易に形成することが可能な半導体装置の製造方法を提供する。

【解決手段】一の実施形態による半導体装置の製造方法では、基板内に素子分離溝を形成し、前記素子分離溝の側壁面にアモルファス層を形成する。さらに、前記方法では、前記素子分離溝内に前記アモルファス層を介して犠牲膜を形成し、前記犠牲膜上にエアギャップ膜を形成する。さらに、前記方法では、前記エアギャップ膜の形成後に前記犠牲膜を除去することで、前記エアギャップ膜の下部の前記素子分離溝内にエアギャップを形成する。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】高耐圧MOSトランジスタと低電圧MOSトランジスタとの両方について良好な特性を得るための技術を提供する。

【解決手段】高耐圧領域に高耐圧トランジスタが形成され、低耐圧領域に低耐圧トランジスタが形成される半導体装置の製造方法が提供される。当該半導体装置の製造方法は、シリコン基板1の表面に、熱酸化膜2とシリコン窒化膜3を形成する工程と、高耐圧領域、低耐圧領域のそれぞれにおいて熱酸化膜2とシリコン窒化膜3に開口を形成する工程と、該開口を通じてシリコン基板1をエッチングしてトレンチ11、12を形成する工程と、トレンチ11、12に埋め込み酸化膜14を埋め込む工程と、熱酸化膜2とシリコン窒化膜3を除去する工程と、厚いゲート酸化膜15と薄いゲート酸化膜16とを形成する工程とを備えている。トレンチ12のテーパー部分8aの深さが、トレンチ11のテーパー部分5aの深さよりも浅い。

(もっと読む)

高電子移動度トランジスタ及びその製造方法

【課題】高電子移動度トランジスタ及びその製造方法を提供する。

【解決手段】高電子移動度トランジスタ(HEMT)及びその製造方法に係り、該高電子移動度トランジスタは、基板と、基板から離隔された位置に備わった高電子移動度トランジスタ積層物と、基板と高電子移動度トランジスタ積層物との間に位置した疑似絶縁層と、を含み、該疑似絶縁層は、異なる相の少なくとも2つの物質を含む。前記異なる相の少なくとも2つの物質は、固体物質と非固体物質とを含む。前記固体物質は、半導体物質であり、前記非固体物質は、空気である。

(もっと読む)

基板処理方法

【課題】 溝パターン内への絶縁層や配線層等の埋め込みを簡易に行うことができ、工程短縮やコスト低減をはかる。

【解決手段】 基板10の表面に形成された溝内に溶媒を埋め込むための基板処理方法であって、基板10の表面上に溶媒42を供給しながら、基板10の表面に弾性材料で形成された溶媒保持材22を接触させた状態で、基板10の表面と溶媒保持材22とが摺動するように、基板10及び前記溶媒保持材22をそれぞれ回転させる。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】電流コラプスを抑制しながらノーマリオフ動作を実現することができる化合物半導体装置及びその製造方法を提供する。

【解決手段】化合物半導体装置の一態様には、基板1と、基板1上方に形成された化合物半導体積層構造7と、化合物半導体積層構造上方に形成されたゲート電極11g、ソース電極11s及びドレイン電極11dと、が設けられている。化合物半導体積層構造7には、電子走行層3と、電子走行層3上方に形成された電子供給層5を含む窒化物半導体層と、が設けられている。窒化物半導体層の表面のIn組成は、平面視でゲート電極11gとソース電極11sとの間に位置する領域及びゲート電極11gとドレイン電極11dとの間に位置する領域において、ゲート電極11gの下方よりも低くなっている。

(もっと読む)

半導体装置及びその製造方法

【課題】動作速度を向上し消費電力を低減しうる半導体装置及びその製造方法を提供する。

【解決手段】半導体基板に第1の領域を画定する第1の素子分離絶縁膜と、半導体基板の第1の領域に形成された第1導電型の第1の導電層と、半導体基板上に形成され、第1の領域の一部である第2の領域に第1の導電層に接続して形成された第1導電型の第2の導電層と、第1の領域の他の一部である第3の領域に第1の導電層に接続して形成された第1導電型の第3の導電層とを有する半導体層と、半導体層内に設けられ、第2の導電層と第3の導電層とを分離する第2の素子分離絶縁膜と、第2の導電層上に形成されたゲート絶縁膜と、ゲート絶縁膜上に形成され、第3の導電層を介して第1の導電層に電気的に接続されたゲート電極とを有する。

(もっと読む)

半導体装置及びその製造方法、並びにデータ処理システム

【課題】トランジスタのオン電流を十分に確保することが可能な信頼性の高い半導体装置を提供する。

【解決手段】活性領域6を分断する2つの埋め込みゲート用の溝部8a,8bにゲート絶縁膜9を介して埋め込まれたゲート電極7a,7bと、2つの埋め込みゲート用の溝部8a,8bによって分断された3つの活性領域6a,6b,6cのうち、中央部に位置する活性領域6bを分断するビットコンタクト用の溝部11の両側面に、埋め込みゲート用の溝部8a,8bの底面と同程度の深さで不純物を拡散させることによって形成された第1の不純物拡散層13a,13bと、中央部を挟んだ両側に位置する活性領域6a,6cに、ゲート電極7a,7bの上面と同程度の深さで不純物を拡散させることによって形成された第2の不純物拡散層14a,14bとを備える。

(もっと読む)

半導体装置の製造方法

【課題】FinFETの特性が均一な半導体装置の製造方法を提供する。

【解決手段】実施形態に係る半導体装置の製造方法は、半導体基板の上層部分に凹部を形成する工程と、前記凹部内に犠牲材を配置する工程と、前記半導体基板及び前記犠牲材を選択的に除去することにより、一方向に延び、周期的に配列された複数本のフィンを形成する工程と、前記フィン間の空間の下部に素子分離絶縁膜を形成する工程と、前記犠牲材を除去する工程と、前記フィンの露出面上にゲート絶縁膜を形成する工程と、前記素子分離絶縁膜上に、前記フィンを跨ぐように、前記一方向に対して交差した方向に延びるゲート電極を形成する工程と、を備える。

(もっと読む)

半導体装置及びその製造方法

【課題】通電領域表面の周辺の強電界の影響がナノワイヤに及び難くして、ホットキャリアの生成やオフリーク電流を低減する。半導体装置を高性能化する。

【解決手段】基板の表面よりも深い位置に配置され互いに対向する2つの側壁を有する導電膜と、導電膜の2つの側壁の側方に形成され互いに同じ導電型の半導体領域である第1及び第2の通電領域と、導電膜を貫通して2つの半導体領域どうしを接続し第1及び第2の通電領域の導電型とは逆導電型の半導体領域であるナノワイヤと、導電膜と前記ナノワイヤとの境界部に形成された絶縁膜と、を有することを特徴とする半導体装置。

(もっと読む)

半導体装置の製造方法

【課題】SOI基板を使用せずバルク基板を用いてフィン型FETを製造すると、従来技術では素子領域と半導体基板との間の絶縁耐圧が低くなっていた。

【解決手段】本発明の半導体装置の製造方法では、素子分離膜の形成時にマスクとして用いる耐酸化用膜を、半導体基板表面に設ける溝部の底部から所定の距離まで離間した部分を除いて立設部の表面に形成することで、立設部の下部の素子分離膜がほぼ一定の膜厚にすることができた。このため、立設部と半導体基板との間の絶縁耐圧が向上し、リークもなく、信頼性が向上した。

(もっと読む)

1 - 20 / 915

[ Back to top ]