Fターム[5F032DA42]の内容

Fターム[5F032DA42]の下位に属するFターム

Fターム[5F032DA42]に分類される特許

1 - 20 / 26

固体撮像装置および固体撮像装置の製造方法

【課題】本発明の一つの実施形態の目的は、素子分離特性を向上可能な固体撮像装置および固体撮像装置の製造方法を提供することである。

【解決手段】実施形態によれば、固体撮像装置の製造方法が提供される。固体撮像装置の製造方法は、素子分離領域形成工程と、電荷蓄積領域形成工程とを含む。素子分離領域形成工程では、第1導電型の半導体層をエピタキシャル成長させて光電変換素子間を分離する素子分離領域を形成する。電荷蓄積領域形成工程では、第2導電型の半導体層をエピタキシャル成長させて前記光電変換素子における電荷蓄積領域を形成する。

(もっと読む)

半導体装置

【課題】出力トランジスタの形成領域から他の素子の形成領域への電子の移動を抑制する効果が高く、素子の誤動作を抑制できる半導体装置を提供する。

【解決手段】半導体基板SUBと、1対の注入元素子DRと、アクティブバリア構造ABと、p型接地領域PGDとを備える。半導体基板SUBは主表面を有し、かつ内部にp型領域を有する。1対の注入元素子DRは、p型領域上であって主表面に形成される。アクティブバリア構造ABは、主表面において1対の注入元素子DRに挟まれる領域に配置される。p型接地領域PGDは、主表面において1対の注入元素子DRに挟まれる領域を避けて1対の注入元素子DRおよびアクティブバリア構造ABよりも主表面の端部側に形成され、かつp型領域に電気的に接続された、接地電位を印加可能な領域である。p型接地領域PGDは、1対の注入元素子DRに挟まれる領域と隣り合う領域において分断されている。

(もっと読む)

半導体装置及びその製造方法

【課題】IGBT形成領域とその制御回路等形成領域とをPN接合分離法で分離し、且つIGBTからの漏れ電流が発生せず、制御回路等のCMOSトランジスタがラッチアップ等することのない高品質の半導体装置を実現する。

【解決手段】P型半導体基板1上に多層からなるN型エピタキシャル層3等を形成する。該N型エピタキシャル層3等をP+型分離層13等によりIGBT形成領域50と制御回路等形成領域40に分離する。該IGBT形成領域50の最下層の前記N型エピタキシャル層3と前記P型半導体基板1の双方に延在するN+型埋め込みガード層2を形成する。また該N+型埋め込みガード層2の端部と接続し前記エピタキシャル層3等の表面まで延在するN+型ガードリング9等を形成する。前記N+型埋め込みガード層2と該N+型ガードリング9等に囲まれた前記エピタキシャル層3等にIGBTを形成する。

(もっと読む)

高耐圧半導体装置

【目的】裏面工程追加などの複雑な製造プロセスを一切伴わず、レベルシフタ素子である高耐圧NMOSFETの高耐圧化が安価で実現できるほか、安定した高電位配線、低いオン電圧による低電圧駆動かつ高速応答性の実現を可能とする高耐圧半導体装置および高電圧集積回路装置を提供することにある。

【構成】支持基板100上に埋め込み酸化膜200を介して半導体層101が形成され、半導体層101上に高電位側第2段トランジスタ302とそれを囲むように低電位側第1段トランジスタ301を形成し、第2段トランジスタのドレイン電極1071と第1段トランジスタ301のソース電極1072を接続する。第2段トランジスタ302のドレイン電極114はドレインパッド119と接続される。

(もっと読む)

半導体装置の製造方法

【課題】周辺トランジスタやメモリセルを構成するnMISトランジスタの駆動特性の劣化を抑制することができる半導体装置の製造方法を提供する。

【解決手段】n型の電界効果型トランジスタを含む半導体装置の製造方法において、半導体基板に対してp型不純物となる元素を有するp型不純物元素含有ガスを含むエッチングガスを用いて、半導体基板に素子分離溝を形成するとともに、素子分離溝の内面に、p型不純物を含む不純物層を形成する素子分離溝形成工程と、素子分離溝内に塗布型絶縁膜を埋め込んで素子分離絶縁膜を形成する素子分離絶縁膜形成工程と、を含む。

(もっと読む)

セミコンダクタ−オン−インシュレータ型構造中の酸化物層を局所的に溶解する方法

本発明は、支持基板(1)、酸化物層(2)および薄い半導体層(3)を順番に含むセミコンダクタ−オン−インシュレータ型構造を処理する方法であって、(a)薄い半導体層(3)上に、窒化シリコンまたは酸窒化シリコンのマスク(4)を形成して、前記層(3)の表面に、マスク(4)によって覆われておらず、所望のパターンに配置された、いわゆる露出エリア(3a)を画定するステップと、(b)中性雰囲気または制御された還元性雰囲気で、制御された温度条件および時間条件の下、熱処理を加えて、酸化物層(2)の酸素の少なくとも一部を薄い半導体層(3)を通して拡散させ、それによって前記所望のパターンに対応した酸化物層のエリア(2a)の酸化物の厚さの制御された低減を達成するステップとを含む方法に関する。ステップ(a)で、マスク(4)は、薄い半導体層(3)の厚さの中に少なくとも部分的に埋め込まれるように形成される。  (もっと読む)

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】寄生容量が小さく、高速・低消費電力で動作する、或いは、寄生効果が無く、高静電気破壊耐量を有する優れた素子特性が得られる完全誘電体分離型のICを低コストで製造することのできる半導体装置を提供する。

【解決手段】トレンチ型誘電体分離層により素子領域側面が誘電体で分離されたn型又はp型のエピタキシャル層に、横型のMOSFETあるいは縦型バイポーラトランジスタ、縦型のダイオード等の半導体素子を形成する。その後素子形成側を接着剤等で保持基板と接着する等して、しかる後にシリコン単結晶基板の裏面を研削・研磨の後、エッチングを行ってエピタキシャル層を成長させる前に形成したエッチングストップ層でエッチングを停止してトレンチ先端を露出させる。その面にCVD酸化膜等の絶縁層を形成して、トレンチと絶縁層で素子を誘電体で完全に分離する。更に半田等の接着剤を用いて支持基板に貼り付け、素子側の保護基板を除去する。

(もっと読む)

半導体装置

【課題】複数の回路を搭載する場合において、回路間のノイズ伝播などの誤動作を抑制することが可能な半導体装置を提供すること。

【解決手段】支持基板と、前記支持基板上に設けられた絶縁層と、前記絶縁層上に設けられ第1回路を有する第1半導体層と、前記絶縁層上に設けられ、前記第1半導体層と絶縁され、第2回路を有する第2半導体層と、前記絶縁層上のうち前記第1半導体層と前記第2半導体層との間に設けられ、前記第1半導体層及び前記第2半導体層とそれぞれ絶縁され、電気的に接地された容量領域を有する分離層とを備える。

(もっと読む)

半導体装置

【課題】 複数の個別半導体素子(チップ)を1つのパッケージに内蔵した複合素子の半導体装置では、それぞれの個別半導体チップが実装されるリードフレームや樹脂層が必要であり、装置の小型化が進まない問題があった。また、フリップチップ実装方式の半導体装置ではリードフレームや樹脂層が不要なため小型化は可能であるが、複合素子を集積化することは困難であった。

【解決手段】 同一基板の一主面から他の主面まで貫通する分離領域を設ける。分離領域で分離された第1の個別半導体素子領域および第2の個別半導体素子領域に、それぞれ個別半導体素子を形成する。これにより、1チップに複数の個別半導体素子を集積化したフリップチップ実装方式の複合素子が実現でき、半導体装置(複合素子)の小型化が実現する。

(もっと読む)

半導体記憶装置

【課題】形成面積の増大を抑えつつ、ソフトエラー発生を抑制することが可能な半導体記憶装置を提供する。

【解決手段】絶縁体層上の半導体層に形成されるSRAMセルアレイにおいて、各セルのアクセストランジスタおよびドライバトランジスタのボディーを、絶縁体層にまで達するトレンチ分離(完全分離)によってセル毎に分離する。またその完全分離を、絶縁体層には達しないトレンチ分離(部分分離)内にスリット状に形成し、そのスリット状の完全分離を跨ぐようにボディーコンタクトを形成することによって、当該ボディーコンタクトを隣接セル間で共有させる。

(もっと読む)

SOI基板の製造方法

【課題】エッチバック法で薄膜化されたシリコン層の基板面内での膜厚均一性と抵抗率均一性に優れたSOI基板の製造方法を提供すること。

【解決手段】単結晶Si基板10の表面にBイオンを注入して最表面に深さLの高濃度ボロン添加p層11を形成した後、単結晶Si基板10と石英基板20を室温で密着させて貼り合わせる。単結晶Si基板10の裏面から、化学的エッチングを施して厚みをL以下とする。得られたSOI基板に水素含有雰囲気中で熱処理を施して、高濃度ボロン添加p層11からBを外方拡散させて所望の抵抗値のボロン添加p層12を得る。この熱処理中に、Si結晶内部のBは雰囲気中の水素と結び付いた状態で結晶外に拡散し、高濃度ボロン添加p層11内のB濃度は低下してゆくこととなる。このときの熱処理温度は、絶縁性基板の軟化点の観点から熱処理温度の上限は1250℃とし、Bが拡散し得る温度の下限として700℃を選択する。

(もっと読む)

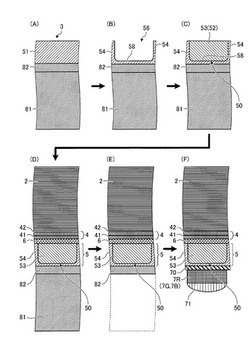

半導体装置の製造方法及び半導体装置

【課題】半導体基板の溝に埋め込まれた素子分離膜上に抵抗素子を有する半導体装置において、抵抗素子と半導体基板の間でショートが発生することを抑制する。

【解決手段】本半導体装置の製造方法は、第2素子領域1aに位置する半導体基板1、及び素子分離膜2aを、絶縁性のマスク膜54で覆う工程と、マスク膜54をマスクとして半導体基板1を熱酸化することにより、第1素子領域1bに位置する半導体基板1に、第1トランジスタのゲート絶縁膜3bを形成する工程と、マスク膜54を、素子分離膜2aの少なくとも一部上に位置する部分を除いて除去する工程と、半導体基板1を熱酸化することにより、第2素子領域1aに位置する半導体基板1に、第2トランジスタのゲート絶縁膜3aを形成する工程と、素子分離膜2a上に残存するマスク膜54上に、抵抗素子4cを形成する工程とを具備する。

(もっと読む)

高電圧トランジスタ及びその製造方法

【課題】寄生トランジスタによるハンプの発生を防止できる高電圧トランジスタとその製造方法を提供する。

【解決手段】半導体基板上に所定の幅を維持しつつ活性領域の中央部位に沿って延びるゲート電極の両側の半導体基板に形成され、部分的に素子分離膜の下部に拡張して形成される第2ウェルを備え、活性領域は、ゲート電極の下部に位置しつつ素子分離膜を離隔させる第1活性領域及び第1活性領域と素子分離膜により限定される第2活性領域を備える高電圧トランジスタ及びその製造方法である。

(もっと読む)

イメージセンサー及びその製造方法

【課題】暗電流が減少したイメージセンサー及びその製造方法提供する。

【解決手段】イメージセンサーは、ピクセル領域とロジック領域を含む。前記ピクセル領域のピクセル素子分離膜は前記ロジック領域のロジック素子分離膜の側壁達より小さな傾斜度を有するピクセル素子分離膜の側壁を含む。前記不純物層を少なくとも一部の前記ピクセル素子分離膜の側壁に隣接して提供することができて、少なくとも一部の前記ロジック素子分離膜の側壁には、前記不純物層が提供されていない。前記不純物層及び/又はより小さな傾斜度を有するロジック素子分離膜の側壁を前記ロジック領域のNMOS装置に提供する一方、前記ロジック領域のPMOS装置には提供されていない。ドーピングされた犠牲膜は、前記不純物を製造するのに使用可能である。

(もっと読む)

半導体装置及びその製造方法

【課題】

高耐圧素子の高耐圧特性を確保しつつ、高耐圧素子と低耐圧素子とが良好な特性を有する半導体装置を提供する。

【解決手段】

高耐圧素子と低耐圧素子とを有する半導体装置が、高耐圧素子が形成された高耐圧素子領域と、低耐圧素子が形成された低耐圧素子領域とが規定された半導体基板と、高耐圧素子領域に設けられた第1LOCOS分離構造と、低耐圧素子領域に設けられた第2LOCOS分離構造とを含む。第1LOCOS分離構造は、半導体基板の表面に形成されたLOCOS酸化膜と、その上に形成されたCVD酸化膜からなり、第2LOCOS分離構造は、LOCOS酸化膜からなる。

(もっと読む)

半導体装置

【課題】 小さな占有面積で分離構造の形成が可能であり、かつ、良好な素子特性が得られるトレンチ構造を有する半導体装置を提供する。

【解決手段】 第1導電型の半導体基板と、半導体基板の上に設けられた第2導電型の半導体層と、半導体層中に設けられたトレンチと、トレンチの壁面に沿って設けられた第1導電型のトレンチ拡散層と、トレンチに埋め込まれた埋め込み導電体とを含む半導体装置において、更に、トレンチの壁面と埋め込み導電体との間に絶縁膜が設けられている。

(もっと読む)

半導体装置及びその製造方法

【課題】半導体装置(DRAM等)を構成するメモリセル(DRAMメモリセル等)の信号量を増加させる。

【解決手段】基板と、前記基板に形成された素子分離用の溝の内部に形成され、絶縁膜と導電層からなる素子分離層と、前記素子分離層間に形成され、前記絶縁膜により前記導電層と分離されている信号電荷蓄積用の第1の導電型の半導体層と、前記第1の導電型の半導体層の下部に形成された第2の導電型の半導体層と、前記第1の導電型の半導体層の上部に形成されたトランジスタとを備えることを特徴とする半導体装置。

(もっと読む)

半導体素子の作製方法及び半導体素子

【課題】リーク電流の発生が抑制されると共に、ガラス基板が使用できる温度で素子分離をおこない微細な素子を形成できる方法を提供する。

【解決手段】ガラス基板上に下地膜を形成する第1工程と、下地膜上に半導体膜を形成する第2工程と、半導体膜上に該半導体膜の酸化又は窒化を防止する膜を所定のパターンに形成する第3工程と、ガラス基板の温度を該ガラス基板の歪点より100℃以上低い温度とし、半導体膜の所定のパターンに覆われていない領域をラジカル酸化又はラジカル窒化して素子分離をおこなう第4工程とを有し、ラジカル酸化又はラジカル窒化は、プラズマ生成領域と離間して配置された半導体膜上において、電子温度が0.5eV以上1.5eV以下好ましくは1.0eV以下、電子密度が1×1011cm−3以上1×1013cm−3以下であるプラズマ処理室でおこなわれる。

(もっと読む)

半導体装置およびその製造方法

【課題】チャネル層に応力が付加され、かつ高信頼なMOSFETを実現する。

【解決手段】半導体基板と、前記半導体基板の表面に対向して設けられ、単結晶または多結晶構造を有する一対のソース・ドレイン電極と、前記ソース・ドレイン電極の間の前記半導体基板の表面に形成された単結晶チャネル領域と、前記チャネル領域上にゲート絶縁膜を介して形成されたゲート電極と、前記ソース・ドレイン電極の上部に形成された金属化合物層と、前記ソース・ドレイン電極の下部に位置し、前記ソース・ドレイン電極を構成する物質の固有の格子間隔とは異なる格子間隔を保持した結晶構造を有する応力付与層と、前記応力付与層の下部に位置する第1の絶縁層とを具備する。

(もっと読む)

接合型電界効果トランジスタ及びその製造方法

【課題】

接合型電界効果トランジスタの重要な課題のひとつであるIDSS特性のばらつきを抑えた接合型電界効果トランジスタ及び接合型電界効果トランジスタの製造方法を提供する。

【解決手段】

第1の導電型半導体層11と、第1の導電型半導体層11上に設けられた第2の導電型半導体層12と、第2の導電型半導体層12に設けられた素子形成領域と、素子形成領域を囲むガードリング領域19と、を備え、ガードリング領域19は、第2の導電型半導体層12を貫通し、第1の導電型半導体層11の表面に達する絶縁分離層を有し、絶縁分離層の側面に第1の導電型半導体層11を設けた接合型電界効果トランジスタ。

(もっと読む)

1 - 20 / 26

[ Back to top ]