Fターム[5F032DA52]の内容

Fターム[5F032DA52]の下位に属するFターム

酸化 (901)

窒化 (52)

イオン注入の利用 (309)

結晶欠陥・ライフタイムキラーの利用 (6)

Fターム[5F032DA52]に分類される特許

1 - 20 / 22

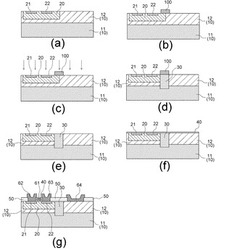

半導体装置の製造方法、半導体装置

【課題】SiCが用いられる半導体層中において、簡易な工程で再現性よく埋め込み絶縁層を形成する。

【解決手段】単結晶のSiC12の表面の温度を局所的に急激に上昇させ、その後で急激に冷却することによって、単結晶を局所的に非晶質化層30を形成することができる。この非晶質層30は、元の単結晶SiCの導電型や抵抗率に関わらず、高抵抗層(絶縁層)となる。このため、こうした非晶質層を埋め込み絶縁層と同様に使用することができる。このためには、(1)レーザー光を効率的に吸収する層100を局所的に半導体層の上に形成してからレーザー光を照射する、(2)レーザー光を局所的に半導体層に照射する、という2つの手段のいずれかを用いることができる。

(もっと読む)

シリカ系絶縁膜形成用塗布液

【課題】ポットライフが長く、焼成してシリコン酸化物としたときの硬化収縮率が小さく、更にクラック耐性に優れかつ耐電圧のばらつきが小さい絶縁膜を形成できる縮合反応物溶液の提供。

【解決手段】(I)(i)下記一般式(1):R1nSiX14-n (1){式中、nは0〜3の整数であり、R1は水素原子又は炭素数1〜10の炭化水素基であり、X1はハロゲン原子、炭素数1〜6のアルコキシ基又はアセトキシ基である}で表されるシラン化合物に由来するポリシロキサン化合物と、(ii)シリカ粒子と、を少なくとも含有する縮合成分を縮合反応させて得られる縮合反応物、及び(II)溶媒を含み、該一般式(1)で表されるシラン化合物が4官能シラン化合物及び3官能シラン化合物を少なくとも含有し、該シリカ粒子中の炭素量が0.05質量%以上0.65質量%未満である、縮合反応物溶液。

(もっと読む)

シャロートレンチアイソレーション膜のためのアミノシラン

【課題】記憶及び論理回路を含む半導体基材、例えば、1つ又は複数の集積回路構造をその上に有するシリコンウェハにおいて用いられるシャロートレンチアイソレーションのための高アスペクト比の特徴のギャップを充填するための酸化条件下で二酸化ケイ素含有膜をスピンオン堆積させる方法を提供する。

【解決手段】高アスペクト比の特徴を有する半導体基材を用意する工程、該半導体基材を低分子量のアミノシランを含む液体配合物と接触させる工程、該半導体基材上に該液体配合物を塗布することにより膜を形成する工程、及び該膜を酸化条件下において高温で加熱する工程を含む方法が提供される。この方法のための組成物もまた記載される。

(もっと読む)

半導体装置およびその製造方法

【課題】応力の発生が緩和され、かつ、良質な埋め込み構造を有する半導体装置、およびその製造方法を提供する。

【解決手段】第1の領域AR1、第2の領域AR2を有し、さらwに、第1の領域AR1が第1の溝TR1を、第2の領域AR2が第2の溝TR2、を有する基板の溝に絶縁膜を埋設する。このとき、第1の溝TR1、第2の溝TR2のそれぞれを、その溝の幅の相違に応じて、径の異なる第1のナノ粒子CS1、第2のナノ粒子CS2で、埋め込んで絶縁膜を形成する。

(もっと読む)

半導体装置の製造方法

【課題】素子分離絶縁膜に対しボイドの発生を抑制できるようにする。

【解決手段】素子分離溝3中の少なくとも一部に塗布法により塗膜4cを埋込み、当該塗膜4cをベークすることで膜中の溶媒を蒸散させてポリシラザン膜4dを形成する。次に、ポリシラザン膜4dを塗布した半導体基板2を酸化性雰囲気中で酸化炉内に導入し、該酸化炉内を真空排気した状態で保持することでポリシラザン膜4d内に残留したガスを蒸散させる。次に、ポリシラザン膜4dを塗布した半導体基板2を酸化性雰囲気中で減圧状態に保持しポリシラザン膜4dをメルトさせることによりポリシラザン膜4d中に残留したガスを蒸散させる。次に、ポリシラザン膜4dを塗布した半導体基板2を水蒸気酸化温度に保持し、水蒸気酸化を行うことでポリシラザン膜4dについてシリコン酸化膜に転換する。

(もっと読む)

半導体装置およびその製造方法

【課題】線形性に優れた半導体抵抗素子を提供する。

【解決手段】本発明の半導体装置は、GaAs基板101上に形成され、3−5族化合物半導体から構成されるHBT130と、GaAs基板101上に形成され、HBT130を構成する半導体エピタキシャル層の少なくとも1層から構成される半導体抵抗素子120とを備え、半導体抵抗素子120は、ヘリウム不純物を含む。

(もっと読む)

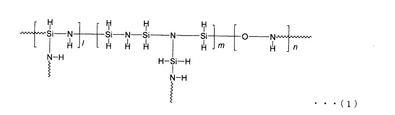

ポリシラザンおよびその合成方法、半導体素子製造用組成物およびその半導体素子製造用組成物を用いた半導体素子の製造方法

【課題】高分子量を有しながらも溝の充填力が優れたポリシラザンおよびその合成方法、ポリシラザンを含む半導体素子製造用組成物およびその半導体素子製造用組成物を用いた半導体素子の製造方法を提供する。

【解決手段】ポリシラザンは、反応溶媒内に反応物として添加されたジクロロシラン、トリクロロシラン、およびアンモニアを触媒存在下で反応させることによって合成することができ、ポリスチレン換算重量平均分子量が2000〜30000であり、下記化学式(1)で示される。

【化1】

(もっと読む)

アクティブ層の厚み減少を伴う歪トランジスタを形成するための構造歪を与えられた基板

【解決手段】

歪を与えられたSOI半導体層において、典型的には溝分離構造のパターニングの間に生じ得る応力緩和は、アクティブ領域の適切に減少させられた目標高さを選択することによって低減することができ、それにより、顕著な量の初期歪成分を未だに含むであろう減少させられた高さのアクティブ領域上へのトランジスタ要素の形成が可能になる。減少させられた高さのアクティブ領域は、完全に減損した電界効果トランジスタを形成するために有利に用いることができる。

(もっと読む)

半導体装置の製造方法

【課題】 素子分離用のトレンチと層間絶縁膜とを同時形成する技術を提供する。

【解決手段】 SOI基板4の素子形成領域に半導体構造6〜12を形成し、SOI基板4の表面において素子形成領域を一巡する素子分離領域に対応する開口16を有する酸化シリコン膜14をSOI基板4の表面に形成する。シリコンをエッチングして酸化シリコンをエッチングしないエッチングガスと、そのエッチングガスによってエッチングされたシリコンと結合して副生成物を生成する添加ガスとが混合した混合ガスを用いてSOI基板4の表面をドライエッチングすることによって、開口16から露出している範囲のSOI基板4にトレンチ18を形成するとともに、酸化シリコン膜14の表面に副生成物を堆積して層間絶縁膜22を上記のトレンチ18と同時に形成する。この層間絶縁膜22は、その後の工程で除去されずに完成した半導体装置2に残存する。

(もっと読む)

III族窒化物半導体からなる半導体素子およびその製造方法

【課題】III 族窒化物半導体からなる半導体素子の製造方法において、素子分離工程を容易とすること。

【解決手段】HFET1は、SI−SiCからなる基板10上に、ノンドープのGaN層11、ノンドープのAlGaN層12が積層され、AlGaN層12上にソース電極13、ゲート電極14、ドレイン電極15が形成され、素子分離領域16によって他の素子と分離されている構造である。素子分離領域16は、CF4 ガスプラズマに晒して絶縁化させることで形成した。このようにプラズマ曝露によって素子分離領域を形成したとしても素子の動作に影響を与えることはなく、良好な絶縁特性が得られる。

(もっと読む)

局所的にGeを濃縮するステップを含む、絶縁層上に半導体を製造するステップ

【課題】半導体オンインシュレータ基板を、表面シリコン層を埋め込み絶縁層と呼ばれる電気絶縁層の上に含むSOI基板を利用して形成する方法を提供する。

【解決手段】積層体をエッチングが埋め込み絶縁層12に達するまで行なうことにより、積層体の少なくとも一つのアイランド14を有するエッチング済み構造を得る。または表面シリコン層に達するまで行なうことにより積層体の少なくとも一つのシリコン領域及び少なくとも一つのアイランド14を有するエッチング済み構造が得られるようにする工程、酸化防止保護マスク17をエッチング済み構造の上に形成し、保護マスクによって、アイランドのシリコン酸化膜層のみが露出して残されるようにする工程、アイランドのSi1−XGeX層15のゲルマニウムを濃縮して、ゲルマニウムリッチ層を得られるようにする。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】多数キャリアの移動度を向上させたSBSIデバイスを実現可能とした半導体装置の製造方法及び半導体装置を提供する。

【解決手段】Si基板1上にSiGe層を形成する工程と、SiGe層上にSi層5を形成する工程と、Si層5及びSiGe層をエッチングして、Si層5及びSiGe層を貫く支持体穴を形成する工程と、支持体穴に支持体11、12を形成する工程と、Si層5をエッチングして、SiGe層を露出させる溝H1、H2を形成する工程と、溝H1、H2を介してSiGe層をエッチングすることにより、Si層5とSi基板1との間に空洞部を形成する工程と、空洞部にSiO2膜23を形成する工程と、引っ張り応力を有する埋め込み膜31を溝H1、H2に形成する工程と、を含む。支持体11には引っ張り応力を有する絶縁膜を用い、支持体12には圧縮応力を有する絶縁膜を用いる。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体基板に形成された拡散層および拡散層間分離絶縁膜の一部がリセスされた溝ゲート構造を有する半導体装置において、拡散層間分離絶縁膜の埋設性とチャネル抵抗の低減を両立する。

【解決手段】溝ゲート構造となる溝内において、拡散層間分離絶縁膜を拡散層に対して選択的にウェットエッチングして拡散層が突出部した構造を形成し、さらに突出した拡散層を選択エピタキシャル成長させることで拡散層の突出部に庇状の構造を形成する。

(もっと読む)

薄膜トランジスタの製造方法、薄膜トランジスタ及び画像表示装置

【課題】簡便なプロセスで素子分離が可能な薄膜トランジスタの製造方法、薄膜トランジスタおよび画像表示装置を提供すること。

【解決手段】絶縁基板上にゲート電極、ゲート絶縁膜、一対の主電極領域を形成する工程と、一対の主電極領域上を含む絶縁基板上の全面に有機半導体層を形成する工程と、有機半導体層と一対の主電極領域との間のチャネル領域を覆う封止層を形成する工程と、有機半導体層の前記封止層の形成されていない領域を非活性化させる工程と、を備えたことを特徴とする薄膜トランジスタの製造方法。

(もっと読む)

半導体装置の製造方法

【課題】STI法を用いて形成した素子分離領域の幅が狭く、かつ溝ゲート構造を有する半導体デバイスを製造するにあたり、絶縁体中に存在するボイドによるゲート電極間のショートを防止できる半導体装置の製造方法を提供する。

【解決手段】半導体基板をパターニングして素子分離用溝を形成する工程と、素子分離用溝に絶縁体を埋め込んで素子分離領域を形成する工程と、CMP法により表面を平坦化して、フィールド形成用絶縁膜を露出させる工程と、絶縁体の上部を除去する工程と、フィールド形成用絶縁膜を除去する工程と、素子分離領域が形成された半導体基板をパターニングして、ゲート電極を形成する領域にゲート溝を形成する工程と、絶縁体の内部に存在しているボイドの上部を開口させる工程と、ゲート溝内にゲート電極を形成する工程とを有する方法で半導体装置を製造する。

(もっと読む)

混合マイクロテクノロジー構造を製造する方法、およびそれによって得られる構造

【課題】混合マイクロテクノロジー構造を製造する方法を提供すること。

【解決手段】この方法は、犠牲層に隣接する混合層15が上に形成された犠牲層2を含み、第1の材料の第1のパターン1A、1B、1C、および第1の材料とは異なる第2の材料、例えば電気絶縁材料の第2のパターン5を含む仮の基板が生成されるステップと、この犠牲層は前記混合層の混合表面を曝すように取り除かれ、この混合表面は第1のパターンの一部および第2のパターンの一部を含むステップと、直接結合によって、この混合表面上に第3の材料の連続カバー層が生成されるステップとを含んでいる。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】 工程数の増大を抑制しつつ、絶縁体上に形成された半導体層の素子分離を安定して行うとともに、寄生トランジスタによる電流リークを抑制する。

【解決手段】 露出面9を介してエッチングガスまたはエッチング液を第1半導体層5に接触させることにより、半導体基板1と第2半導体層6との間に空洞部10を形成し、露出面9を介して第2半導体層6の端部をエッチングすることにより、支持体層8から露出された第2半導体層6の端部を丸めた後、半導体基板1および第2半導体層6の熱酸化を行うことにより、半導体基板1と第2半導体層6との間の空洞部10に埋め込み絶縁層11を形成し、第2半導体層6の丸められた端部にかかるように配置されたゲート電極14を第2半導体層6上に形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】良好な耐圧を得ることができる半導体装置およびその製造方法を提供する。

【解決手段】絶縁分離領域14の絶縁部材13の先端21をn半導体基板1cの裏面20から引っ込ませた凹状とすることで、n半導体基板1cの底部のコーナーでの電界強度を緩和して、良好な耐圧を得ることができる。また、n半導体基板1cの裏面20にフィールドストップ層22などの高濃度領域を形成することで、表面から伸びた空乏層が裏面20に達するのを防止して、裏面20に形成した絶縁膜23とn半導体基板1cとの界面に導入される表面準位の影響を排除し、良好な耐圧を得ることができる。

(もっと読む)

バイポーラートランジスターの作製方法

本発明は、標準的な浅いトレンチ分離作製方法を適用してバイポーラートランジスターを作製するための方法を提供するものであり、第一トレンチ(5,50)の中に縦型バイポーラートランジスター(29)又は横型バイポーラートランジスター(49)と、第二トレンチ(7,70)の中に浅いトレンチ分離領域(27,270)を同時に形成する。更に本作製方法は、第一トレンチ(5,50)の中に縦型バイポーラートランジスター(27)、第三トレンチの中に横型バイポーラートランジスター(49)、及び第二トレンチ(7,70)の中に浅いトレンチ分離領域(27,270)を同時に形成することもある。  (もっと読む)

(もっと読む)

混在型半導体集積回路及びその製造方法

【課題】 同一基板に機械的駆動系及び電気的駆動系を混在しつつ、電気的駆動系上に機械的駆動系を積層する構造を無くした簡易な構造を有するMEMSを備えた混在型半導体集積回路及びその製造方法を提供する。

【解決手段】 混在型半導体集積回路1は、基板10上の第1の領域Aに配設された第1の半導体活性層31と、第1の半導体活性層31の側面周囲を取り囲む絶縁分離領域40と、基板10上の第1の領域Aに隣接する第3の領域Cに配設され、絶縁分離領域40の一部及びトレンチ45により側面周囲が取り囲まれたメカニカル電極331と、メカニカル電極331に一端が接続され、他端が絶縁分離領域40の一部上を通過して第1の半導体活性層31上に延在する第2の薄膜配線90とを備えている。

(もっと読む)

1 - 20 / 22

[ Back to top ]