Fターム[5F033JJ19]の内容

半導体集積回路装置の内部配線 (234,551) | 層間接続のコンタクト層の材料 (22,060) | 金属及びその合金(シリサイドを除く) (14,566) | 高融点金属 (7,010) | W (2,609)

Fターム[5F033JJ19]に分類される特許

2,001 - 2,020 / 2,609

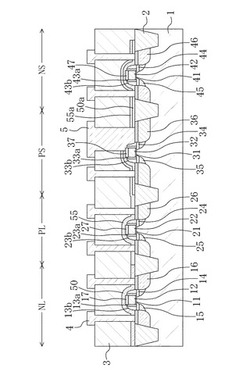

半導体装置およびその製造方法

【課題】ロジック領域におけるトランジスタの上を応力を有する膜で覆って能力を向上させると共に、SRAM領域において、各トランジスタの能力のバランスを保持し、リーク電流の発生を抑制する事ができる半導体装置及びその製造方法を提供する。

【解決手段】半導体装置では、N型ロジック領域NLにおけるトランジスタが引っ張り応力を有する膜50により覆われ、P型ロジック領域PLにおけるトランジスタが圧縮応力を有する膜55により覆われている。そして、P型SRAM領域PSにおけるトランジスタおよびN型SRAM領域NSにおけるトランジスタは、引っ張り応力を有する膜50aおよび圧縮応力を有する膜55aからなる積層膜により覆われている。

(もっと読む)

半導体装置およびその作製方法

【課題】基板上に設けられた半導体素子を複数積層させた場合であっても、積層した半導体素子が基板を通して電気的に接続可能となる半導体装置およびその作製方法を提供することを目的とする。

【解決手段】基板の一方の面に選択的に凹部または基板の一方の面から他方の面に貫通する開口部を形成し、基板の一方の面および凹部または開口部を覆うようにトランジスタを有する素子群を形成し、基板を他方の面から薄膜化することによって、凹部または開口部に形成された素子群を露出させることを特徴としている。基板を薄膜化する手段としては、基板の他方の面から研削処理、研磨処理、化学処理によるエッチング等を行うことによって基板を部分的に除去することによって行うことができる。

(もっと読む)

半導体集積回路装置およびその製造方法

【課題】 製造工程においてトランジスタ特性の変動を招くことなく、貫通配線部の低抵抗化および高集積化が可能な半導体集積回路装置およびその製造方法を提供する。

【解決手段】 この半導体集積回路装置10は、基板11上に集積回路が形成される半導体層L1〜L3が複数積層され、積層構造を有する半導体集積回路装置であって、複数の半導体層の各々は、基板11に、上記の集積回路を含む半導体集積回路部16と、半導体集積回路部16に含まれる集積回路を他の半導体層の集積回路に電気的に接続する貫通配線17aと、この貫通配線を囲んで半導体集積回路部から絶縁した囲み絶縁部18とを有するように構成される。

(もっと読む)

半導体装置及びその製造方法

【課題】 容量密度を高めることが可能な、立体構造のMIMキャパシタにおいてMIMキャパシタ直下の配線領域が配線として利用でき、配線層数の増大や、ICチップ面積の増大を防ぐことのできるMIMキャパシタを備えた半導体装置及びその製造方法を提供する。

【解決手段】 下層配線を被覆するように層間絶縁膜301を形成し、層間絶縁膜に対し、下層配線の上面を基準とする層間絶縁膜の膜厚よりも小さな高さの開口部を形成し、開口部を被覆するように上部電極204、容量膜401、下部電極203から構成されるMIMキャパシタを形成する。

(もっと読む)

シリカ系被膜の製造方法、シリカ系被膜および半導体装置

【課題】 誘電率と被膜強度を表わすヤング率とに優れたシリカ系被膜、特に、比誘電率が2.7以下と小さく、さらに被膜強度を表わすヤング率が半導体配線層作製プロセスに耐えうるだけの強度特性を備えたシリカ系被膜の形成方法を提供する。

【解決手段】 (i)シリカ系被膜形成用塗布液を基板上に塗布し、(ii)塗布後の基板を加熱処理し、(iii)加熱後の基板に、ケイ素の不対電子を安定化できる物質を含む雰囲気中で活性エネルギー線を照射して、シリカ系被膜を得る。

(もっと読む)

半導体装置の製造方法

【課題】銅配線形成時のディッシングを防止する。

【解決手段】半導体基板12上面12a上の第1絶縁膜14の表面を覆う拡散防止膜22、拡散防止膜上を覆う第2絶縁膜24、及び第2絶縁膜上を覆うキャップ膜26を順次に積層する。拡散防止膜、第2絶縁膜及びキャップ膜を貫通する配線溝部30であって、この配線溝部の底面からキャップ膜の表面までの高さh1に対する、配線溝部の延在方向に直交する方向の幅w1の比率を最大でも2.8倍として当該配線溝部を形成する。キャップ膜の表面及び配線溝部の表面を覆うバリアメタル膜を形成する。バリアメタル膜上を覆う配線膜を成膜する。配線膜の表面からキャップ膜の表面が露出するまで、配線膜及びバリアメタル膜を削り取って、配線溝部を埋め込む配線部を形成する。

(もっと読む)

半導体装置

【課題】 コンタクト抵抗の低減化を図る。

【解決手段】 本発明の半導体装置は、半導体基板上に形成された通常耐圧のMOSトランジスタ(A)と、高耐圧MOSトランジスタ(B)とを有し、前記通常耐圧のMOSトランジスタ(A)のソース・ドレイン層42にコンタクト接続されるプラグコンタクト部47の数が、前記高耐圧MOSトランジスタ(B)のソース・ドレイン層30にコンタクト接続されるプラグコンタクト部47の数よりも少ないことを特徴とする。

(もっと読む)

半導体装置の製造方法及び製造装置

【課題】 埋め込み性に優れ、誘電率の小さい絶縁膜を用い、電気的特性の優れた半導体装置の製造方法及び製造装置を提供する。

【解決手段】 真空排気したチャンバ1内に酸素ガス及び塩素ガス18を導入すると共に、プラズマアンテナ27に給電することにより、ガスプラズマ14を発生させた後、主として、ケイ素製の被エッチング部材20を塩素ガスラジカルによりエッチングして前駆体15を生成させ、温度制御手段6の調整により基板3に前駆体15を吸着させてから、塩素ガスラジカルにより前記基板に吸着した前駆体15を還元すると共に酸素ガスラジカルにより酸化してSiO2膜とする反応により、アスペクト比の大きい溝にSiO2膜を埋め込む。

(もっと読む)

合わせ誤差計測マークおよびこれを用いた半導体装置の製造方法

【課題】メタルフォトリソグラフィ工程で正確な位置合わせを行うための合わせ誤差計測マークを提供する。

【解決手段】下地基準マーク110は、層間膜132に下地基準マーク用ホール111を所定密度で形成し、下地基準マーク用ホール111内および層間膜132上にタングステンを堆積し、層間膜132表面のタングステンを化学機械研磨したときのエロージョンで凹みを生じさせることによって形成される。レジスト基準マーク120は、下地基準マーク110上のレジスト膜134に形成され、下地基準マーク110と異なる寸法の矩形枠状に形成される。エロージョンの凹みで下地基準マーク110を形成したので、アルミニウム膜133の凹みのエッジ133a位置と下地基準マーク110のエッジ110a位置とが一致するようになる。したがって、エッジ133aの位置とレジスト基準マーク120の位置とを測定することで、合わせ誤差を正確に検出できる。

(もっと読む)

パターン形成方法および半導体装置の製造方法

【課題】より微細なパターンを容易に形成することが可能なパターン形成方法およびそれを用いた半導体装置の製造方法を提供する。

【解決手段】基板10上に第1レジスト膜12Aと第2レジスト膜12Bを形成し、第1パターン21を有する第1ホトマスク20を用いて第2レジスト膜12Bを露光して、第1パターン21を第2レジスト膜12Bに転写し、パターン12aを形成する。次に第2パターン31を有する第2ホトマスク30を用い、第2パターン31の一部が第2レジスト膜12Bに転写されたパターン12aと重畳するように、第2パターン31を第2レジスト膜12Bと第1パターン21により露出された第1レジスト膜12Aとに転写し、第1パターン21と第2パターン31とが重畳する領域46に第1および第2レジスト膜12B、12Aを貫通する開口パターン11を形成する。

(もっと読む)

金属系膜形成方法及びプログラムを記録した記録媒体

【課題】 結晶構造をコントロールすることによって,従来以上に低い抵抗を有する金属系膜を形成する。

【解決手段】 金属系原料ガスとして例えばWF6ガスを供給するステップと水素化合物ガスとして例えばSiH4ガスを供給するステップとを,不活性ガス例えばArガス,N2ガスを供給するパージステップを介在させて,交互に繰り返し実行することによって,非晶質を含む第1タングステン膜を成膜する第1タングステン膜成膜ステップと,第1タングステン膜上に,上記WF6ガスと還元性ガスとして例えばH2ガスを同時に供給することによって,第2タングステン膜を成膜する第2タングステン膜成膜ステップとを含む。SiH4ガスを供給するステップ後のパージステップの実行時間を変えることにより第1タングステン膜が含む非晶質の割合をコントロールする。

(もっと読む)

第1の配線下部の金属−絶縁膜−金属キャパシタ及びそれの製造方法

【課題】第1の配線下部の金属−絶縁膜−金属キャパシタ及びそれの製造方法を提供する。

【解決手段】集積回路素子の金属−絶縁膜−金属キャパシタは層間絶縁膜110上に形成され、金属間絶縁膜150によって覆われる。金属間絶縁膜150は、金属−絶縁膜−金属キャパシタの第1の電極の上面を露出する少なくとも一つの第1の開口部を備える。第1の開口部は、第1の銅ダマシン配線パターン160aに埋め込まれるが、第1の銅ダマシン配線は、最下部配線層(例、M1配線層)からなったデュアルダマシン配線構造の一部でありうる。第1の銅ダマシン配線パターン160aは、金属間絶縁膜150の上面と平らな上面を備え、金属−絶縁膜−金属キャパシタの第1の電極の上面と接触する底面を備える。これにより、誘電膜130の誘電特性を向上させるための熱処理を工程条件の制約を受けず実施できて高キャパシタンスのMIMキャパシタを実現できる。

(もっと読む)

半導体装置およびその製造方法

【課題】 メモリ部とロジック部とを含む半導体装置において、容量素子の上部の領域において、導電プラグの終端面における段差の発生を抑制する。

【解決手段】 シリコン基板101にメモリ部104とロジック部102とが混載された半導体装置100は、メモリ部104からロジック部102にわたってシリコン基板101上に設けられた絶縁層と、ロジック部102において層間絶縁膜103および層間絶縁膜119に埋設された複数の第二配線接続プラグ109と、メモリ部104において層間絶縁膜103中に埋設された容量素子115と、メモリ部104の容量素子115が設けられた領域よりも上部の領域において層間絶縁膜103および層間絶縁膜119中に埋設されるとともに、容量素子115と絶縁されたダミープラグ121と、を含む。複数の第二配線接続プラグ109およびダミープラグ121は、層間絶縁膜119の上面で終端する。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置のより微細化に適し、しかも低コストである半導体装置の製造方法を提供すること。

【解決手段】本発明は、半導体シリコン基板表面上に形成されたポリシリコン膜からなるゲート電極構造とこれを覆う層間絶縁膜を有する半導体装置の製造方法において、層間絶縁膜形成後、層間絶縁膜を貫いてコンタクトホールを開口させて所望のコンタクト面を露出させる工程、少なくともコンタクトホール側壁部及びコンタクト面上に絶縁膜を堆積させる工程、絶縁膜をエッチバックすることによりコンタクトホール側壁部にサイドウォール状絶縁膜を形成することを特徴とする半導体装置の製造方法を提供する。

(もっと読む)

微小電気機械式装置の作製方法

【課題】微小構造を有するマイクロマシンの量産に際して、微小構造体と微小構造体を制御する半導体素子を同一基板上に形成し、コストを低減する方法を提供する。

【解決手段】マイクロマシンの作製に際して、膜のパターン形成を行うためのマスク材料を用いて犠牲層を形成し、半導体素子を形成する領域におけるマスクの除去と、微小構造体を形成する領域における犠牲層とマスクの除去を同一の工程にて行う。具体的には絶縁性基板上に選択的に犠牲層103を形成し、犠牲層を覆って半導体層104を形成し、半導体層上にマスク105を形成し、マスクを用いて半導体層をエッチングし、マスク及び犠牲層の除去を同時に行う微小電気機械式装置の作製方法を提供する。

(もっと読む)

半導体装置及びその製造方法

【課題】ゲート電極上にシリサイド膜を有し、従来に比べてより一層の高密度化が可能な半導体装置及びその製造方法を提供する。

【解決手段】ゲート電極62及びLDD層63が形成された半導体基板60の上にシリサイドブロックとなるSiN膜64を形成し、このSiN膜64にゲート電極62に通じる開口部を設ける。この開口部を介してゲート電極66の表面をシリサイド化してシリサイド膜66を形成する。次に、SiO2からなる層間絶縁膜67を形成し、フォトリソグラフィ法により層間絶縁膜67の上面からLDD層63に到達するコンタクトホール67hを形成する。そして、このコンタクトホール67hを介してLDD層63に不純物を高濃度に導入して、ソース/ドレイン層63aを形成する。

(もっと読む)

半導体装置、半導体装置の作製方法

【課題】材料の利用効率を向上させ、かつ、作製工程を簡略化して作製可能な半導体装置、表示装置及びその作製技術を提供することを目的とする。また、それらの半導体装置、表示装置を構成する配線等のパターンを、所望の形状で制御性よく形成できる技術を提供することも目的とする。

【解決手段】光触媒物質、又はアミノ基を有する物質を含む組成物を吐出して選択的に光触媒物質、又はアミノ基を有する物質を形成し、光触媒物質、又はアミノ基を有する物質を、めっき触媒物質を含む溶液中に浸漬し、光触媒物質、又はアミノ基を有する物質にめっき触媒物質を吸着又は析出させ、めっき触媒物質を、金属材料を含むめっき液に浸漬し、めっき触媒物質を吸着又は析出させた光触媒物質又はアミノ基を有する物質表面に金属膜を形成し半導体装置を作製し、めっき触媒物質を含む溶液はpHを3以上6以下に調整して用いる。

(もっと読む)

ウェハ貫通相互接続部を形成する方法およびそれから得られる構造体

半導体基板内に導電バイアすなわちウェハ貫通相互接続部を形成する方法、および結果として得られるウェハ貫通相互接続構造体を開示する。本発明の一実施形態では、ウェハ貫通相互接続構造体を形成する方法は、基板の第1の表面に開口を形成する処置と、開口の内部表面に第1の絶縁層または誘電体層を堆積させる処置と、第1の誘電体層の上に導電層を堆積させる処置と、導電材料を覆って開口の内部表面に第2の絶縁層または誘電体層を堆積させる処置と、基板の反対側の第2の表面を貫通して導電層の一部分を露出させる処置とを含む。本発明の方法を用いて生成されたウェハ貫通相互接続部を含む半導体デバイスもまた開示する。 (もっと読む)

半導体装置

【課題】保護素子による過電流保護機能を向上させることが可能な半導体装置を提供する。

【解決手段】I/Oセル14は、パッド2と、それに接続する出力バッファおよび入力バッファ、およびパッド2と同じ配線層を用いて形成された電源配線3と、パッド2と電源配線3との間に接続する保護素子であるクランプダイオード(アノード領域29およびカソード領域31)とを備える。クランプダイオードは、電源配線3により短い距離で接続可能なように、電源配線3の真下あるいはその近傍の領域にレイアウトされる。

(もっと読む)

半導体装置

【課題】 埋込銅配線を有する半導体装置の信頼性を向上させる。

【解決手段】 絶縁膜14,15に配線溝を形成し、その配線溝の底面および側面上を含む絶縁膜15上に導電性バリア膜18と銅の主導体膜19を形成し、CMP法により不要な部分を除去して配線20を形成する。そして、主導体膜19上にタングステンからなる金属キャップ膜22を選択成長させてから、配線20を埋込んだ絶縁膜15上に絶縁膜23〜26を形成し、ビア30が金属キャップ膜22を貫通して主導体膜19を露出するようにビア30及び配線溝31を形成し、ビア30の底部で露出した主導体膜19上にタングステンからなる金属キャップ膜32を選択成長させた後に、ビア30および配線溝31の内部を含む絶縁膜26上に導電性バリア膜33と銅の主導体膜34を形成し、CMP法により不要な部分を除去して配線35を形成する。

(もっと読む)

2,001 - 2,020 / 2,609

[ Back to top ]