Fターム[5F033JJ19]の内容

半導体集積回路装置の内部配線 (234,551) | 層間接続のコンタクト層の材料 (22,060) | 金属及びその合金(シリサイドを除く) (14,566) | 高融点金属 (7,010) | W (2,609)

Fターム[5F033JJ19]に分類される特許

201 - 220 / 2,609

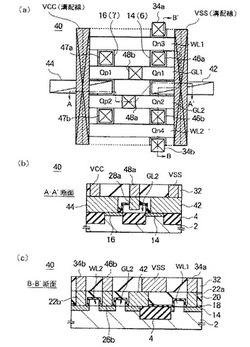

半導体記憶装置

【課題】セル面積増大を抑制しつつゲート形成時のパターンずれによる特性低化を有効に防止し、さらに電源電圧供給線を低抵抗化する。

【解決手段】第1の電源電圧供給線VDDと第2の電源電圧供給線VSSとの間に電気的に直列接続されてゲートが共通に接続された第1導電型の駆動トランジスタQn1,Qn2と第2導電型の負荷トランジスタQp1,Qp2とからそれぞれが構成され、入力と出力が交叉して接続された2つのインバータをメモリセルごとに有する。第1の電源電圧供給線VSSと第2の電源電圧供給線VSSの少なくとも一方が、層間絶縁層の貫通溝内を導電材料で埋め込んだ溝配線からなる。

(もっと読む)

領域分割基板およびそれを用いた半導体装置ならびにそれらの製造方法

【課題】基板を貫通するトレンチによって複数の部分領域に分割されてなる領域分割基板およびそれを用いた半導体装置ならびにそれらの製造方法であって、部分領域の側壁に導電層を形成するメリットだけを享受して、該導電層の形成に伴う悪影響を排除することのできる領域分割基板およびそれを用いた半導体装置ならびにそれらの製造方法を提供する。

【解決手段】基板30の第1表面S1から第2表面S2に亘って、当該基板30を貫通するように形成されたトレンチ31aによって、当該基板30が複数の部分領域Ce,Cea〜Ced,Cek,Celに分割され、前記複数の部分領域のうち、一部の部分領域Cea〜Cedの側壁に、第1表面S1の側から第2表面S2の側に亘って、当該基板30より高い導電率を有する導電層35が形成され、トレンチ31aに絶縁体31bが埋め込まれてなる領域分割基板A20とする。

(もっと読む)

半導体装置

【課題】基板を介したクロストークを抑制でき、放熱性が高い半導体装置を提供する。

【解決手段】実施形態に係る半導体装置1は、半導体基板10を備える。前記半導体基板の内部には空洞11が形成されている。また、前記半導体基板の内部には、前記空洞を前記半導体基板の上面に連通させる連通孔12も形成されている。前記半導体装置は、さらに、前記空洞及び前記連通孔の内面上に設けられた絶縁膜13と、前記空洞及び前記連通孔の内部に埋め込まれ、熱伝導率が前記絶縁膜の熱伝導率よりも高い伝熱部材14と、前記半導体基板における前記空洞の直上域に形成された素子21,22と、を備える。

(もっと読む)

半導体装置

【課題】小型化を実現し得る半導体装置を提供することにある。

【解決手段】半導体基板に形成され、素子分離領域により画定された第1の素子領域12bと、第1の素子領域上に形成された第1のゲート電極21bと、第1のゲート電極の第1の側における第1の素子領域に形成された第1のソース領域32Sと、第1のゲート電極の第2の側における第1の素子領域に形成された第1のドレイン領域32Dとを有する第1のトランジスタ36と、第1のゲート電極の第1の側における素子分離領域上に、第1のゲート電極と並行するように形成された第1のパターン38aと、第1のソース領域に接続された第1の導体プラグ44cとを有し、第1の導体プラグは、接地線及び電源線のうちの一方に電気的に接続されており、第1のパターンは、接地線及び電源線のうちの他方に電気的に接続されている。

(もっと読む)

半導体装置

【課題】配線及びビア間接続の信頼性を向上させた半導体装置を提供する。

【解決手段】実施形態に係る半導体装置は、半導体基板と、前記半導体基板上の異なる高さに配置され、配線が形成された複数の配線層と、前記配線層の積層方向に延びる柱状に形成され、異なる複数の前記配線層の配線間を電気的に接続するビアとを備える。前記配線の一部は、前記ビアの中間部において前記ビアに接触する中間配線であり、所定の前記配線層の中間配線は、前記ビアを前記積層方向に直交する方向で貫通し、且つ、上面、下面及び両側面において前記ビアと接触していることを特徴とする。

(もっと読む)

半導体装置の製造方法

【課題】信頼性の高い半導体装置を高い歩留りで製造し得る半導体装置の製造方法を提供する。

【解決手段】ゲート配線16aを形成するのと同時に形成された位置合わせマーク16fに対して位置合わせして、コンタクトホールの第1の部分パターン61a1をゲート配線の一部と重なり合うようにフォトレジスト膜に露光する工程と、活性領域11bを形成するのと同時に形成された位置合わせマーク11fに対して位置合わせして、コンタクトホールの第2の部分パターン61a2を活性領域の一部と重なり合うようにフォトレジスト膜に露光する工程と、フォトレジスト膜を現像し、第1の部分パターンと第2の部分パターンとが露光された箇所に開口部を形成する工程と、フォトレジスト膜をマスクとして絶縁膜をエッチングし、ゲート配線とソース/ドレイン拡散層20とに達するコンタクトホールを形成する工程とを有している。

(もっと読む)

半導体装置

【課題】nチャネル型電界効果トランジスタとpチャネル型電界効果トランジスタを有する半導体装置において、nチャネル型電界効果トランジスタ、pチャネル型電界効果トランジスタ共にドレイン電流特性に優れた半導体装置を実現する。

【解決手段】nチャネル型電界効果トランジスタ10と、pチャネル型電界効果トランジスタ30とを有する半導体装置において、nチャネル型電界効果トランジスタ10のゲート電極15を覆う応力制御膜19には、膜応力が引張応力側の膜を用いる。pチャネル型電界効果トランジスタ30のゲート電極35を覆う応力制御膜39には、膜応力が、nチャネル型トランジスタ10の応力制御膜19より、圧縮応力側の膜を用いることにより、nチャネル型、pチャネル型トランジスタの両方のドレイン電流の向上が期待できる。このため、全体としての特性を向上させることができる。

(もっと読む)

半導体装置及びその製造方法

【課題】凹形状を有するホールの内壁側面上に側壁保護膜の一部を残留させることにより、ホールの内壁側面を平滑化する。後の工程でホール内に材料を埋設する際にも、ボイドを発生させることなく優れた埋設性でホール内を材料で埋設させる。

【解決手段】半導体基板の裏面上にマスクを設ける工程と、マスクを用いて半導体基板を貫通すると共に凹形状の内壁側面を有するホールであって内壁側面が側壁保護膜で覆われたホールを形成する工程と、側壁保護膜の一部を残留させるようにマスクを除去する工程と、を有する半導体装置の製造方法。

(もっと読む)

半導体装置

【課題】高い耐電圧特性、および耐リーク特性を有する配線構造を備える半導体装置、およびその製造方法を提供する。

【解決手段】本発明の実施の形態による半導体装置は、半導体素子が設けられた半導体基板と、前記半導体基板上に形成された、上下層の導電部材を電気的に接続する接続部材と、前記接続部材と同じ層に形成された第1の絶縁膜と、前記接続部材の上面の一部と接する第1の領域、および前記第1の領域上に位置し、前記第1の領域よりも幅の広い第2の領域を含む配線と、前記第1の絶縁膜上に、前記配線の前記第1の領域の側面の上側から少なくとも一部、および前記第2の領域の底面に接して形成された第2の絶縁膜と、を有する。

(もっと読む)

ナノ物体を外部電気システムに接続する素子、及びその素子を作る方法

【課題】ナノ物体を外部電気システムに接続する素子、及びその素子を作る方法を提供する。

【解決手段】特に分子の特性評価に適用される本発明によると、以下を備える素子が作られる:ナノ物体(2)に接続される上部接触パッド(8)を備えた上部層(16);外部電気システム(4)に接続される下部接触パッド(12)を備えた下部層(18);前記下部層上にあり、前記下部パッドと接触する電気的貫通ビア(22)を備えた接着層(20);前記接着層と前記上部層の間にあり、前記上部パッドを前記下部パッドに接続するための導電ライン(25)及び電気的ビア(26)を備えた少なくとも2つの層(22、24)。

(もっと読む)

半導体集積回路装置用ルテニウムバリア膜とその作製方法及び該ルテニウムバリア膜を有する半導体集積回路装置とその製造方法

【課題】クレバスの面積比が小さく、低抵抗を維持した薄膜の状態で、配線層を構成する銅又はアルミニウム等の拡散を防止できるルテニウムバリア膜とその作製方法及び該ルテニウム膜を有する半導体集積回路装置とその製造方法を提供する。

【解決する手段】ルテニウムバリア膜は、ルテニウムを主成分とする金属からなり、表面上に観測されるクレバス(溝、割れ目又は深く鋭いくぼみ)の占める面積比が、前記バリア膜表面の全面積に対して15%以下であり、広角X線回折測定によって得られるX線回折プロファイルにおいて、ルテニウムの結晶配向面(002)及び(100)に起因するスペクトルのそれぞれのピーク強度比であるRu(002)/Ru(100)が10以上であり、また、スパッタリング法によって、温度を500℃以上に加熱した状態の半導体基板の配線溝上に成膜されることを特徴とする。

(もっと読む)

半導体装置およびその製造方法

【課題】埋め込み絶縁層により活性層と支持基板とが電気的に絶縁された半導体基板において、支持基板の電位を活性層の表面から取り出すための基板コンタクトの低抵抗化を図ることができる半導体装置およびその製造方法を提供すること。

【解決手段】活性層16に素子領域4およびコンタクト領域5が形成された厚膜SOI基板2において、CMOSトランジスタ7のB/L層29およびL/I層37、npnバイポーラトランジスタ8のコレクタ層49と同一層に、n型基板コンタクト12の貫通コンタクト58を取り囲むn型コンタクト埋め込み層57を形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】ゲート電極同士の間の突合わせ部を挟むように形成されたコンタクトプラグ同士が、当該突合わせ部の絶縁膜内に形成されたボイドを介してショートすることを防ぐ。

【解決手段】ゲート電極G2およびG5間の突合わせ部において対向するサイドウォールSW上には、ライナー絶縁膜6と層間絶縁膜7が形成されている。サイドウォールSW同士の間において、サイドウォールSWの側壁にそれぞれ形成されたライナー絶縁膜6を接触させてサイドウォールSW間を閉塞させることにより、層間絶縁膜7とライナー絶縁膜6の内部にボイドが発生することを防ぐ。

(もっと読む)

熱型検出器、熱型検出装置及び電子機器

【課題】 熱型検出素子を基体から熱分離する空洞部の深さを規定するスペーサー部材を配線構造として兼用し、かつ、その配線構造により、確実に熱分離できる空洞部の深さを確保することができる熱型検出器、熱型検出装置及び電子機器を提供すること。

【解決手段】 熱型検出器は、基体100と、基体100より突出するスペーサー部材104と、スペーサー部材104に支持される支持部材210と、支持部材に支持される熱型検出素子220と、基体内に配置されて熱型検出素子と接続される検出回路510,520と、熱型検出素子と検出回路とを接続する配線部と、を有する。配線部は、基体内に配置された少なくとも一層の第1導電層LIA,LIBと、スペーサー部材内に配置された少なくとも一層の第2導電層LIC,LIDと、支持部材に支持された第3導電層214,238と、第1,第2及び第3導電層の隣接層同士を接続する複数のプラグHLA〜HLDとを含む。

(もっと読む)

成膜方法および記憶媒体

【課題】成膜原料としてコバルトカルボニルを用いてCo膜を成膜する場合に、下地との密着性を良好にすることができる成膜方法を提供すること。

【解決手段】処理容器1内に基板Wを配置し、処理容器1内に気体状のコバルトカルボニルを供給し、基板W上でコバルトカルボニルを熱分解させて基板W上にCo膜を成膜するにあたり、基板WのCo膜の下地が、Co膜との界面近傍に混合層を形成する材料で構成されており、基板Wの加熱温度を190〜300℃とする。

(もっと読む)

半導体記憶装置及びその製造方法

【課題】コンタクトとアクティブエリアとの間のショートマージンを確保できる半導体記憶装置及びその製造方法を提供する。

【解決手段】実施形態に係る半導体記憶装置は、半導体基板と、前記半導体基板の上層部分に形成され、前記上層部分を第1方向に延びる複数本のアクティブエリアに区画する複数本の素子分離絶縁体と、前記アクティブエリアに接続されたコンタクトと、を備える。そして、各前記アクティブエリアの上面のうち、前記第1方向における一部の領域には、前記第1方向に対して直交する第2方向において前記アクティブエリアの全体にわたって凹部が形成されている。前記第1方向において、隣り合う前記アクティブエリアにそれぞれ接続された2本の前記コンタクトの位置は相互に異なる。前記コンタクトは前記凹部の側面に接し、底面には接していない。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】本発明は、銅合金配線とビアとの接続面に、窒素を含むバリヤメタル膜が形成されている構造を有する半導体装置であって、銅合金配線とビアとの間における電気抵抗の上昇を抑制することができる半導体装置等を提供する。

【解決手段】本発明に係る半導体装置では、第一の層間絶縁膜内に配設されており、主成分であるCuにAlを添加した第一の銅合金配線と、第一の層間絶縁膜上に形成される第二の層間絶縁膜と、第二の層間絶縁膜内に配設されており、主成分であるCuにAlを添加した第二の銅合金配線とを、備えている。そして、第二の銅合金配線のAlの濃度は、第一の銅合金配線の前記Alの濃度未満である。

(もっと読む)

Cu配線の形成方法およびCu膜の成膜方法、ならびに成膜システム

【課題】微細なトレンチまたはホール等の凹部にボイドを発生させずに確実にCuを埋め込むことができ、かつ低抵抗のCu配線を形成すること。

【解決手段】ウエハWに形成されたトレンチ203を有する層間絶縁膜202において、トレンチ203の表面にバリア膜204を形成する工程と、バリア膜204の上にRu膜205を形成する工程と、Ru膜205の上に、加熱しつつ、PVDによりCuがマイグレーションするようにCu膜206を形成してトレンチ203を埋める工程とを有する。

(もっと読む)

半導体装置

【課題】貫通電極の形成に時間を要さず、貫通電極内でのボイドの発生を抑制できる半導体装置、およびこの半導体装置の製造方法を提供すること。

【解決手段】半導体装置1は、孔111が形成された絶縁性あるいは半導体の層11と、層11の孔111内に設けられた貫通電極12と、を備える。貫通電極12は、シード層121と、めっき層122と、を備える。シード層121は、孔111の底面111Aを覆う。また、シード層121は、孔111の側面111Bのうち、孔111の開口から、孔111の開口と孔111の底面111Aとの間の所定の位置までの第1の領域を未被覆とし、この第1の領域(未被覆領域)111B1を除いた第二の領域を被覆している。めっき層122は、シード層121と、未被覆領域111B1の少なくとも一部を覆う。

(もっと読む)

半導体素子及びその製造方法

【課題】絶縁膜を貫通するコンタクトプラグの抵抗を改善させられる半導体素子及びその製造方法を提供する。

【解決手段】半導体基板上に形成された第1層間絶縁膜と、前記第1層間絶縁膜を貫通して形成されたコンタクトホールと、前記コンタクトホールの内部に形成されたコンタクトプラグと、前記コンタクトホール内で前記コンタクトプラグの上部側壁を部分的に覆うスペーサと、を含む。

(もっと読む)

201 - 220 / 2,609

[ Back to top ]