Fターム[5F033JJ22]の内容

半導体集積回路装置の内部配線 (234,551) | 層間接続のコンタクト層の材料 (22,060) | 金属及びその合金(シリサイドを除く) (14,566) | 高融点金属 (7,010) | 高融点金属の合金 (308)

Fターム[5F033JJ22]の下位に属するFターム

TiW (270)

Fターム[5F033JJ22]に分類される特許

21 - 38 / 38

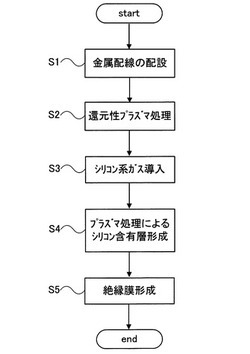

半導体装置の製造方法

【課題】半導体装置の信頼性及び生産性を向上させる。

【解決手段】本発明では、半導体基板上に形成させた第1の絶縁膜内に金属配線を配設し、配設した金属配線の表面に第1のプラズマ処理を施し、第1のプラズマ処理を施した金属配線の表面にシリコン系ガスを晒し、シリコン系ガスを晒した金属配線の表面に第2のプラズマ処理を施し、金属配線上にシリコン含有層を形成し、シリコン含有層上に第2の絶縁膜を形成するようにした。これにより、半導体装置の微細化に伴うエレクトロマイグレーションが抑制されると共に、ストレスマイグレーションが充分抑制され、半導体装置の電気的信頼性が向上し、生産性の高い半導体装置の製造方法が実現する。

(もっと読む)

半導体素子及びその形成方法、半導体クラスタ装備

【課題】電気的な特性が向上される半導体素子の形成方法を提供する。

【解決手段】この方法は、導電パターン105を有する半導体基板100の上に絶縁膜110を形成する。絶縁膜をパターニングして導電パターンの一部を露出する開口部115を形成し、開口部の内壁及び絶縁膜の上部面に予備拡散防止膜120を形成する。予備拡散防止膜に酸素原子等を供給して第1拡散防止膜120aを形成する。第1拡散防止膜により囲まれている開口部を埋める金属膜152を形成する。この方法により製造された半導体素子及び半導体素子の製造に利用する半導体クラスタ装備を提供する。

(もっと読む)

薄膜トランジスタ及びその製造方法

【課題】ソース/ドレイン電極用金属膜による基板のストレスを減少させて素子の製造歩留まりを向上させる。

【解決手段】基板と、前記基板上に位置し、ソース/ドレイン領域及びチャネル領域を有する半導体層と、前記半導体層を含む基板上に位置するゲート絶縁膜と、前記半導体層のチャネル領域に対応するように、前記ゲート絶縁膜上に位置するゲート電極と、前記ゲート電極を含む基板上に位置し、前記半導体層のソース/ドレイン領域に連結されるコンタクトホールを有する層間絶縁膜と、前記コンタクトホールを介してソース/ドレイン領域に連結されるソース/ドレイン電極と、を備え、前記ソース/ドレイン電極は、第1金属膜、第2金属膜及びこれら間に介在された金属酸化膜を有する。

(もっと読む)

画像表示装置とその製造方法

【課題】イオン注入とホトリソグラフィーの工程数を削減できる構造をもつ薄膜トランジスタとすることで、製造にかかる時間を短縮した画像表示装置を提供する。

【解決手段】ゲート電極GTを薄い下層金属GMBと上層金属GMTの積層構造とし、保持容量Cst部分の上層電極を下層金属GMBのみとする。そして、保持容量Cstの下部電極用インプラを、薄い下層金属GMBを通過させて、ソース・ドレインのインプラと同時に行う。PMOSTFTのゲート電極も下層金属GMBのみとし、ソース・ドレインのインプラと閾値調整インプラを同じレジストを利用して行う。薄膜トランジスタと保持容量をこのような構造としたことで、ホト工程とイオン注入工程が各々1工程削減でき、より短時間で、より廉価に画像表示装置のためのアクティブ・マトリクス基板が得られる。

(もっと読む)

バリヤ層、この形成方法及びプラズマ成膜装置

【課題】 Ti合金を用いることにより被処理体の表面の凹部におけるコーナエッチング耐性を向上させることができるバリヤ層を提供する。

【解決手段】被処理体2の表面に絶縁層6と導電層12とを形成する際に前記絶縁層と前記導電層との間に介在されるバリヤ層10において、このバリヤ層は、Ti(チタン)金属よりなる母材に、遷移金属群より選択された1又は2以上の金属を混合してなるTi合金膜88を含むように構成する。これにより、被処理体の表面の凹部におけるコーナエッチング耐性を向上させる。

(もっと読む)

配線構造と配線形成方法及び薄膜トランジスタ基板とその製造方法

【課題】本発明は、接着力が改善されて、良好な側面プロファイルを有する銅配線構造を提供する。本発明はまた、前記構造を有する配線形成方法を提供する。本発明はさらに、前記配線構造を含む薄膜トランジスタ基板を提供する。本発明はさらに、前記したような薄膜トランジスタ基板の製造方法を提供する。

【解決手段】配線構造と配線形成方法及び薄膜トランジスタ基板とその製造方法が提供される。配線構造は下部構造物上に形成された銅窒化物を含むバリヤ膜及びバリヤ膜上に形成された銅または銅合金を含む銅導電膜を含む。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】配線材とバリアメタル層の密着性を向上させる。

【解決手段】第1の基板温度で、表面に凹部が形成された層間絶縁膜中及びその表面の酸

化種を放出させ、その後、前記第1の基板温度より低い第2の基板温度で、前記層間絶縁

膜の少なくとも一部と接触するようにして、Ti及びNを含み、酸素(O)及び貴金属成分を除く全成分におけるTi含有量が50at%を超える層を形成する。次いで、前記層上にCu金属層を形成して半導体装置を製造する。

(もっと読む)

半導体装置とその製造方法

【課題】コスト増を招くことなく高いインダクタンス値を得る。

【解決手段】半導体基板10にインダクタ素子40が形成される。粉末状の磁性体が分散された樹脂材で形成され、インダクタ素子40を覆う磁性樹脂体30、66を備える。また、巻き線41における配線間の隙間を埋めるように、透磁率の低い材料として非磁性の樹脂層42が製膜されている。樹脂剤42は磁性樹脂層30を形成する材料の中、磁性体が添加されない樹脂で形成される。

(もっと読む)

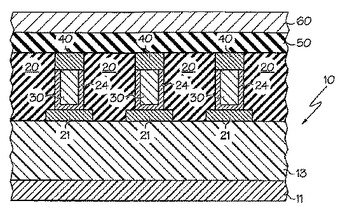

半導体装置およびその製造方法

【課題】写真製版におけるフォトマスクの重ね合わせズレが生じた場合にもエアギャップと上層配線層のビアホールとが接続することを防止できる半導体装置およびその製造方法を提供する。

【解決手段】絶縁層2、3は下地層1上に形成されている。絶縁層4は絶縁層2、3上に形成されている。複数の下層配線用導電層5のそれぞれは、絶縁層4を貫通して絶縁層3に達する配線用溝3c内に形成されている。隣り合う下層配線用導電層5の間にエアギャップ8dが形成されており、エアギャップ8dと下層配線用導電層5との間に絶縁層4が配置されている。

(もっと読む)

フラットパネルディスプレイ装置及びその製造方法

【課題】低い配線抵抗,熱的安定性を有し,画素電極との接触抵抗特性が改善されたフラットパネルディスプレイ装置及びその製造方法を提供する。

【解決手段】フラットパネルディスプレイ装置は、基板100と,該基板100上に順次積層された耐熱性金属膜パターン131a,アルミニウム系金属膜パターン131c,およびキャッピング金属膜パターン131dを備えるソース/ドレイン電極131と,を含み,耐熱性金属膜パターン131aは,500Å以下の厚さを有し,耐熱性金属膜パターン131aとアルミニウム系金属膜パターン131cとの間には,拡散防止膜パターン131bがさらに含まれる

(もっと読む)

半導体装置の製造方法

【課題】下層配線のスパッタエッチングにより、接続孔の側壁に付着する導電性粒子に起因する不具合を防止するとともに、埋め込み特性および導通特性の悪化を防止する半導体装置の製造方法を提供する。

【解決手段】まず、基板上に設けられた層間絶縁膜7に、配線溝8aと接続孔8bとからなるデュアルダマシン開口部8を形成する工程を行う。次に、下層配線5を露出させるように、デュアルダマシン開口部8の内壁を覆う状態で、犠牲膜21を形成するとともに、下層配線5のスパッタエッチングを行う。次いで、犠牲膜21の少なくとも表面側を、下層配線5に対して選択的に除去する。その後、デュアルダマシン開口部8に、導電膜を埋め込んで、配線溝8aと接続孔8bとに上層配線とヴィアとをそれぞれ形成する工程を行うことを特徴とする半導体装置の製造方法である。

(もっと読む)

半導体接合部に薄膜物質を選択的に堆積させる方法

本発明の実施形態は、基板上に形成されたデバイスに高品質コンタクトレベル接続部を形成するプロセスを提供する。一実施形態において、基板上に物質を堆積させるための方法であって、基板を酸化物エッチング緩衝液にさらして、前処理プロセスで水素化シリコン層を形成するステップと、基板上に金属シリサイド層を堆積させるステップと、金属シリサイド層上に第一金属層(例えば、タングステン)を堆積させるステップと、を含む前記方法が提供される。酸化物エッチング緩衝液は、フッ化水素とアルカノールアミン化合物、例えば、エタノールアミン、ジエタノールアミン、又はトリエタノールを含有することができる。金属シリサイド層は、コバルド、ニッケル、又はタングステンを含有することができ、無電解堆積プロセスによって堆積させることができる。一例において、基板は、溶媒と金属錯体化合物を含有する無電解堆積溶液にさらされる。 (もっと読む)

相変化メモリ装置および相変化メモリ装置の製造方法

【課題】相変化メモリ装置における良好な電気特性と良好な熱特性を両立させ、電極や配線の材料選択の自由度も高めて、大規模な相変化メモリ装置の量産を可能とすること。

【解決手段】ヒータ電極110と相変化層114の接触界面112の近傍で発生するジュール熱が、ヒータ電極110を介して下方に伝達され、下地の良導電性の金属コンタクトプラグから放熱されることを抑制するために、異種材料コンタクトプラグ104(106,108)を採用する。ヒータ電極110に接触する第1の導電材料プラグ106は、ヒータ電極110の構成材料と同種または同じ金属材料からなり、第2の導電材料プラグ108は、接地電位用プラグ100や接地配線102と同種あるいは同じ金属材料からなる。両プラグ106,108は、共通のコンタクトホール内に積層形成される。

(もっと読む)

電子基板の製造方法及び電気光学装置の製造方法並びに電子機器の製造方法

【課題】製造コストを抑えつつ、高精度の電子素子を形成できる電子基板の製造方法および電気工学装置の製造方法並びに電子機器の製造方法を提供する。

【解決手段】配線パターンを有する基板Pに対してマスク22を貼着する工程と、マスク22の開口部22aを介して配線パターンの一部を除去して抵抗素子を形成する工程とを備える。マスク22は、基板Pに貼着される第1フィルム材22Aと、第1フィルム材22Aに剥離可能に貼り合わされる第2フィルム材22Bとを有する。マスク22の所定領域に開口部22aを形成し、開口部22aが形成されたマスク22を負圧環境下で基板Pに貼着する。

(もっと読む)

半導体装置およびその製造方法

【課題】薄膜トランジスタの静電破壊を抑制することができ、信頼性を高めた半導体装置およびその製造方法を提供する。

【解決手段】複数の薄膜トランジスタ100により回路が形成された半導体装置であって、複数の薄膜トランジスタ100に共通接続されたゲート配線22が分割されており、分割されたゲート配線22同士が、ゲート配線22よりも上層に配置された接続配線29により電気的に接続されている。

(もっと読む)

1ないし5nmの厚さの金属キャップを用いる改良されたオンチップCu相互接続

【課題】 1から5nmの厚さの金属キャップを用いた改良されたオンチップCu相互接続を提供する。

【解決手段】 開示されているのは、層間の誘電体又は誘電体拡散障壁層の堆積に先立って、1から5nmの厚さの元素でCuダマシン配線の表面をコーティングする手順である。そのコーティングは、酸化に対する防御をもたらし、Cuと誘電体の間の密着力を増し、そしてCuの界面拡散を減少させる。さらに、その薄いキャップ層はCuのエレクトロマイグレーション寿命を増し、応力により誘起されたボイド発生を減らす。選択された元素は、Cu配線間のショートを引き起こすことなしに、下層の誘電体中に埋込まれたCuの上に直接堆積することができる。これらの選ばれた元素は、酸素及び水に関する負の高い還元電位と、Cuへの低い溶解度、及びCuとの化合物形成に基づいて選ばれている。

(もっと読む)

カルコゲニド型メモリ・デバイスのための金属キャップの無電解メッキ

カルコゲニド型メモリ・デバイスにおいて導電性相互接続部の上側に金属キャップを形成する方法が提供され、該方法は、基板10の上側に第1導電性材料の層21を形成する工程と、基板及び第1導電性材料の上側に絶縁層20を堆積させる工程と、絶縁層に開口22を形成して、第1導電性材料の少なくとも一部分を露出させる工程と、絶縁層の上側に且つ開口内に第2導電性材料30を堆積させる工程と、第2導電性材料を部分的に除去して開口内に導電性区域を形成する工程と、開口内の導電性区域を絶縁層の上面よりも低い高さまで凹ます工程と、開口内の凹まされた導電性区域の上側に第3導電性材料のキャップ40を形成する工程と、キャップの上側にカルコゲニド型メモリ・セル材料のスタックを堆積させる工程と、カルコゲニド型メモリ・セル材料のスタックの上側に導電性材料を堆積させる工程とを備え、第3導電性材料は、コバルト、銀、金、銅、ニッケル、パラジウム、白金、及びそれらの合金の群の中から選択される。  (もっと読む)

(もっと読む)

半導体装置及びその製造方法

【課題】 機械的強度に優れると共に、低抵抗であって且つ絶縁膜に対する密着性の高いバリアメタル膜を有する半導体装置を提供する。

【解決手段】 基板(1)上に形成された絶縁膜(6)と、絶縁膜(6)中に形成された埋め込み金属配線(10)と、絶縁膜(6)と金属配線(10)との間に形成されたバリアメタル膜(A1)とを備えた半導体装置において、バリアメタル膜(A1)は、絶縁膜(6)が存在している側から金属配線(10)が存在している側へ向かって順に積層されている金属酸化物膜(7)、金属化合物膜(8)及び金属膜(9)よりなる。金属化合物膜(8)の弾性率は、金属酸化物膜(7)の弾性率よりも大きい。

(もっと読む)

21 - 38 / 38

[ Back to top ]