Fターム[5F033JJ22]の内容

半導体集積回路装置の内部配線 (234,551) | 層間接続のコンタクト層の材料 (22,060) | 金属及びその合金(シリサイドを除く) (14,566) | 高融点金属 (7,010) | 高融点金属の合金 (308)

Fターム[5F033JJ22]の下位に属するFターム

TiW (270)

Fターム[5F033JJ22]に分類される特許

1 - 20 / 38

半導体装置及び半導体装置の作製方法

【課題】微細化されたトランジスタのオン特性を向上させる。微細化されたトランジスタを歩留まりよく作製する。

【解決手段】一対の低抵抗領域及び該低抵抗領域に挟まれるチャネル形成領域を含む酸化物半導体層と、ゲート絶縁層を介してチャネル形成領域と重畳する第1のゲート電極層と、第1のゲート電極層のチャネル長方向の側面及びゲート絶縁層の上面と接し、一対の低抵抗領域と重畳する一対の第2のゲート電極層と、第2のゲート電極層上の、側端部を第2のゲート電極層の側端部と重畳する一対の側壁絶縁層と、を有する半導体装置を提供する。

(もっと読む)

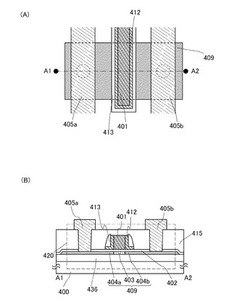

コア付きインダクタ素子およびその製造方法

【課題】半導体基板上に形成するインダクタのインダクタンスを大きくすること。

【解決手段】半導体基板上に形成された少なくとも1層からなるコイル配線のコイル中央孔に別基板に形成されたコアを挿入する。コアをコイル中央孔に固定した後、別基板は分離する。コアは別基板に接合材を介してコア材(磁性体)の薄板を付着させて、パターニングする。半導体基板上に形成されたコイル中央孔は流動性接着剤が入っていて、コアを挿入した後に流動性接着剤が硬化してコアが固定される。コアが固定された後に接合剤の接着力を低下させて別基板を分離する。コア材はバルクと同じ高透磁率を有するので、非常に大きなインダクタンスを持つインダクタを形成できる。

(もっと読む)

回路基板及び表示装置

【課題】 配線の特性の劣化を生じさせることなく、額縁面積を削減することが可能な回路基板、及び、該回路基板を備える表示装置を提供することを目的とする。

【解決手段】 支持基板上にトランジスタ及び外部接続端子が載置されたトランジスタ基板と、該トランジスタ基板上に取り付けられた外付け部材とを含んで構成される回路基板であって、上記外付け部材は、導電部材を介して外部接続端子と電気的かつ物理的に接続されており、上記トランジスタは、外部接続端子と横並びに配置されている回路基板である。

(もっと読む)

配線構造物及びその製造方法

【課題】短時間で、配線母体の内部に、種々のトポロジーの貫通配線や連結配線を埋め込むことが可能な配線構造物を提供する。

【解決手段】配線母体11と、配線母体11の内部に設けられた複数の穴部の内部にそれぞれ配置された、配線子連続体(Qi1,Qi2,Qi3,……,Qin-1,Qin;Qi+11,Qi+12,Qi+13,……,Qi+1n-1,Qi+1n)からなる複数の貫通配線部とを備える。複数の配線子連続体のそれぞれをなす複数の配線子Qi1,Qi2,Qi3,……,Qin-1,Qin;Qi+11,Qi+12,Qi+13,……,Qi+1n-1,Qi+1nのそれぞれは、コア部と、コア部を被覆し、コア部より融点の低い導電体からなるシェル部Qi,shell,Qi+1,shellを有する。複数の配線子は、それぞれのシェル部を互いに溶融することにより金属学的に接合される。

(もっと読む)

導電性バリア膜形成材料、導電性バリア膜形成方法、及び配線膜形成方法

【課題】溝や穴の開口部と深さとの比(開口部/深さ)が1/5〜1/7のような条件を要求されても、又、厚さが10nm以下であっても成膜が可能で、かつ、銅の拡散防止(バリア性)に優れ、更には電気抵抗が小さく、銅膜との密着性にも優れた導電性バリア膜形成材料を提供する。

【解決手段】ケミカルベーパーデポジションにより銅膜の下地膜として導電性Ta−Zr系バリア膜を形成する為の材料であって、Taを持つ金属有機化合物と、Zrを持つ金属有機化合物とを含むことを特徴とする導電性バリア膜形成材料、および、前記Ta有機化合物、前記Zr有機化合物の一方または双方を溶解する溶媒とを含むことを特徴とする導電性バリア膜形成材料。

(もっと読む)

半導体基板と半導体基板の製造方法および半導体パッケージ

【課題】高信頼性の貫通電極を有する半導体基板と半導体基板の製造方法を提供することを目的とする。

【解決手段】第1絶縁層(2)を介して第1配線層(3)が形成され、貫通孔(4)の内周に第2配線層(5)を形成し、貫通孔(4)は、第1の開口部(4a)と、第1の開口部(4a)よりも開口面積が小さい第2の開口部(4b)で形成され、第2の開口部(4b)に第3配線層(103a)を形成するとともに、第3配線層(103a)を第1の開口部(4a)よりも先に形成することを特徴とする。

(もっと読む)

スルーシリコンビア(TSV)内にチップ−チップ間、チップ−ウェハー間及びウェハー−ウェハー間の銅インターコネクトを電着するプロセス

シリコン基板内のビア内に高純度の銅を電着し、スルーシリコンビア(TSV)を形成するプロセスである。本プロセスは、電解銅めっきシステム内の電解槽内にシリコン基板を浸漬するステップと、高純度の銅を電着してTSVを形成するのに十分な時間の間、電圧を印加するステップとを含み、電解槽が酸、銅イオンの発生源、第一鉄イオン及び/又は第二鉄イオンの発生源、及び析出した銅の物理−機械的特性を制御するための少なくとも1つの添加剤とを含み、銅金属の発生源からの銅イオンを溶解することによって電着されることになる付加的な銅イオンを提供するために、前記槽内でFe2+/Fe3+レドックス系が、確立される。 (もっと読む)

半導体装置、半導体装置の製造方法

【課題】微細配線であっても、Cu配線の配線抵抗上昇の低減と信頼性向上とを両立する。

【解決手段】半導体装置は、絶縁膜2と、絶縁膜2に形成された溝5と、溝5の側壁及び底面に形成された、チタン(Ti)とタンタル(Ta)との合金からなるバリアメタル膜3と、バリアメタル膜3に積層され、溝5の中に位置する銅(Cu)配線4と、を有する。バリアメタル膜3のチタン濃度は、0.1at%以上14at%以下である。

(もっと読む)

表示装置及びその製造方法

【課題】CVD装置への出し入れ回数を減らした表示装置の製造方法および表示装置を提供すること。

【解決手段】本発明にかかる表示装置の製造方法は、絶縁基板上に第1の電極膜と第2の電極膜とを含む導電層、第1の絶縁層、半導体膜、第2の絶縁層および保護層を形成する工程と、半導体膜の上方の第1の領域に配置される所定の厚さの第1のレジスト膜と、第2の電極膜の上方の第2の領域に配置される開口部と、それら以外の領域に配置される厚い第2のレジスト膜と、を保護層上に形成する工程と、第2の領域下をエッチングする工程と、第1のレジスト膜をアッシングにより除去する工程と、第1の領域下に半導体膜に達する第1の孔を形成し、かつ第2の領域下に第2の電極膜に達する第2の孔を形成する工程と、第2のレジスト膜を除去する工程と、半導体膜および第2の電極膜と接続される配線を形成する工程と、を含む。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】配線材との密着性が良く、バリア性の高い金属膜をもつ半導体装置、およびその製造方法を提供する。

【解決手段】基板上に絶縁膜、金属からなるバリアメタル膜、及びCu配線金属膜がこの順で積層された積層構造を具備してなり、バリアメタル膜の酸化物のX線回折測定による回折強度が、バリアメタル膜とCu配線金属膜との化合物の回折強度の10倍以下である。

(もっと読む)

電子装置及びその製造方法

【課題】絶縁膜とCuを含む配線との間に介在する下地膜であって、特に酸素のバリア性が高い下地膜を含む電子装置を提供する。

【解決手段】電子装置は、凹部の形成された絶縁膜と、凹部内に形成され、Cuを含む配線層と、絶縁膜と前記配線層との間に形成され、Ta及びMnを含む下地膜とを有する。

(もっと読む)

半導体装置及びその製造方法

【課題】微小ビアでの接続信頼性を確保した信頼性の高い半導体装置を提供すること。

【解決手段】半導体基板11と、半導体基板11上に配されるとともに、少なくとも1以上の第1配線層、少なくとも1以上の第1絶縁層、及び第1ビアを有する第1配線構造体12と、第1配線構造体12上に配されるとともに、少なくとも1以上の第2配線層15、少なくとも1以上の第2絶縁層14、第2ビア16、及び第3ビア19を有する第2配線構造体17と、第2配線構造体17上に設けられた外部端子18と、を備える半導体装置において、第2配線構造体17の第2配線層15と外部端子18に接合される第2ビア16は、外部端子18側の端部に接合界面16aが配されている。

(もっと読む)

パターン形成方法及びそれを利用した表示装置の製造方法

【課題】

互いにパターン(平面形状)の異なる2種類以上の薄膜を積層した積層構造を形成する工程にて、1回のフォトリソグラフィ工程で夫々の薄膜形状を画定すること。

【解決手段】

基板1上に2層の薄膜3,2を順次成膜し、次に薄膜2の上面に形成された第1マスクパターン4を用いて薄膜2のエッチングを行い、第1の薄膜パターン6を形成する。その後、第1マスクパターン4を残した状態で第1マスクパターン4及び薄膜2の上に、有機材料のオフセット印刷、インクジェット印刷、又はディスペンサノズルによる追加塗布で第2マスクパターン5を形成する。最後に、薄膜3を第1マスクパターン4及び第2マスクパターン5を用いて第2の薄膜パターン7に成形し、続いて2つのマスクパターン4,5を除去する。以上の工程により、フォトリソグラフィが第1マスクパターン4を形成する1回のみに制限されるも、基板1の主面に所望の積層構造が形成される。

(もっと読む)

表示装置の製造方法

【課題】フォト工程の低減を図った表示装置の製造方法。

【解決手段】第1導電型TFTと第2導電型TFTの各形成領域に、半導体層、第1絶縁膜、ゲート電極が形成され、前記半導体層のチャネル領域の各外側に第1導電型不純物領域が形成されている基板上に第2絶縁膜を形成し、前記第1導電型TFTの形成領域において当該ゲート電極を露出させることなく、前記第2導電型TFTの形成領域において当該ゲート電極のうち半導体層と交差する各辺の一部を露出させるようにして、ドレインおよびソースの各電極の接続用のコンタクトホールを形成し、多層導電層によって、前記第1導電型TFTの形成領域における前記各コンタクトホール、前記第2導電型TFTの形成領域において前記各コンタクトホールのゲート電極の一部を被うようにして、ドレインおよびソースの各電極を形成し、第2導電型不純物をドープして、半導体層に第2導電型不純物領域を形成する。

(もっと読む)

層間導電性コンタクトを含む半導体素子及びその形成方法

【課題】半導体素子及びその形成方法を提供する。

【解決手段】半導体素子は、半導体素子の下部コンタクト領域(underlying contact region)上に配置され、上部面を有する第1層間絶縁膜と、前記第1層間絶縁膜を貫通する第1開口部110a、110b内に配置され、第1幅W1aの上部を有する第1導電パターン113a、113bと、第1導電パターン113a、113bの上部面と接触され、第1幅W1aより狭い第2幅W2aの下部を有する第2導電パターン125a、125bと、を含み、第1導電パターン113a、113bの上部面は、前記第1層間絶縁膜の上部面に対して相対的にリセスされて、第1導電パターン113a、113bの上部面の前記下部コンタクト領域に相対的な高さは、前記第1層間絶縁膜の上部面の前記下部コンタクト領域に相対的な高さより低い。第2導電パターン125a、125bが第1導電パターン113a、113bの上部面と接続される。第2導電パターンの下部は、第1幅より狭い第2幅を有する。

(もっと読む)

半導体装置の製造方法

【課題】微細かつ高精度なパターンを含む半導体装置を高い生産効率で製造することができる半導体装置の製造方法を提供する。

【解決手段】露光装置Aを用いて所定の寸法精度内に転写可能なマスクAを準備し(s1)、マスクAでの転写パターンにおいて、所定の寸法精度内に転写すべき複数のクリティカルパターン部を選定し、各クリティカルパターン部の近傍領域に関する開口率をそれぞれ算出する(s2)。複数のクリティカルパターン部のうち、開口率が最大となるクリティカルパターン部αおよび開口率が最小となるクリティカルパターン部βをそれぞれ特定する(s3,s4)。露光装置Bを用いてマスクAを転写した場合、クリティカルパターン部α,βの各寸法が所定の許容範囲に収まるかを評価し(s5)、各寸法が所定の許容範囲に収まる場合、露光装置BとマスクAの組合せにより露光を実施する(s6)。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】配線信頼性が向上される。

【解決手段】半導体基板上に配線層11と層間絶縁膜12とが順に形成され、層間絶縁膜12にトレンチ溝13とトレンチ溝13中に配線層11に達するビア孔14とが形成され、トレンチ溝13とビア孔14と層間絶縁膜12との表面に金属膜15が成膜され、スパッタ法を用いて、ビア孔14の底部の金属膜15をエッチングするとともに、全面に金属膜16が成膜されて、さらに、ビア孔14の側壁にそれぞれの金属によって新たな金属膜が生成され、ビア孔14とトレンチ溝13とを導電性材料17aで埋め込んだ配線層が形成されるようになる。

(もっと読む)

薄膜トランジスタアレイ基板、その製造方法、及び表示装置

【課題】蓄積容量素子の占有面積を小さくすることが可能な薄膜トランジスタアレイ基板、その製造方法、及び表示装置を提供すること

【解決手段】本発明にかかる薄膜トランジスタアレイ基板は、基板1上に形成され、ソース/ドレイン領域を有する半導体層3と、ゲート絶縁膜4と、ゲート電極5と、層間絶縁膜6aと、ソース/ドレイン領域に接続する配線電極71、72と、保護膜8と、配線電極72に接続する画素電極9と、半導体層3より延在して形成された下部容量電極3aと、ゲート電極5と同じ層によって形成され、ゲート絶縁膜4を介して下部容量電極3aの対面に配置された共通配線電極5aと、層間絶縁膜6aより膜厚の薄い誘電体膜(保護膜8)を介して共通配線電極5aの対面に配置された上部容量電極9aと、を備えるものである。

(もっと読む)

電子デバイス及びその製造方法

【課題】カーボンナノチューブを用いた配線構造を備える電子デバイスの製造方法について、炭素元素円筒型構造体からなるビアを歩留まり良く形成すること。

【解決手段】基板1上の第1絶縁膜2上に導電パターン5を形成する工程と、第1絶縁膜2と導電パターン5を覆う第2絶縁膜7を形成する工程と、第2絶縁膜7のうち導電パターン5の上にホール7aを形成する工程と、少なくともホール7a内の底面と第2絶縁膜7の上面に金属膜9を形成する工程と、金属膜9の表面に触媒粒子又は触媒膜からなる触媒面10を形成する工程と、触媒面10から炭素元素円筒型構造体11の束を成長する工程と、炭素元素円筒型構造体の束10の間隙に埋込膜12を形成する工程と、炭素元素円筒型構造体の束11及び埋込膜12及び金属膜9を研磨して第2絶縁膜7の上面から除去するとともに、埋込膜12及び炭素元素円筒型構造体の束11をホール7a内に残してビア13を形成する工程とを含む。

(もっと読む)

半導体装置

【課題】金属抵抗素子の形成位置を画定するための写真製版技術における露光時にレジスト膜中に定在波が発生するのを防止して金属抵抗素子の寸法バラツキを低減する。

【解決手段】金属抵抗素子27の下地絶縁膜23は、金属抵抗素子27の長手方向において、金属抵抗素子27の接続孔25,25間における上面の40%以上の部分を占める上側に凸の1つの曲面を備えている。金属抵抗素子27はその長手方向において下地絶縁膜23の曲面に起因して、コンタクト、コンタクト間における上面及び下面の40%以上の部分を占める上側に凸の1つの曲面を備えている。金属抵抗素子27の形成位置を画定するための写真製版技術における露光時に、金属抵抗素子27を形成するための金属膜の上面及び下面で露光光の反射光は上記曲面により散乱されるので、反射光と入射光によるレジスト膜中での定在波の発生が防止される。

(もっと読む)

1 - 20 / 38

[ Back to top ]