Fターム[5F033JJ23]の内容

半導体集積回路装置の内部配線 (234,551) | 層間接続のコンタクト層の材料 (22,060) | 金属及びその合金(シリサイドを除く) (14,566) | 高融点金属 (7,010) | 高融点金属の合金 (308) | TiW (270)

Fターム[5F033JJ23]に分類される特許

1 - 20 / 270

銅を含む電極連結構造体

半導体集積回路装置

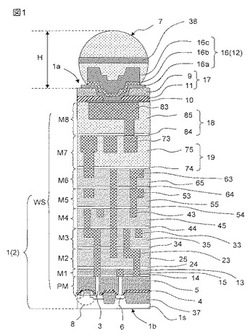

【課題】チップあたりの端子数の増大に伴って、フリップチップ実装が種々の形態で実施されている。しかし、バンプピッチの微細化およびバンプの鉛フリー化によって、エレクトロマイグレーション耐性の確保がますます重要となっている。

【解決手段】本願の発明は、フリップチップ型の半導体集積回路装置において、チップの第1の主面上に形成された多数のUBMパッド状の各々に設けられた半田バンプの中間部には、上下を分割する前記半田バンプとは異なる材質の金属隔壁が設けられているものである。

(もっと読む)

半導体装置の製造方法、半導体装置及び電子機器

【課題】半導体装置に含まれる貫通孔を微細化した場合であっても、メッキで貫通孔の内部に貫通電極を形成する。

【解決手段】半導体装置100の製造方法は、基板10の表面10a側にシード層30を形成するシード層形成工程と、シード層形成工程後、シード層30上に配線層40を形成する配線層形成工程と、配線層形成工程後、基板10の裏面10bからシード層30に達する貫通孔10cを形成する貫通孔形成工程と、貫通孔形成工程後、貫通孔10c内にメッキで貫通電極60を形成する貫通電極形成工程と、貫通電極形成工程後、シード層30を複数に分断する分断工程とを含んでいる。

(もっと読む)

ウェハ裏面のキャパシタを有する半導体デバイスを形成する方法

【課題】 ウェハ裏面のキャパシタを有する半導体デバイスの形成方法を提供する。

【解決手段】 本発明の方法は、その前面の活性シリコン層とその裏面のバルク・シリコン層との間に挿入された埋込み絶縁層を有する、SOI基板を準備するステップと、SOI基板の前面から埋込み絶縁層を貫通して延びる埋込みコンタクト・プラグを含む集積回路を、SOI基板の前記前面に形成するステップと、裏面エッチング・プロセスを実施してバルク・シリコン層内にトレンチを形成し、埋込みコンタクト・プラグの端部を埋込み絶縁層の裏表面に露出させるステップと、第1キャパシタ・プレートと、第2キャパシタ・プレートと、該第1及び第2キャパシタ・プレートの間に挿入されたキャパシタ誘電体層とを含むキャパシタをトレンチ内に形成するステップとを含み、第1キャパシタ・プレートは、埋込みコンタクト・プラグの露出した端部に接触するように形成される。

(もっと読む)

半導体ウエハ及び半導体装置並びに半導体装置の製造方法

【課題】ダイシング工程におけるチッピング不良を低減させる。

【解決手段】一面側に複数の回路素子3が形成され、この回路素子が形成された領域間に第一スクライブライン領域R1が設けられたウエハ状の半導体基板2と、この半導体基板の他面2bから半導体基板の一面2aまで貫通する貫通孔7と、この貫通孔の内面及び半導体基板の他面側に形成された絶縁膜5と、この絶縁膜上に形成された配線6とを備えた半導体ウエハにおいて、半導体基板の他面側に形成された絶縁膜に、第一スクライブライン領域に沿って絶縁膜が離間した領域である第二スクライブライン領域R2が設けられている半導体ウエハを提供する。

(もっと読む)

3DIC方法および装置

【解決手段】 切り分けられたダイまたはウェハのような素子を3次元的に集積する方法および切り分けられたダイまたはウェハのような素子が接続された集積構造。ダイまたはウェハの一方または両方は、その中に形成された半導体デバイスを有する。第1コンタクト構造を有する第1素子は、第2コンタクト構造を有する第2素子に接着される。第1、第2コンタクト構造は、接着の際に露出されることが可能で、また接着の結果、電気的に接続される。接着後にビアがエッチングされるとともに埋め込まれて電気的配線を露出および形成して第1、第2コンタクト構造を接続するとともに、この電気的配線への表面からの電気的なアクセスが可能になる。または、第1、第2コンタクト構造は接着の際に露出されず、接着後にビアがエッチングおよび埋め込みされて第1、第2コンタクト構造が電気的に接続されるとともに接続された第1、第2コンタクト構造への電気的なアクセスが得られる。 (もっと読む)

貫通配線基板および貫通配線基板の製造方法

【課題】貫通孔内に形成された導電層に加わる応力を抑制できるとともに、導電層からの効果的な放熱も促すことができる貫通配線基板、及びこの貫通配線基板の製造方法を提供する。

【解決手段】半導体基板11(基板)の一方の面11aに配された電極層12と、電極層12の少なくとも一部が露呈するように半導体基板11内に開けられた貫通孔20と、貫通孔20の内側面20aを覆い、電極層12の少なくとも一部が露呈するように配された第一絶縁層15と、第一絶縁層15を介して、貫通孔20の内側面20a及び電極層12の露呈部を覆うように配され、電極層12と電気的に接続された導電層5と、導電層5を覆うように配された第二絶縁層16と、を少なくとも備えてなる貫通配線基板10であって、第二絶縁層16は、導電層5の表面形状に沿って形成されていることを特徴とする。

(もっと読む)

貫通配線付き接合基板

【課題】貫通孔内に配した樹脂が熱膨張することによって電極を破損することを防止した貫通配線付き接合基板の提供。

【解決手段】

一面1aに電極層2が形成された第一基板1、及び電極層2と接合樹脂層3を介して、第一基板1と接合された第二基板4とを備えた貫通配線付き接合基板10Aであって、第一基板1の他面1b側から電極層2が露出するまで第一基板1を貫通する貫通孔5と、貫通孔5の内部において、貫通孔5の内側面5c及び電極層2を覆う貫通配線層6と、貫通配線層6を覆い貫通孔5の内部に充填された充填樹脂部7とを有し、充填樹脂部7を構成する樹脂のヤング率は、接合樹脂層3を構成する樹脂のヤング率よりも小さいことを特徴とする貫通配線付き接合基板10A。

(もっと読む)

半導体装置の製造方法

【課題】信頼性を低下することなく、高集積化が可能な半導体装置の製造方法を提供する。

【解決手段】この半導体装置の製造方法は、薄膜抵抗体と配線層とが、接続層とビアホールに埋設されたタングステンプラグとを介して電気的に接続されてなる半導体装置の製造方法である。従来、接続層は、バリアメタル層を介して薄膜抵抗体と接続された構成である。この接続層としてアルミニウムを用いたものでは、接続層とタングステンプラグとの線膨張係数の差異に起因してストレスマイグレーションにより、接続層にボイドが発生する懸念があった。本発明では、接続層を除去する工程を実施し、タングステンプラグをバリアメタル層と直接接続する。これにより、タングステンプラグは、アルミニウムよりなる接続層を介することなく、薄膜抵抗体と電気的に接続される。したがって、接続層におけるボイドの発生を抑制し、半導体装置の接続信頼性を向上することができる。

(もっと読む)

半導体装置

【課題】半導体チップのバンプ電極と実装基板の配線との接続信頼性を向上できる技術を提供する。特に、バンプ電極下の最上層配線層に配線を配置しても、バンプ電極の平坦性を確保してバンプ電極とガラス基板に形成されている配線との接続信頼性を向上できる技術を提供する。

【解決手段】バンプ電極BP1の非重複領域Y直下にある最上層配線層に電源配線や信号配線からなる配線L1と、ダミーパターンDPを形成する。ダミーパターンDPは、配線L1間のスペースを埋めるように配置され、配線L1とスペースによって最上層配線層に生じる凹凸を緩和する。さらに、最上層配線層を覆うように形成される表面保護膜に対してCMP法による平坦化処理を実施する。

(もっと読む)

半導体装置の製造方法

【課題】高精細化に伴う、貫通孔の微細化とさらに高アスペクト化の貫通電極を有する半導体装置の製造方法を提案する。

【解決手段】半導体基板1の厚み方向に貫通する貫通電極4を有する半導体装置の製造方法であって、半導体基板1の第1の面1aから第1孔10を開口する第1の工程と、第1孔10を含む半導体基板1の第1の面1aに絶縁膜2を形成する第2の工程と、半導体基板1の第1の面1aと反対の面である第2の面1bから、少なくとも2つの第1孔10を含んで第1孔10へ貫通する第2孔11を開口する第3の工程と、第2孔11側よりスパッタ法によりシード層3を成膜する第4の工程と、シード層3に金属材料4aをメッキ法により半導体基板1の第1の面1aに達するまで第1孔10を埋める第5の工程と、半導体基板1の第2の面1bを第2孔11の深さ寸法より深く、厚み方向に研削する第6の工程と、を含む。

(もっと読む)

半導体装置の製造方法

【課題】膜厚の厚い応力緩和層を有するウェハレベルCSPと称される半導体装置において、第1電極と外部電極との接続不良が発生しにくい半導体装置の製造方法を提供する。

【解決手段】(1)応力緩和層を半導体ウェハの上に形成する工程、(2)応力緩和層の一部を除去した開口部を形成し、半導体ウェハ上の第1電極を露出する工程、(3)第1電極と接続し、開口部を充填するポスト部を形成する工程、(4)外部電極とポスト部を接続するための再配線層を応力緩和層の上に形成する工程、(5)再配線層の上に再配線保護層を形成する工程、(6)再配線保護層の一部を除去して、外部電極を形成するための第2電極を露出する工程、(7)第2電極上に外部電極を形成する工程を含む半導体装置の製造方法。

(もっと読む)

HEMT装置を製造するCMOSコンパチブルな方法とそのHEMT装置

【課題】Si−CMOSプロセス時術とコンパチブルなHEMT装置の製造法を提供する。

【解決手段】基板101を提供するステップと、III族窒化物層のスタックを基板上に形成するステップと、窒化シリコンからなり、スタックの上方層に対して上に位置すると共に当接する第1パッシベーション層301を形成し、第1パッシベーション層が、現場でスタックに堆積されるステップと、第1パッシベーション層に対して上に位置すると共に当接する誘電体層を形成するステップと、窒化シリコンからなり、誘電体層に対して上に位置すると共に当接する第2パッシベーション層303を形成し、第2パッシベーション層が、LPCVD、MOCVD又は同等の手法によって450℃より高い温度で堆積されるステップと、ソースドレイン・オーミック接触とゲート電極601を形成するステップとを備える。

(もっと読む)

半導体装置の製造方法

【課題】 厚い絶縁樹脂層のウェハレベルCSPで、第1電極(チップパッド)と外部電極(バンプ)との接続不良が発生しにくい半導体装置の製造方法を提供する。

【解決手段】 次の各工程を含む半導体装置の製造方法、(1)絶縁樹脂層を半導体ウェハの上に形成し、(2)開口径が(D1)となるよう絶縁樹脂層の一部を除去し半導体ウェハ上の第1電極を露出し、(3)フィルム状レジストを半導体ウェハの全面に、第1電極とレジストとの間が中空構造となるよう貼付け、(4)レジストをパターニングし、再配線層を絶縁樹脂層の上に形成し、レジストパターンを除去し、めっきした部分以外のシード層を除去し、(5)再配線層の上に再配線保護層を形成し、(6)再配線保護層の開口径(D2)が、D2>D1となるように再配線保護層の一部を除去して第1電極と、第2電極を露出し、(7)第1電極及び第2電極の上にめっき層を形成し、(8)めっき層を溶融して外部電極を形成する。

(もっと読む)

配線基板、赤外線センサー及び貫通電極形成方法

【課題】基板と貫通電極との間で形成される浮遊容量が小さい基板を提供する。

【解決手段】第1面2aと第1面2aと対向する第2面2bとを貫通して開口するビアホール2cを有する基板2と、基板2の第1面2aに設置され熱酸化膜を含む第1絶縁膜3と、ビアホール2c内の面とに設置され熱酸化膜を含む第3絶縁膜5と、ビアホール2c内で第3絶縁膜5に囲まれた導電体7と、を有し、第1面2aにおける第1絶縁膜3の厚みに比べてビアホール2c内の面における第3絶縁膜5の厚みが厚くなっている。

(もっと読む)

半導体装置及びその製造方法並びに積層型半導体装置

【課題】貫通電極と直接に接続される配線の信頼性を向上できるようにする。

【解決手段】半導体装置100は、貫通孔1Aを有する半導体基板1と、半導体基板1の上に形成された第2層間絶縁膜7bと、第2層間絶縁膜7bに貫通孔1Aを覆うように形成された第1の外部接続用配線8a1と、第2層間絶縁膜7bの上に、第1の外部接続用配線8a1を覆うように形成された第3層間絶縁膜7cと、第3層間絶縁膜7cにおける第1の外部接続用配線8a1の上側部分に形成された第2の外部接続用配線8b1と、貫通孔1Aにおける少なくとも内壁面に形成されると共に、各外部接続用配線8a1、8b1とそれぞれ電気的に接続される貫通電極15Aとを備えている。第1の外部接続用配線8a1は、複数の孔部19aを有し、第2の外部接続用配線8b1は、第1の外部接続用配線8a1の孔部19aを覆うように形成されている。

(もっと読む)

半導体装置、半導体装置の製造方法、回路基板および電子機器

【課題】電極パッドと貫通電極との接続面積を確保しつつ、下地膜が確実に形成される半導体装置、半導体装置の製造方法、回路基板および電子機器を提供する。

【解決手段】半導体基板10の能動面10a側に設けられた第一絶縁膜22と、第一絶縁膜22上に設けられた電極パッド12と、電極パッド12の形成位置に対応し、半導体基板10および第一絶縁膜22に形成された貫通孔H3と、貫通孔H3の少なくとも側面に設けられた第二絶縁膜23と、第二絶縁膜23と電極パッド12とを覆うように設けられた下地膜24と、下地膜24の内側で、貫通孔H3に埋め込まれた導電材料からなる貫通電極30と、を具備した半導体装置100において、貫通孔H3の側面と電極パッド12の裏面との角部23aに、第二絶縁膜23がフィレット状に形成されている。

(もっと読む)

電子部品、電子部品の製造方法、基板

【課題】チッピング検出用配線が他の部材で覆われている状態であっても、ダイシングによって電子部品を形成した後に、チッピング検出用配線の導通状態を検出するための電圧を印加できる基板を提供する。

【解決手段】電子部品40は、互いに平行を成す一方の主面41aと他方の主面41bが矩形状の基体41を有する。基体41の一方の主面41aには、第一チッピング検出用配線42が配されている。また、基体41の他方の主面41bには、第二チッピング検出用配線44が配されている。第一チッピング検出用配線42は貫通配線43aを介して第二チッピング検出用配線44に電気的に接続される。

(もっと読む)

半導体装置

【課題】半導体装置において、高電圧の配線層とその下方を横切るように配置された抵抗層との間の絶縁膜の耐圧を確保し、この配線層と抵抗層との間で破壊が起きるのを抑制することを目的とする。

【解決手段】第1半導体領域10に接続され第2半導体領域11上を通過するように第3配線層22が配置されている。第3配線層22と第2半導体領域11との間に配置される絶縁膜14内には、一端が第3配線層22に接続されると共に、他端が第1半導体領域11よりも電位の低い制御端子12に接続され、且つ第3配線層22とSOI層2との間において第3配線層22を少なくとも1回以上横切る構成で抵抗層25が配置されている。この抵抗層25は、第3配線層22を横切る部位の上面が他の部位よりも下方位置となるように段差状に形成されている。

(もっと読む)

半導体素子及び半導体素子の製造方法

【課題】ドレイン電極とドレイン層とのコンタクト抵抗を低減できる半導体素子及び半導体素子の製造方法を提供する。

【解決手段】半導体素子は、第1導電型のドレイン層と、ドレイン層上に形成された第1導電型のドリフト層と、ドリフト層上に選択的に形成された第2導電型のベース層と、ベース層上に選択的に形成された第1導電型のソース層と、ゲート絶縁膜を介して、ドリフト層、ベース層及びソース層に跨って形成されたゲート電極と、ベース層及びソース層に電気的に接続されたソース電極と、ドリフト層を貫通して、底部の少なくとも一部がドレイン層にまで達する第1のトレンチ内に形成され、ドレイン層と電気的に接続されたドレイン電極と、を備え、底部には、凹凸が形成されている。

(もっと読む)

1 - 20 / 270

[ Back to top ]