Fターム[5F033KK11]の内容

半導体集積回路装置の内部配線 (234,551) | 層間接続の下層配線層の材料 (17,020) | 金属及びその合金(シリサイドを除く) (9,842) | Cu (2,449)

Fターム[5F033KK11]の下位に属するFターム

Cu合金 (304)

Fターム[5F033KK11]に分類される特許

2,001 - 2,020 / 2,145

半導体装置の製造方法および半導体装置

【課題】配線溝底部の面粗れを防止するエッチングストッパーを配線溝の底部となる領域に導入することで、デバイス速度の向上、デバイス信頼性の向上を可能とする。

【解決手段】多孔質絶縁膜を含む層間絶縁膜を備えた半導体装置の製造方法において、前記層間絶縁膜に配線溝20を形成する前に、前記配線溝20底部となる領域、すなわち接続孔が形成される絶縁膜15上の配線溝が形成される領域に、前記層間絶縁膜の配線層が形成される絶縁膜18とは異なる材質の絶縁膜パターン17を形成する工程を備えている。

(もっと読む)

半導体装置とその製造方法

【課題】配線上にSiCN膜を有する半導体装置において、SiCN膜から流出する不安定なNによるレジストポイゾニングの発生を低減する。

【解決手段】SiCN膜を有する半導体装置の製造方法において、SiCN膜成膜時に一部に有機基を有する原料ガスとHeの流量比を1:4.2以上にする。または原料ガスの流量×原料ガスの有機基との結合数とHeの流量比を1:1.4以上にする。その結果、SiCN膜中のSiNH基の増加を抑制し、膜ストレス変化とポイゾニング不良の発生を合わせて抑制することが半導体装置を提供する。

(もっと読む)

レジスト除去方法

【課題】 低誘電率絶縁膜の比誘電率の増加を防止すると共にレジスト残渣を生じさせないレジスト除去を可能にする。

【解決手段】 レジストマスクをエッチングマスクにして、被処理基板上の有機成分含有の層間絶縁膜をRIEで加工した後(S1、S2)、上記レジストマスクを除去するために、はじめに、第1の温度下において水素ラジカル照射をして(S3)、レジストマスク表面に形成されている変質層を水素化分解する改質層に変換する(S4)。その後、第1の温度より高い第2の温度下において水素ラジカル照射を行い(S5)、上記改質層およびレジストマスクをアッシング除去する(S6)。このようにして、上記層間絶縁膜の組成変化およびその比誘電率の増加がなく、しかもレジスト残渣の生じないレジスト除去が可能になる。

(もっと読む)

炭素元素からなる線状構造物質の形成体及び形成方法

【課題】 触媒金属を堆積させる基板に依存することなく、基板を用いない場合でさえも、容易且つ確実にCNTを形成する。

【解決手段】 触媒微粒子生成システムを用いて、シリコン基板1の絶縁膜2上にチタン・コバルト複合微粒子3を堆積した後、CVD法によりチタン・コバルト複合微粒子3からCNT4を成長させる。

(もっと読む)

粘性前駆物質を用いた化学気相堆積による機能的に段階的な誘電体層の堆積方法

下にある層上に段階的な誘電体層を形成する方法であって、シリコン-炭素含有ガスと酸素含有ガスとキャリヤガスの混合物を阻止板と面板を備えたシャワーヘッドに流して、段階的な誘電体層の酸化物を多く含む部分を形成するステップであって、シリコン-炭素含有ガスが初期流量を持つ前記ステップと、シリコン-炭素含有ガスを第1中間流量で約0.5秒以上流すステップであって、第1中間流量が初期流量より大きい前記ステップと、シリコン-炭素含有ガスを第1中間流量より大きい最大流量で流して、段階的な誘電体層の炭素を多く含む部分を形成するステップと、を含む前記方法。 (もっと読む)

半導体装置及びその製造方法

【課題】半導体基板の一面側に形成された半導体素子の電極端子と、この半導体基板の他面側に形成された外部接続端子用のパッドとを電気的に接続する距離を可及的に短距離にできる半導体装置を提供することにある。

【解決手段】半導体素子12が一面側に造り込まれた半導体基板10の半導体素子形成面側には、半導体素子12の電極端子12aから半導体基板10と電気的に絶縁されて延出されたパターン14と、半導体素子12及びパターン14を覆う絶縁層16とが形成され、 半導体基板10の他面側には、パターン14と電気的に接続された外部接続端子用のパッド32が形成された半導体装置であって、該半導体基板10の他面側に開口され且つ底面にパターン14の半導体素子近傍の半導体基板側面が露出する凹部は、その側壁面を覆う絶縁層22と、パターン14の半導体基板側面に一端部が接続されていると共に、他端部が前記凹部の開口部を覆うように形成されたパッド32に接続された金属から成る柱状導体部30とによって充填されていることを特徴とする。

(もっと読む)

半導体装置およびこれを備えた電子機器

【課題】 半導体基板上に設けられる半田バンプの形状および高さのばらつきを抑制し、外部端子との接続不良を生じることのない半導体装置およびこれを備えた電子機器を提供する。

【解決手段】 第二の絶縁層15を介して第一配線14と第二配線16を上下に設けてなる多層配線構造を備えた半導体装置10において、第二の絶縁層15の下に位置する第一配線14に、第二の絶縁層15の上に位置する第二配線16が重なる部分であって、半田バンプが載置される領域16aを、第一配線14の補助領域14aの上に配する。

(もっと読む)

少なくとも1つの試験接点構造を備えたチップ

半導体本体(6)と、半導体本体(6)に形成された集積回路(7)と、集積回路(7)を保護するように形成された不動態層(14)と、試験接点構造(15)とを備えるチップ(2)において、試験接点構造(15)は、不動態層(14)の下に位置する試験接点層(16)と、試験接点層(16)に接続される試験接点ブロック(18)とを有し、試験接点ブロック(18)の一部は不動態層(14)の穴部(17)を通って試験接点層(16)へと突出するとともに試験接点層(16)に接続し、試験接点ブロック(18)は不動態層(14)の上に位置する接点領域(20)を有する。  (もっと読む)

(もっと読む)

軟金属導体およびその形成方法

【課題】 化学的機械的研磨プロセスで研磨した後でほぼ擦り傷なしの表面が得られるような、その最上部表面の硬度が改善された軟金属導体を提供する。

【解決手段】 その後の化学的機械的研磨ステップで研磨後にほぼ擦り傷なしの表面が得られるように、十分大きい粒子サイズを有する粒子から構成される最上部層を有する、半導体素子に使用するための軟金属導体78である。導電性軟金属構造の最上部層に軟金属構造の厚さの約20%以上の粒子サイズを有する金属粒子を付着する。

(もっと読む)

インダクタ及びその製造方法

【課題】チップ占有面積が小さく、自己共振周波数やQ値を高くできるオンチップインダクタ及びその製造方法を提供する。

【解決手段】互いに対面するように配置される右巻スパイラル構造と左巻スパイラル構造とが、半導体基板に対して水平方向を軸に巻かれて構成される。そして、右巻スパイラル構造の中心端と左巻スパイラル構造の中心端とが接続される。巻軸方向から見て、右巻スパイラル構造を流れる電流の向きと左巻スパイラル構造を流れる電流の向きが等しく、これらの配線がそれぞれ近傍に位置している。

(もっと読む)

アクティブマトリクス基板の製造方法、アクティブマトリクス基板、電気光学装置並びに電子機器

【課題】 ドライプロセスとフォトリソエッチングを組み合わせた工程の回数を低減することができるアクティブマトリクス基板の製造方法等を提供することを目的とする。

【解決手段】 アクティブマトリクス基板20の製造方法において、第1方向又は第2方向のいずれか一方の配線42が交差部56において分断された格子パターンの配線40,42,46を基板P上に形成する第1工程と、交差部56及び配線40,42,46の一部上に絶縁膜と半導体膜30とからなる積層部を形成する第2工程と、積層部上に分断された配線42を電気的に連結させる導電層49、及び半導体膜30を介して配線42と電気的に接続される画素電極45を形成する第3工程と、を有する。

(もっと読む)

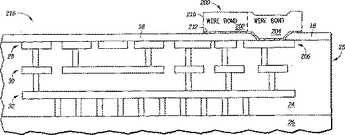

ボンディングパッドを有する半導体装置及びその形成方法

ボンディングパッド(200)は第1ワイヤボンディング領域(202)と、第2ワイヤボンディング領域(204)と、を含む。一実施形態では、第1ワイヤボンディング領域(202)がパッシベーション(18)を覆って延びる。別の実施形態では、ボンディングパッドはプローブ領域、第1ワイヤボンディング領域、及び第2ワイヤボンディング領域を有する。一実施形態では、プローブ領域及びワイヤボンディング領域がパッシベーション(18)を覆って延びる。ボンディングパッドはどのような数のワイヤボンディング領域及びプローブ領域も有することができ、かつこれらの領域をどのような構成として有することもできる。ボンディングパッドが複数のワイヤボンディング領域を含むことができるので、マルチチップパッケージにおける場合のように単一のボンディングパッドへの複数のワイヤ接続を行なうことができる。ボンディングパッドがパッシベーションを覆って延びる形でパッドを設けることができるので、集積回路チップ面積を小さくすることもできる。  (もっと読む)

(もっと読む)

電子デバイス及びその製造方法

【課題】 low−k膜のような疎水性膜を使用した多層配線構造において、層間絶縁膜に使用する疎水性膜とライナー膜又はバリア膜として使用する親水性膜との界面剥離の発生を防止する。

【解決手段】 電子デバイスは、図示しない基板上に形成された第1の層間絶縁膜11の下層配線溝11aを埋め込むように形成された下層配線12と、下層配線12の上に形成されたバリア膜13と、第1の層間絶縁膜11及びバリア膜13の上に形成された第2の層間絶縁膜14とを備えている。そして、電子デバイスは、第1の層間絶縁膜11と第2の層間絶縁膜12とが接合している界面を有している。

(もっと読む)

半導体チップの製造方法、半導体チップ、半導体装置の製造法および半導体装置

【課題】貫通電極の形成に伴う半導体基板の金属汚染を抑制することができる半導体チップの製造方法を提供する。

【解決手段】一方表面に機能素子3が形成されたウエハWの当該一方表面に、ウエハWの厚さよりも浅い所定の深さの表面側凹所9を形成する。続いて、表面側凹所9内に非金属材料を供給して、当該非金属材料からなるダミープラグ8を形成する。次に、ウエハWにおいて上記一方表面とは反対の面である裏面Wrを機械的に研削して、ウエハWを表面側凹所9の深さより小さな厚さに薄型化して、表面側凹所9をウエハWを貫通する貫通孔にする。その後、この貫通孔内のダミープラグ8を除去し、さらに、この貫通孔内に金属材料を供給して貫通電極を形成する。

(もっと読む)

一体型の低kハードマスク

本発明の実施例によって、第一ILD層と第二ILD層との間にハードマスク層を有する装置が与えられる。ハードマスク層は、第一ILD層および/または第二ILD層にほぼ等しいk値を有する。 (もっと読む)

レジスト除去方法及び半導体装置の製造方法

【課題】 低誘電率絶縁膜の比誘電率の増加を防止すると共にレジスト残渣を生じさせないレジスト除去を可能にする。

【解決手段】 ビアホール用開口3を有するレジストマスク4をエッチングマスクにして、第1キャップ層2c、第1低誘電率膜2bを順次に反応性イオンエッチング(RIE)でドライエッチングしビアホール5を形成する。そして、レジストマスク4の除去では、はじめに、上記RIEでレジストマスク4表面部に形成された変質層4aに対して、ホットプレートにより空気雰囲気、300℃温度、3分程度の熱処理を施すことで、変質層4aを少なくともその一部が酸素と反応した改質層4bに変換させる。その後に、この改質層4bおよびレジストマスク4に水素ラジカルを照射して残渣のないレジスト除去を行う。

(もっと読む)

半導体装置の設計方法及び半導体装置

【課題】低誘電率層間膜材料を用いた多層配線におけるスタックビアの熱応力歪みによる信頼性低下を予め防ぐことを可能とするスタックビアレイアウト設計方法および半導体装置を提供する。

【解決手段】スタックビア設計レイアウト結果から温度変化による歪みによって故障発生可能性の高い危険スタックビア部を特定のスタックビア構造をもとに抽出し、その危険スタックビア部の温度変化歪み量を算出して所定の臨界歪み量を超える臨界スタックビアを抽出し、そのビアを含む領域に回路機能に変化を与えないように新規ビア構造を追加配置することで臨界スタックビアの歪み量を低減させて、信頼性の高いスタックビアのレイアウト結果を得る。また前記の特定のスタックビア構造を有しない半導体装置を構成する。

(もっと読む)

半導体装置

【課題】 半導体装置中のクラックの伝播を抑制し、他の領域に影響を与えないようにする。

【解決手段】 シリコン基板101上に設けられたSiCN膜105およびSiOC膜107を貫通する凹部の側面を覆う界面補強膜115を設ける。界面補強膜115はSiOC膜113と連続一体に形成され、エアギャップ117を有する。

(もっと読む)

半導体集積回路装置

【課題】 低い比誘電率を有し、かつ望ましい特性を有する絶縁膜を有する半導体集積回路装置を提供することである。

【解決手段】 半導体集積回路装置は、層間絶縁膜の一部として比誘電率が2.5以下のSiC:H膜を含む。

(もっと読む)

半導体装置の製造方法及び半導体装置

【目的】 配線抵抗を低減させながら歩留まりを向上させたバリアメタル膜を形成することを目的とする。

【構成】 基体上に絶縁膜を形成する絶縁膜形成工程(S102〜S108)と、前記絶縁膜に開口部を形成する開口部形成工程(S110)と、PVD法を用いて、前記絶縁膜上と開口部内とに第1のバリアメタル膜を形成する第1のバリアメタル膜形成工程(S116)と、その上に、CVD法を用いて第2のバリアメタル膜を形成する第2のバリアメタル膜形成工程(S118)と、その上に、PVD法を用いて第3のバリアメタル膜を形成する第3のバリアメタル膜形成工程S120)と、その上に、導電性材料を堆積させる堆積工程(S112,S124)と、を備え、前記絶縁膜上に形成された前記第1と第2と第3のバリアメタル膜の合計膜厚が、8nmより小さくなるように形成することを特徴とする。

(もっと読む)

2,001 - 2,020 / 2,145

[ Back to top ]