Fターム[5F033MM13]の内容

半導体集積回路装置の内部配線 (234,551) | 配線構造、形状の特徴点 (15,803) | 配線の断面構造 (9,197) | 2種類以上の導電層よりなる配線 (8,898) | バリア層を含むもの (2,960)

Fターム[5F033MM13]に分類される特許

2,401 - 2,420 / 2,960

薄膜配線層

【課題】 平面表示装置用の配線層として有効な、ウェットエッチング性と耐熱性とを確保しつつ、耐湿性をも改善できる薄膜配線層を提供する。

【解決手段】 基板上に形成される薄膜配線層であって、AgまたはCuを主成分とする主導体層と該主導体層の上層および/または下層を覆う被覆層からなり、該被覆層は添加元素としてCuを1〜25原子%、(Ti、Zr、Hf、V、Nb、Ta、Cr、Mo、W)から選択される1種または2種以上の添加元素を1〜25原子%含有し、かつ添加元素の総量を35原子%以下とし、残部が不可避的不純物およびNiからなる薄膜配線層である。

(もっと読む)

湿式処理層の欠陥減少方法及びその装置

本発明は、脱ガスされた電気化学的析出溶液、脱ガスされた電気化学的研磨溶液、脱ガスされた無電解析出溶液、脱ガスされた洗浄液などの脱ガスされた処理溶液を用いることによって、導体層を湿式処理するための方法及び装置を提供する。この技術は、処理装置に脱ガスされた処理溶液を送る前に処理溶液を脱ガスすること又は処理装置においてイン−サイチュ(in−situ)で処理溶液を脱ガスすることを含んでいる。 (もっと読む)

集積回路及びその製造方法

複数のアクティブエリア(12、14、16)が電界領域(18)によってそれぞれ分離された集積回路(10、250)と、その集積回路(10、250)の製造方法である。第1アクティブエリア(12)と電界領域(18)上に第1ポリシリコンフィンガー(20)が形成され、第2アクティブエリア(16)と電界領域(18)上に第2ポリシリコンフィンガー(22)が形成される。第1アクティブエリア(12)と電界領域(18)上に第1絶縁層(168)が形成され、第2アクティブエリア(16)と電界領域(18)上の第1絶縁層(168)の一部上に第2絶縁層(170)が形成される。第1の電気相互接続(175)は、第1ポリシリコンフィンガー(20)上に第1ポリシリコンフィンガーから誘電的に絶縁されて形成され、第2電気相互接続(177)は第2アクティブエリア(16)上に第2アクティブエリアから誘電的に絶縁されて形成される。第1電気相互接続(177)は第2ポリシリコンフィンガー(22)に電気的に結合される。  (もっと読む)

(もっと読む)

半導体素子の製造方法

【課題】接続層の形成が完了した下部構造物の上に形成される金属配線のステップカバレッジ特性を改善して信頼性を向上可能な半導体素子の製造方法を提供すること。

【解決手段】接触口(23)に沿って層間絶縁膜(22)上にTiNバリア金属膜(44)を形成するステップと、TiNバリア金属膜上にタングステン膜を形成するステップと、タングステン膜に対して過度エッチングを伴う第1エッチングを行い、接触口の内部に埋め込まれるタングステンプラグ(45A)を形成するステップと、露出したTiNバリア金属膜に対して第2エッチングを行い、第1エッチング時に生成された接触口のトップ部の側壁の垂直プロファイルをスローププロファイル(45D)に緩和させるステップと、全面にアルミニウム膜を形成するステップと、該アルミニウム膜を選択的にパターニングし、アルミニウム金属配線を形成するステップとを含む。

(もっと読む)

半導体装置及びその製造方法

【課題】MIMキャパシタの信頼性を向上させた半導体装置とその製造方法を提供する。

【解決手段】半導体装置は、半導体基板と、前記半導体基板上に第1の絶縁膜を介して形成された第1の配線と、前記第1の絶縁膜上に形成されたMIMキャパシタと、前記MIMキャパシタを覆って形成された第2の絶縁膜と、前記第2の絶縁膜表面に形成された第2の配線と、前記MIMキャパシタを取り囲むように前記第2の絶縁膜に埋設されたガードリングと、を有する。

(もっと読む)

成膜方法、成膜装置およびコンピュータ読取可能な記憶媒体

【課題】 基板との密着性が良好であり、所定の厚さの連続したCu膜を成膜することができる成膜方法を提供する。

【解決手段】 チャンバ1内にウエハWを配置し、二価のCuの原料物質をウエハW上に供給し(STEP3)、この原料物質の供給停止後、チャンバ1内の残留ガスを除去し(STEP4)、H2ガスをウエハWに供給し、その際にプラズマによりH2ガスをラジカル化させて、ウエハW上に第1段階のCu膜50aを形成し(STEP5)、H2ガスの供給停止後、チャンバ1内の残留ガスを除去し(STEP6)、一価のCuの原料物質をH2ガスとともにウエハWに供給して、第1段階のCu膜50a上に第2段階のCu膜を形成し、これにより連続したCu膜50bを成膜する(STEP7)。

(もっと読む)

半導体装置の製造方法

【課題】 信頼性の高い半導体基板を効率よく製造する方法を提供する。

【解決手段】 電極10パッドを有する半導体基板2の電極10が形成された面に、芳香族化合物を含む樹脂によって、電極10の少なくとも一部を避けて樹脂層14を形成する。Arガスを利用して、電極10の表面から酸化膜を除去するとともに、樹脂層14の表面を炭化させて炭化層24を形成する。電極10から炭化層24上に至る配線32を形成する。その後、配線32をマスクとして炭化層24をO2プラズマ20でエッチングして、炭化層24を部分的に除去する。

(もっと読む)

埋込導電体の形成方法

【課題】 埋込導電体の形成方法に関し、ビアホールや埋込配線用溝の形成工程におけるダメージを低減するとともに、ビアホールや埋込配線用溝の形成後の清浄化工程のスループットを向上する。

【解決手段】 埋込導電体6用の凹部4を形成したのちに、脱ガス処理と前処理としての有機酸5を用いたドライクリーニングとを一連の工程として行う。

(もっと読む)

半導体装置の製造方法

【課題】 溝の内部に窒化金属膜を介して埋め込まれたフォトレジストのプラズマアッシングに際して、窒化金属膜の酸化を防止する。

【解決手段】 半導体基板の主面上にSiO2膜28を成膜する工程と、SiO2膜28にシリンダ孔29を形成する工程と、シリンダ孔29の底面及び側面を含み、全面にTiN膜(30)を成膜する工程と、シリンダ孔29の内部のTiN膜(30)上にフォトレジストを埋め込む工程と、SiO2膜28上に露出するTiN膜(30)を除去する工程と、シリンダ孔29の内部に埋め込まれたフォトレジストをプラズマアッシングによって除去する工程とを有し、アッシング工程では、酸素を含まない非酸素系ガスのプラズマを用いる。

(もっと読む)

半導体装置およびその製造方法

【課題】 ドレインコンタクトの形成時にSTIと活性領域との段差に起因したエッチング残りでコンタクト面積の縮小で抵抗が高くなるのを防止する。

【解決手段】 NOR型フラッシュメモリにおいて、ゲート電極4の形成後にスペーサとして第1のシリコン窒化膜15を形成する。この後、ドレインコンタクトの形成領域のSTI2の高さをエッチングにより低くして活性領域3との段差を小さくする(ΔH<Δh)ことで、第2のシリコン窒化膜16形成後のコンタクト形成で、段差部分に残渣が少なくなりコンタクト面積の減少を防止できる。これにより、コンタクト抵抗の低減を図れ、しかもゲート絶縁膜であるシリコン酸化膜7の端面が保護されているので悪影響を与えることがない。

(もっと読む)

プラズマ処理方法および半導体装置の製造方法

【課題】絶縁膜の誘電率の変動や、絶縁膜への水分吸着を抑制することができるプラズマ処理方法および半導体装置の製造方法を提供する。

【解決手段】被処理基板10上の絶縁膜100に、少なくともCH系ガス、CO系ガスのいずれかを含むガスを用いたプラズマ処理を行う。

(もっと読む)

半導体装置及びその製造方法

【課題】 MEMSデバイスをCMOS LSIと同一基板上に混載する点において、LSIプロセスと整合性良く、またLSI領域から発生する水分、熱などのMEMSデバイスへの影響を抑制することができる半導体装置を提供する。

【解決手段】 第1領域及びこの第1領域に隣接する第2領域を有する半導体基板(500)と、第2領域に形成される集積回路(401)と、第1領域と第2領域との境界に壁状に形成され、第1及び第2領域を電気的且つ空間的に分離する支柱構造体(414)と、この支柱構造体に支持され、第1及び第2領域上を覆うように積層形成されている薄膜構造体(419、427)と、第1領域にある薄膜構造体下部に形成される空間に配置される機械的可動部を備え、集積回路に電気的に接続されている素子(424)とを具備する。

(もっと読む)

半導体装置の製造方法

【課題】

配線の酸化又は層間絶縁膜の変質などの表面異常によって生じる層を確実に除去することができる半導体装置の製造方法を提供すること。

【解決手段】

本発明の半導体装置の製造方法は、半導体基板上の第1層間絶縁膜に形成された第1凹部内に第1バリア層を介して第1配線が形成された配線基板の表面に形成された異常層を除去し、得られた配線基板上に第1拡散防止膜及び第2層間絶縁膜を順次形成し、第1配線を露出させるように、第2層間絶縁膜及び第1拡散防止膜に第2凹部を形成し、得られた配線基板上に第2バリア層を形成し、第2凹部内に第2配線を形成し、得られた配線基板上に第2拡散防止膜を形成する工程を備える。

(もっと読む)

半導体装置及びその製造方法

【課題】 水分の侵入、腐食の影響を集積回路に及ぼさないガードリング構造を有する半導体装置及びその製造方法を提供する。

【解決手段】 半導体基板10は、ICチップ製品CHIPの基材である。製品実パターン領域CPAは、図示しないが複数の素子を配線層で接続し集積回路化した領域を示す。集積回路に関係する配線層の構造の一部で、製品実パターン領域CPAすなわち集積回路の周辺の絶縁層12中に、防湿用の壁として二重以上のガードリングGR(GR1,GR2)が形成されている。この二重以上のガードリングGR(GR1,GR2)は、互いに絶縁層12を隔てて内側、外側の位置関係を有し独立している。

(もっと読む)

半導体装置の製造方法

【課題】配線溝内の導電膜への結晶欠陥の集合を抑制し、配線内のボイドの発生を防止する半導体装置の製造方法を提供する。

【解決手段】基板11上に設けられた層間絶縁膜12に、凹部13を形成する工程と、凹部13を埋め込む状態で、層間絶縁膜12上に、導電膜16を形成する工程と、導電膜16上に、導電膜16とは異なる材質からなり、かつ応力の異なる被覆膜21を形成する工程と、被覆膜21が設けられた状態で、導電膜16に熱処理を行う工程とを有することを特徴とする半導体装置の製造方法である。

(もっと読む)

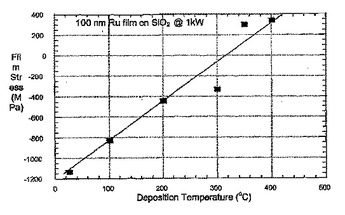

ルテニウム系材料およびルテニウム合金

本明細書には、ルテニウムおよび元素周期表のIV族、V族、もしくはVI族の元素の少なくとも1つの元素またはこれらの組合せが含まれる、蒸着法または原子層堆積法において用いるための合金が記載される。また、本明細書には、ルテニウム系材料またはルテニウム系合金を含む少なくとも1つの層、および元素周期表のIV族、V族、もしくはVI族の元素の少なくとも1つの元素またはそれらの組合せを含む少なくとも1つの層が含まれる積層材料が記載される。  (もっと読む)

(もっと読む)

半導体装置の製造方法

【課題】 銅配線のEM耐性とSM耐性を、ともに向上させる。

【解決手段】 不純物を含む銅めっき膜をシリコン基板1の上に成膜した後、銅めっき膜を結晶成長させて、複数の銅結晶粒とそれらの粒界に分布する不純物層とで構成された第一銅膜9cを形成する。次に、第一銅膜9cより不純物濃度が高い第二銅膜10を第一銅膜9cの上に形成し、第二銅膜10に含まれる不純物を第一銅膜9cに拡散させて、第一銅膜9cの結晶粒界に偏析する不純物濃度を高める。

このように形成することにより、第一銅膜9cの結晶粒の粒径は十分に大きくなる。これにより、結晶粒界における拡散パスを減少させ、EM耐性を向上させることができる。また、第一銅膜9cに発生するボイドの移動を抑え、SM耐性を向上させることができる。

(もっと読む)

半導体装置及びその製造方法

【課題】絶縁膜中への導電性金属の拡散を抑制することができる半導体装置の製造方法を提供すること。

【解決手段】本発明の半導体装置の製造方法は、(1)半導体基板上に形成された絶縁膜に溝を形成し、(2)前記溝の内面及び前記絶縁膜上にバリア膜を形成し、(3)前記溝を充填するようにバリア膜上に導電性金属層を形成し、(4)導電性金属層の表面が前記絶縁膜の表面よりも低くなるように、前記絶縁膜上の導電性金属層及びバリア膜並びに前記溝内の導電性金属層の一部を除去し、(5)前記絶縁膜及び導電性金属層上に金属拡散防止膜を形成し、(6)導電性金属層上の金属拡散防止膜の少なくとも一部を残すように、前記絶縁膜上の金属拡散防止膜と前記絶縁膜の一部を除去する工程を含むことを特徴とする。

(もっと読む)

メモリアレイに適した接触機構およびその製造方法

【課題】NAND型フラッシュメモリアレイにおいて、選択トランジスタ線及びソース線の低抵抗化をはかることのできる接触機構及びその製造方法を提供する。

【解決手段】基板主表面1にトンネル誘電体層6が堆積され、かつ該トンネル誘電体層6上に、第1導電線が第1方向に延びて配置された、基板1を提供する工程と、第1導電線に誘電体材料の層を堆積する工程と、制御ゲート層10を堆積する工程と、第1導電線をパターン形成し、ゲート積層20を形成する工程と、ゲート積層20間に誘電体材料を堆積する工程と、ゲート積層20を部分的に除去して、選択トランジスタ線24が形成される領域に浮遊ゲート電極9を露出させることで、第2方向に延びる選択トランジスタ線溝23を形成する工程と、選択トランジスタ線溝23に導電性材料を充填し、選択トランジスタ線24を形成する工程とを含んでいる。

(もっと読む)

半導体装置とその製造方法

【課題】配線表面にバリア膜を形成する前に、NH3を含むプラズマ処理を行う際に発生する低誘電率膜のダメージを低減するとともに、比誘電率上昇による配線遅延の問題を低減する配線構造の形成方法を提供する。

【解決手段】基板上に3以下の比誘電率を有する絶縁膜を形成する工程と、絶縁膜内にCuからなる配線を形成する工程と、配線表面上に還元性ガスを供給する工程と、還元性ガスを供給した後、前記配線上にバリア膜を形成することを特徴とする、半導体装置の製造方法を提供する。その結果、配線構造を形成後、バリア膜を形成する前に配線表面に対してプラズマを供給しないので、低誘電率膜がダメージを受けるのを防止するとともに、ゲート酸化膜等の劣化を防ぐことが出来る。

(もっと読む)

2,401 - 2,420 / 2,960

[ Back to top ]