Fターム[5F033NN02]の内容

半導体集積回路装置の内部配線 (234,551) | 層間構造の特徴点 (9,232) | コンタクトホールへの穴埋め構造 (6,462) | 介在層を有するもの (6,157)

Fターム[5F033NN02]の下位に属するFターム

Fターム[5F033NN02]に分類される特許

21 - 35 / 35

成膜方法およびコンピュータにより読み取り可能な記憶媒体

【課題】CVD法において、500℃未満の低い成膜温度でも異常成長のない良質の金属窒化膜を成膜することが可能な成膜方法を提供すること。

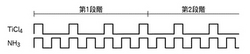

【解決手段】成膜温度に加熱された被処理基板に金属化合物ガスおよび窒素含有還元ガスを供給してCVDにより被処理基板上に金属窒化膜を直接堆積させる期間を含む第1段階と、同様に金属化合物ガスおよび窒素含有還元ガスを供給してCVDにより前記第1段階で堆積された初期の金属窒化膜の上にさらに金属窒化膜を堆積させて所定の膜厚とする第2段階とを含み、前記第1段階および前記第2段階ともに、前記金属化合物ガスおよび窒素含有還元ガスを供給する第1ステップと、前記金属化合物ガスを停止して前記窒素含有還元ガスを供給する第2ステップとからなるサイクルを1サイクル以上繰り返す。

(もっと読む)

半導体装置の製造方法

【課題】良好な抵抗値を示すコンタクトプラグを備えた半導体装置の製造方法を提供する

こと。

【解決手段】

コンタクトプラグを備えた半導体装置の製造方法であって、半導体シリコン基板表面に設けられた高濃度N導電型拡散層の表面部分および層間絶縁層により形成されたコンタクトホールを通じて、加速エネルギーを30〜120keVの範囲とし、注入量を1.0×1013〜5.0×1014/cm2の範囲としてインジウムイオンを注入するこにより、前記コンタクトホール下部の前記高濃度N導電型拡散層の表面部分にインジウム含有層を形成することを特徴とする半導体装置の製造方法。

(もっと読む)

半導体装置およびその製造方法

【課題】 半導体装置の配線構造中の絶縁膜を低誘電率化するとともに、製造安定性を向上させる。

【解決手段】 半導体装置100は、銅含有金属により構成される第1配線108と、第1配線108の上部を被覆する第1のCuシリサイド層111と、Cuシリサイド層111の上部に設けられ、第1配線108に接続される導電性の第1プラグ114と、第1プラグ114の上部を被覆するCuシリサイド層117と、第1配線108の側壁から第1プラグ114の側壁にわたって設けられ、第1配線108の側壁と、第1配線108の上部と、第1プラグ114の側壁とを覆うように形成された第1ポーラスMSQ膜105と、第1ポーラスMSQ膜105の下層にあって、第1配線108の側壁下部に接するとともに、第1ポーラスMSQ膜105よりも膜密度の高い第1SiCN膜103と、を有する配線構造を備える。

(もっと読む)

半導体装置およびその製造方法

【課題】強誘電体又は高誘電体を用いた容量絶縁膜を有するキャパシタをロジックに混載する半導体装置において、レイアウトの自由度を高め、マスク枚数を抑制する。

【解決手段】本発明の半導体装置では、半導体基板10の上方に、第1の電極17、第2の電極18および容量絶縁膜19が基板の上面と垂直方向に配置することにより、キャパシタ20が構成されている。キャパシタ20が複数設けられている場合には、それぞれは同一の形状を有していなくてもよく、コンタクトプラグ23および配線24等により構成されるロジック回路に応じて配置される。

(もっと読む)

半導体装置及びその製造方法

【課題】 容易に切断できるヒューズ素子を高密度に配置できるようにする。

【解決手段】 下層配線205と上層配線210と当該両配線を接続するビア209とからヒューズ素子が構成されている。ビア209の下面の一部分は下層配線205の外側に位置する。

(もっと読む)

半導体装置及びその製造方法

【課題】LSIの多層配線、特に半導体素子と接続する下層に近い配線に対して低誘電率絶縁膜や微細な配線の機械的/熱的ストレスを抑えた半導体装置及びその製造方法を提供する。

【解決手段】半導体基板上に形成された半導体素子12と、前記半導体基板上に積層された複数の絶縁膜107,112,117,122と、前記複数の絶縁膜内にそれぞれ形成された複数の配線層108,113,118,123と、前記各配線層の上面及び両側面を連続的に覆うバリアメタルとを具備する半導体装置。

(もっと読む)

インシチュ薄膜蒸着方法

【課題】TiSiX/Ti膜またはTiSiX/Ti/TiN膜を連続的に蒸着できるインシチュ薄膜蒸着方法を提供する。

【解決手段】インシチュ薄膜蒸着方法は、内部にロボットアーム11が設置される移送チャンバ10と、移送チャンバ10にクラスタータイプに設置されて内蔵された基板W上に薄膜を蒸着する複数個のチャンバ20、30、50とを備える薄膜蒸着装置を利用して、基板W上に抵抗性コンタクト及びバリヤーの役割を行う薄膜を蒸着するに際し、任意のチャンバに、Ti元素を含む第1反応ガスとSi元素を含む第2反応ガスとを供給し、チャンバ20の内部にプラズマを印加して、基板WにTiSiX膜を蒸着し、基板Wを移送チャンバ10を介して他のチャンバ30に移送した後、TiSiX膜上にTiN薄膜を蒸着する。

(もっと読む)

半導体装置及びその製造方法

【課題】 製造工程数を削減し、低コスト化を実現した半導体装置を提供する。

【解決手段】 本発明の半導体装置は、半導体チップ上に形成されたパッド2と、前記パッド2上に形成された電極接続部7と、前記パッド2を露出するように前記半導体チップの裏面に形成された開口部14と、前記開口部14の側壁に形成された第1の絶縁膜15と、前記第1の絶縁膜15を有した前記開口部内に形成された金属膜(Cu17)とを具備することを特徴とするものである。

(もっと読む)

めっき装置及びめっき方法

【課題】 比較的簡単な構成で、例えアスペクト比が高く、深さが深いビアホール等にあっても、内部にボイドを発生させることなく、金属膜を確実に埋込むことができるようにする。

【解決手段】 めっき液188を保持するめっき槽186と、基板Wを保持して該基板に通電し、基板の被めっき面をめっき槽内のめっき液に接触させるホルダ160と、めっき槽内のめっき液に浸漬させて配置されるアノード214と、アノードとホルダで保持した基板との間に配置され、めっき槽内のめっき液を攪拌するめっき液攪拌部220,224と、基板とアノードとの間に電圧を周期的に印加するめっき電源230を有し、基板とアノードとの間に電圧が印加されていない時にめっき液攪拌部によるめっき液の攪拌を行い、基板とアノードとの間に電圧が印加されている時にめっき液攪拌部によるめっき液の攪拌を停止する。

(もっと読む)

配線基板の製造方法および半導体モジュールの製造方法

【課題】埋め込み型の配線層を形成するに際して、ウェハの反りやディッシングの発生を防止することができ、高精度な均一性と再現性を容易に得ることのできる配線基板の製造方法を提供する。

【解決手段】基板10に溝10Aを形成した後、溝10Aの内部を含むシリコン基板10上にバリアメタル層13およびシード層14をこの順で形成する。エッチングにより、シード層14の溝10A内の領域以外の部分を選択的に除去した後、めっきによりシード層14上に金属15(例えば銅(Cu))を選択的に成長させて配線層L1を形成する。配設層L1を形成するに際し、シード層14を用いためっきにより溝10A内にのみ金属15を選択的に成長させるようにしたので、従来のように、基板10上に金属層が厚く成膜されることはなく、金属層に起因してシリコン基板10が反るような虞がなくなる。

(もっと読む)

電子デバイスの洗浄方法

【課題】 金属配線の露出部分の腐食を抑制しつつ、ドライエッチング後に生じた堆積ポリマーを完全に除去し、それにより高信頼性を有する金属配線を得る。

【解決手段】 部分的に露出した金属配線が設けられているシリコン基板100上に洗浄液123を供給し、該洗浄液123によってシリコン基板100の表面を覆う。その後、シリコン基板100上への洗浄液の供給を停止して、シリコン基板100の表面を覆う洗浄液の少なくとも一部分をシリコン基板100上に保持した後、シリコン基板100の表面を覆う洗浄液を除去する。

(もっと読む)

レジスト除去方法

【課題】 低誘電率絶縁膜の比誘電率の増加を防止すると共にレジスト残渣を生じさせないレジスト除去を可能にする。

【解決手段】 レジストマスクをエッチングマスクにして、被処理基板上の有機成分含有の層間絶縁膜をRIEで加工した後(S1、S2)、上記レジストマスクを除去するために、はじめに、第1の温度下において水素ラジカル照射をして(S3)、レジストマスク表面に形成されている変質層を水素化分解する改質層に変換する(S4)。その後、第1の温度より高い第2の温度下において水素ラジカル照射を行い(S5)、上記改質層およびレジストマスクをアッシング除去する(S6)。このようにして、上記層間絶縁膜の組成変化およびその比誘電率の増加がなく、しかもレジスト残渣の生じないレジスト除去が可能になる。

(もっと読む)

半導体装置およびその製造方法

【課題】低電気抵抗化および高信頼性化可能なコンタクトを備え、高速伝送が可能で信頼性の高い半導体装置およびその製造方法を提供する。

【解決手段】 コンタクト20、23を、CVD法を用いて、シリサイド膜19、22、シリコン窒化膜15aおよび第1層間絶縁膜15bの内壁に接する表面に、表面からコンタクト内部方向への距離に応じて窒素含有量が減少する組成勾配を有する窒化タングステン部24を形成し、その内側にタングステンが充填されたタングステン部25を形成する。窒化タングステン部24とタングステン部25との界面の酸化や汚染を防止する。

(もっと読む)

半導体装置の製造方法

【課題】コリメータを備えるスパッタリング装置の生産効率を向上させることのできる技術を提供する。

【解決手段】上部シールド13の上部折曲部13aと下部折曲部13bとの上下垂直位置の距離を相対的に短く、上部シールド13の下縁部の内径を相対的に広くして、ターゲット3と上部シールド13との間の隙間量を相対的に広くし、さらに台座リング15の内径を相対的に広く、台座リング15の高さを相対的に低くして、パッキングプレート11(ターゲット3)と台座リング15との間の隙間量を相対的に広くすることにより、ターゲット3と上部シールド13との接触またはパッキングプレート11(ターゲット3)と台座リング15との接触を回避する。

(もっと読む)

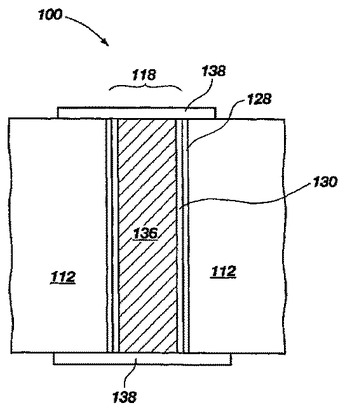

導電性構成部品、貫通ビア及び導電性貫通ウェーハ・ビアを含む半導体構成部品を製造するためのプロセス及び集積化スキーム

半導体構成部品に導電性ビアを形成するための方法が開示される。この方法は、第1の表面及び反対側の第2の表面を有する基板112を設けるステップを含む。この基板に、第1の表面と反対側の第2の表面の間に延びる少なくとも1つの穴118が形成される。基板のこの少なくとも1つの穴を画定している側壁にシード層128が形成され、導電層130でコーティングされ、この少なくとも1つの穴の内部の残りの空間に、導電性材料又は非導電性充てん材料136が導入される。基板を貫通した導電性ビアを、ブラインド・ホールを使用して形成する方法も開示される。本発明の導電性ビアを含む基板を有する半導体構成部品及び電子システムも開示される。  (もっと読む)

(もっと読む)

21 - 35 / 35

[ Back to top ]