Fターム[5F033NN05]の内容

半導体集積回路装置の内部配線 (234,551) | 層間構造の特徴点 (9,232) | コンタクトホールへの穴埋め構造 (6,462) | 介在層を有するもの (6,157) | 側面 (337)

Fターム[5F033NN05]に分類される特許

1 - 20 / 337

銅を含む電極連結構造体

半導体装置、半導体装置の製造方法、および電子機器

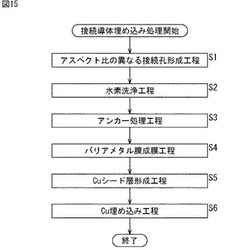

【課題】アスペクト比の異なる複数の開口下部に接続される配線に対して最適な処理を施すことができるようにする。

【解決手段】半導体装置の製造方法において、第1の半導体基板と第2の半導体基板が接合された半導体基板の第1の開口の下部配線と、貫通接続孔と異なるアスペクト比の第2の開口の下部配線に対して、バリアメタル膜の成膜と、スパッタガスによる物理エッチングを同時に行うアンカー処理工程が含まれる。本技術は、例えば、固体撮像装置などの半導体装置に適用できる。

(もっと読む)

貫通電極基板の製造方法

【課題】基板の表裏を導通する導通部における電気特性を向上した貫通電極基板及びそれを用いた半導体装置を提供すること。

【解決手段】本発明の貫通電極基板の製造方法は、ウェハ状の基板に前記基板を貫通しない複数の有底孔を形成し、前記基板及び前記有底孔の表面に絶縁膜を形成し、前記有底孔が開口する側の前記基板及び前記有底孔の絶縁膜上に金属からなるシード膜を形成し、前記シード膜に第1の時間直流電流を供給する電解めっき法により、前記シード層が形成されている面の前記有底孔の底部に金属層を形成し、前記シード膜及び前記金属層にパルス電流を供給する電解めっき法により、前記有底孔内に金属材料を充填して導通部を形成し、前記有底孔が形成されている側と反対側の前記基板の表面を、前記導通部の表面が露出するまで研磨する。

(もっと読む)

半導体装置の製造方法、半導体装置及び電子機器

【課題】半導体装置に含まれる貫通孔を微細化した場合であっても、メッキで貫通孔の内部に貫通電極を形成する。

【解決手段】半導体装置100の製造方法は、基板10の表面10a側にシード層30を形成するシード層形成工程と、シード層形成工程後、シード層30上に配線層40を形成する配線層形成工程と、配線層形成工程後、基板10の裏面10bからシード層30に達する貫通孔10cを形成する貫通孔形成工程と、貫通孔形成工程後、貫通孔10c内にメッキで貫通電極60を形成する貫通電極形成工程と、貫通電極形成工程後、シード層30を複数に分断する分断工程とを含んでいる。

(もっと読む)

基板貫通バイアを有する半導体構造および製造方法

【課題】基板を貫通するバイアホールを与える。

【解決手段】半導体デバイス構造は、第1の濃度および第1の導電型のバックグラウンドドーピングを有する基板を含んでなる。基板貫通バイアは基板を貫通している。デバイスは基板の第1の面上に第2の導電型の第1のドープ領域を有する。第2のドープ領域が基板貫通バイアの周りにある。第2のドープ領域は、第1の濃度よりも大きい第2の濃度にドーピングされており、第1の導電型を有する。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】貫通電極と配線との接続部位の抵抗のバラつきを低減させて、配線信頼性を向上させる。

【解決手段】貫通電極用の穴部を設け、配線層に対してオーバエッチングを施す。穴部に銅を埋め込むことにより、銅からなる貫通電極を形成させて、アルミニウムからなる配線と接続させた後、熱処理により貫通電極と配線とが接続される接触領域Gを合金化させることで、貫通電極と配線との抵抗バラつきを低減させて、配線信頼性を向上させる。本技術は、半導体装置と、その製造に適用することができる。

(もっと読む)

半導体装置の製造方法

【課題】貫通電極を効率良く形成する。

【解決手段】シリコン基板1にビアホール25を形成し、絶縁膜22を形成した後、ビアホール25に低誘電率膜31を埋め込む。ビアホール25内の低誘電率膜31の膜厚を異方性ドライエッチングによって所望の値に減少させる。この異方性ドライエッチングによって、絶縁膜22上の低誘電率膜31が除去される。続いて、ビアホール25内に導電材を埋め込み、トランジスタT1,T2上に多層配線を形成する。この後、シリコン基板1の裏面側を研磨して導電材を露出させると、貫通電極が形成される。

(もっと読む)

半導体チップ、これを含む半導体パッケージ、及びその製造方法

【課題】信頼性を向上させることができる高集積化された半導体チップ及びこれを含む半導体パッケージが提供される。

【解決手段】本発明にしたがう半導体チップは、基板と、前記基板を貫通している貫通ビアと、前記貫通ビアと前記基板との間に介在されたウェッティング膜と、前記ウェッティング膜と前記貫通ビアとの間に介在されたシード膜と、を含む。本発明の実施形態による半導体チップは突出された貫通ビアをウェッティング膜が覆っているので、導電パッドを追加に形成する必要がない。したがって、半導体チップの厚さを減らすことができ、構造が単純化されて半導体装置の高集積化により有利である。また、工程を単純化することができるので、生産収率を増大させ得る。

(もっと読む)

半導体装置、半導体パッケージ、半導体装置の製造方法及び半導体パッケージの製造方法

【課題】電気的接続信頼性を向上させることができる半導体装置を提供する。

【解決手段】半導体チップ3は、第1主面30Aと第2主面30Bとの間を貫通する貫通孔30Xを有する半導体基板30と、半導体基板30の第2主面30Bを覆うように形成され、貫通孔30Xと対向する位置に開口部31Xが形成された絶縁層31と、絶縁膜33によって覆われた貫通孔30X及び開口部31Xに形成された貫通電極32とを有する。絶縁層31から露出される貫通電極32の上端面は、当該半導体チップ3に他の半導体チップ4が積層される際のパッドになる。また、貫通電極32の上端面は、絶縁層31の半導体基板30と接する面と反対側の面と面一になるように形成されている。

(もっと読む)

半導体装置、および半導体装置の製造方法

【課題】配線抵抗の上昇や絶縁耐性の劣化を抑制しつつ、配線信頼性を確保する。

【解決手段】半導体装置100は、半導体基板と、半導体基板上に設けられた層間絶縁膜50と、層間絶縁膜50に埋め込まれた、Cuにより構成される配線10と、配線10の表層に設けられた、銅錯体を含有する表面層20と、を備える。配線10の表層に銅錯体を含有する表面層20を備えることにより、配線抵抗の上昇や絶縁耐性の劣化を抑制しつつ、配線信頼性を確保することができる。

(もっと読む)

半導体装置の製造方法

【課題】 絶縁膜に、底面及び側面の形状を良好に保って配線溝を形成する技術が望まれている。

【解決手段】 基板の上に、仮のパターンを形成する。仮のパターンを囲むように、基板の上に層間絶縁膜を形成する。層間絶縁膜を形成した後、仮のパターンを除去する。仮のパターンが除去されることによって現れた凹部の側面及び底面に、第1のバリア膜及びシード膜を形成する。シード膜の上に、配線材料を堆積させることにより、凹部を配線材料で埋め込む。

(もっと読む)

半導体装置の製造方法

【課題】高精細化に伴う、貫通孔の微細化とさらに高アスペクト化の貫通電極を有する半導体装置の製造方法を提案する。

【解決手段】半導体基板1の厚み方向に貫通する貫通電極4を有する半導体装置の製造方法であって、半導体基板1の第1の面1aから第1孔10を開口する第1の工程と、第1孔10を含む半導体基板1の第1の面1aに絶縁膜2を形成する第2の工程と、半導体基板1の第1の面1aと反対の面である第2の面1bから、少なくとも2つの第1孔10を含んで第1孔10へ貫通する第2孔11を開口する第3の工程と、第2孔11側よりスパッタ法によりシード層3を成膜する第4の工程と、シード層3に金属材料4aをメッキ法により半導体基板1の第1の面1aに達するまで第1孔10を埋める第5の工程と、半導体基板1の第2の面1bを第2孔11の深さ寸法より深く、厚み方向に研削する第6の工程と、を含む。

(もっと読む)

半導体装置、電子装置、配線基板、半導体装置の製造方法、及び配線基板の製造方法

【課題】配線基板に半導体素子を形成する場合において、配線基板の製造工程数を少なくする。

【解決手段】コア層200の一面上には、第1配線232が設けられている。第1配線232上、及びその周囲に位置するコア層200の一面上には、半導体層236が形成されている。第1配線232及び半導体層236は、半導体素子を形成している。本実施形態において半導体素子は、第1配線232をゲート電極としたトランジスタ230であり、半導体層236と第1配線232の間に、ゲート絶縁膜234を有している。

(もっと読む)

半導体装置及びその製造方法

【課題】基板貫通電極の周囲に形成される絶縁分離部において、埋め込まれる絶縁膜が接合面を有していると、基板裏面の研削後の絶縁分離部は、接合面が基板主面から基板裏面に達することで、機械的強度が低下しやすく、貫通電極に応力を印加した場合に絶縁分離部の内側領域が孤立しやすい。

【解決手段】絶縁分離部5に埋め込まれる絶縁膜を第1の絶縁膜3と第2の絶縁膜4の少なくとも2段の積層構造とすることで、第1の絶縁膜3の接合面3Sと第2の絶縁膜4の接合面4Sとが第2の絶縁膜4の底面の接合面のない領域で分断され、機械的強度が増加し、絶縁分離部の内側領域の孤立を阻止することができる。

(もっと読む)

半導体基板内の埋込ボイドを検出するための方法

【課題】半導体基板内又は基板上に形成された構造内の埋込ボイドを検出するための方法を提供する。

【解決手段】構造を形成するための少なくとも1つの処理ステップを実施する工程と、基板の質量M1を測定する工程と、熱処理を実施する工程と、基板の質量M2を測定する工程と、前記実施した熱処理の前後で測定した基板の質量の差を計算する工程と、前記質量の差を所定値と比較することにより、前記構造内の埋込ボイドの存在を推測する工程とを含む。

(もっと読む)

貫通電極を備えた配線基板とその製造方法

【課題】深孔相互間の距離を狭くする事ができ、深孔を微細化しても周囲の配線基板から及ぼされる応力の増加が防止でき、信頼性が保たれ、プロセス全体を低コストできる配線基板とその製造方法を提供する。

【解決手段】基体の主表面からその反対側裏面の両面に貫通する複数の貫通孔を備え、それらの孔が実質的に金属で埋められて貫通電極とされており、それらの内の少なくとも2以上の電極が電気的に並列に接続されている配線基板の製造方法であって、それらの2以上の孔を形成する場合に、それらの2以上の孔を含む領域より大きいサイズのマスクパターンを利用してそれらの2以上の孔を陽極酸化法を含む自己組織的穴明けプロセスにより所定の深さ以上の孔を形成した後に裏面から基体を削って、孔を裏面に露出させて貫通孔とする事を特徴とする配線基板の製造方法。

(もっと読む)

導電性ビアの製造と充填のための方法、およびそのように形成された導電性ビア

【課題】ビアホール表面上の絶縁コーティングとビアホール内に挿入される導電材料との付着性を向上する。

【解決手段】導電性ビアを形成する方法は、一つ以上のビアホールを基板内に形成するステップを含む。ビアホールは、単一マスク、保護層、ボンドパッド、もしくは、エッチングプロセスの間にフォトマスクが除去される場合にハードマスクとして機能する、基板のその他のフィーチャで形成され得る。ビアホールは、その表面に低誘電率(低K)誘電材料を含む誘電体コーティングの付着を促進するように構成されてもよい。障壁層が各ビアホールの表面の上に形成されてもよい。種材料(seed material)を含み得るベース層は、その後のビアホールの表面上の導電材料の選択的堆積を促進するように形成されてもよい。

(もっと読む)

導電性構成部品、貫通ビア及び導電性貫通ウェーハ・ビアを含む半導体構成部品を製造するためのプロセス及び集積化スキーム

【課題】公知のプロセスよりも高速であり、充てんされたビアにボイド、凹み又はキーホールを残さず、製造の費用効果が高い、改善された方法を提供する。

【解決手段】第1の表面214及び対向する第2の表面216を有する基板212を設け、基板の第1の表面に部分的にのみ前記基板の中に広がる少なくとも1つのブラインドビア218を形成する。酸化材料によって前記少なくとも1つのブラインドビアの表面をパッシベーションし、少なくとも一つのブラインドビアの酸化材料の表面に銅を含むシード材料228を、シード材料を前記少なくとも一つのブラインドビアの内部に閉じ込め、かつ、基板の前記第1の表面を露出させるように形成する。シード材料の上に導電性材料230を前記少なくとも一つのブラインドビアを充填するように無電解めっきし、少なくとも一つのブラインドビアの導電性材料を露出させるために基板の前記第2の表面に研磨平坦化を実施する。

(もっと読む)

半導体装置及びその製造方法

【課題】半導体基板を貫通する貫通電極の周囲に形成される環状の絶縁分離部において、絶縁分離部を構成する酸化膜の応力により絶縁分離部周囲の半導体基板が変形する。

【解決手段】絶縁分離部の基板側に深さ方向に圧縮応力を与える第1の膜4を形成し、第1の膜4上に深さ方向に引張応力を与える第2の膜6膜を形成し、その際、第1及び第2の膜の膜厚を圧縮応力と引張応力とがほぼ釣り合うように調整する。

(もっと読む)

基板中間体、基板及び貫通ビア電極形成方法

【課題】貫通ビア電極を形成する際に処理温度が高くなく且つ低コストで、バリア層を均一に、且つ高い密着強度で製造する。

【解決手段】シリコン基板10の厚さ方向に形成された高アスペクト比の、貫通ビア電極形成用の孔12の内周面に、自己組織化単分子膜24を形成し、これに、金属ナノ粒子14を、高密度で吸着させて、この金属ナノ粒子14を触媒として、バリア層を無電解めっきにより形成し、バリア層の上にシード層を無電解めっきにより形成し、次に、貫通ビア電極材を電解めっきにより堆積して、孔12を埋めて、貫通ビア電極を形成する。

(もっと読む)

1 - 20 / 337

[ Back to top ]