Fターム[5F033PP12]の内容

半導体集積回路装置の内部配線 (234,551) | 導電膜の成膜方法 (14,896) | CVD(化学的気相成長法) (3,065) | プラズマCVD (289)

Fターム[5F033PP12]に分類される特許

281 - 289 / 289

低k材料上にTaN拡散バリア領域を堆積する方法(低k材料上のTaN拡散バリア領域のPE−ALD)

【課題】低k材料上にタンタル−窒化物(TaN)拡散バリア領域を堆積する方法を提供する。

【解決手段】この方法は、チャンバにおいてタンタル系前駆物質および窒素プラズマからプラズマ増強原子層堆積(PE−ALD)を実行することによって、低k材料基板(102)上に保護層(104)を形成することを含む。保護層(104)は、そのタンタル含有量よりも大きい窒素含有量を有する。次いで、タンタル系前駆物質ならびに水素および窒素を含むプラズマからPE−ALDを実行することによって、次の実質的化学量論的タンタル−窒化物層を形成する。また、本発明は、このように形成したタンタル−窒化物拡散バリア領域(108)も含む。一実施形態において、金属前駆物質は、五塩化タンタル(TaCl5)を含む。本発明は、低k材料とライナ材料との間に鮮鋭な界面を生成する。

(もっと読む)

アモルファス炭素膜のCVD堆積用の液体前駆体

アモルファス炭素材料を堆積するための方法が提供される。一態様では、本発明は、処理チャンバに基板を位置決めするステップと、該処理チャンバに処理ガスを導入するステップであって、該処理ガスがキャリアガス、水素および1つ以上の前駆体化合物を含むステップと、二重周波数RF源から電力を印加することによって該処理ガスのプラズマを生成するステップと、該基板上にアモルファス炭素層を堆積するステップとを含む基板処理方法を提供する。 (もっと読む)

アモルファスカーボン膜を含む構造およびその形成方法。

【課題】 アモルファスカーボン膜を有する構造およびその形成方法を提供することである。

【解決手段】 半導体デバイスは、半導体基板と、半導体基板上に形成され、被処理膜を有する膜スタックとを含む。膜スタックに含まれるデュアルハードマスクは、アモルファスカーボン層、およびアモルファスカーボン層と被処理膜との間に配置される下層のハードマスク層を有し、ハードマスク層は、アモルファスカーボン層を含まない。金属配線のためのダマシン構造は、膜スタックに形成されている。アモルファスカーボン膜は、例えば、シングルダマシン構造またはデュアルダマシン構造の中で取り入れられることができる。アモルファスカーボン膜は、配線構造を形成するためのリソグラフィマスクの一部として役に立つことができ、または、それは、CMPの間、デュアルハードマスク、ケミカルメカニカルポリシング(CMP)ストップ層または犠牲層の上部層として役立つことになる。

(もっと読む)

多孔状基板上にパターン電極をコンタクトさせる方法とその素子

パターン電極素子をコンタクトさせる方法は、多孔状基板を作成するステップと、導電性材料をデポジットして多孔状基板の前面に少なくとも一つの電極を形成するステップと、該基板の背面に少なくとも一つの導電性背面コンタクトトレースをデポジットするステップと、を含む。導電性材料の一部分は基板に浸透する。素子は基板の前面に電極を含んで形成され、該電極は該基板を通して該背面コンタクトトレースまで該導電性材料を含む導電チャネルで電気的に結合される。  (もっと読む)

(もっと読む)

調整可能な反射防止コーティングを含む構造およびその形成方法。

【課題】 調整可能な反射防止コーティングを含む構造およびその形成方法を提供することである。

【解決手段】 調整可能なエッチング耐性反射防止(TERA)コーティングを含む配線工程(BEOL)アプリケーションにおける配線構造が記載される。TERAコーティングは、例えば、シングルダマシン構造またはデュアルダマシン構造の中で取り入れられることができる。TERAコーティングは、配線構造を形成するリソグラフィマスクの一部として役に立つことができ、または、それは、ハードマスクとして、ケミカルメカニカルポリシング(CMP)のストップ層として、またはCMP中の犠牲層として役立つことになる。

(もっと読む)

精密ポリシリコン・レジスタ・プロセス

【課題】 製造されるポリシリコン・レジスタのシート抵抗の許容誤差をより正確に制御する精密ポリシリコン・レジスタを製造するためのプロセスを提供する。

【解決手段】 プロセスは、一般に、部分的に形成されたポリシリコン・レジスタを有するウェハに対して、エミッタ/FET活性化高速熱アニール(RTA)を行うステップと、それに続いて、保護誘電体層をポリシリコン上に堆積させるステップと、ドーパントを該保護誘電体層を通して該ポリシリコンに注入して、ポリシリコン・レジスタの抵抗を定めるステップと、シリサイドを形成するステップとを含む。

(もっと読む)

半導体装置及びその製造方法

【課題】低抵抗且つ高バリア性を有するバリアメタルを提供する。

【解決手段】バリアメタル201 が、配線溝16の底面及び側壁の表面に沿って形成された膜厚16nmのTaN0.87膜31と、TaN0.87膜上に形成され、配線溝16に埋め込み形成されたCuダマシン配線17に接する膜厚4nmのTaN1.19膜32とから構成されている。

(もっと読む)

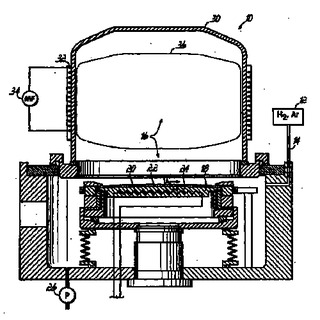

高温水素含有プラズマによるチャンバ及びウェーハ表面から物質を除去する方法及び装置

半導体ウェーハ処理装置(10)のチャンバ(16)と、清掃されるべき表面にバイアス電圧を掛けることなくガス混合物中に高密度プラズマを生成するためのみのICP電源と、に供給される、水素及び不活性ガスから成る清掃ガス混合物、例えば、水素含有量が体積で20%から80%の間にある混合物を使用する清掃方法が提供される。本発明の実施形態では、Si及びSiO2汚染物質又はCFx汚染物質は引き続く金属被着に先立ってシリコン・コンタクト(46)から清掃される。本発明の別の実施形態では、基準酸化物エッチング速度を回復するために酸化物をエッチングする以前にシリコン残留物は内部チャンバ表面から清掃される。

(もっと読む)

(もっと読む)

多層スピンオン多孔性誘電体からなるlow−k配線構造

【課題】その中にマイクロトレンチを含まない低誘電体層間絶縁膜金属導体配線構造およびそのような構造の形成方法を提供する。

【解決手段】導体抵抗に対する制御は、第1の原子組成を有する多孔性の低誘電体層間絶縁膜の線とバイア誘電体層との間に位置する第2の原子組成を有する埋込みエッチング停止層により行われる。本発明の配線構造は、また、二重波形模様タイプの配線構造を形成する際に助けになるハードマスクを含む。第1および第2の組成は、エッチング選択性が少なくとも10:1またはそれ以上になるように選択され、特定の原子組成および他の発見できる量を有する多孔性の低誘電体層間絶縁膜有機材料または無機材料の特定のグルーブから選択される。

(もっと読む)

281 - 289 / 289

[ Back to top ]