Fターム[5F033PP12]の内容

半導体集積回路装置の内部配線 (234,551) | 導電膜の成膜方法 (14,896) | CVD(化学的気相成長法) (3,065) | プラズマCVD (289)

Fターム[5F033PP12]に分類される特許

81 - 100 / 289

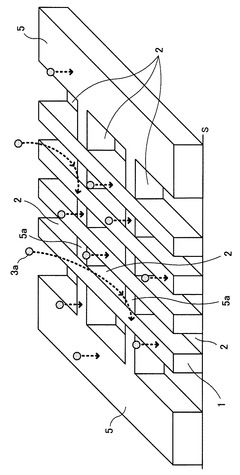

半導体装置の製造方法及び半導体装置

【課題】配線間容量の低い半導体装置を安定的に形成する。

【解決手段】配線1間に、仕切層5aで仕切られた複数の空洞の溝2を形成し、その後、それらの溝2を覆うように、配線1及び仕切層5aの上側に絶縁膜を形成する。配線1間に仕切層5aを設けることにより、絶縁膜形成に用いる絶縁膜原料3aの溝2内への進入が抑えられ、溝2内の絶縁膜形成が抑えられるようになる。それにより、配線1間の容量が低く、また、容量のばらつきが抑えられた半導体装置が形成可能になる。

(もっと読む)

半導体装置の製造方法

【課題】 極短時間アニール処理を行う際に、基板自体の損傷を抑制する半導体装置の製造方法を提供する。

【解決手段】 半導体基板上にゲート電極を形成する工程と、前記半導体基板に導電性の不純物を導入する工程と、前記半導体基板及び前記ゲート電極上に保護膜を形成する工程と、前記保護膜を形成後に前記半導体基板の裏面全面を研磨する工程と、前記半導体基板の裏面全面を研磨した後に前記半導体基板の表面が1000℃以上での保持時間が0.1秒以下となるような加熱処理により前記不純物を活性化する工程とを備えることを特徴とする半導体装置の製造方法。

(もっと読む)

多層配線層の電源配線構造およびその製造方法

【課題】互いに交差する上下の電源配線同士を中間配線層に形成される接続用配線を介して接続する際に、中間配線層での接続用配線によって占有される信号配線の配線トラック数を少なくする多層配線層の電源配線構造を提供する。

【解決手段】中間配線層のうち第1の方向を優先配線方向とする1つの中間配線層は、同種の上層電源配線と下層電源配線との交差位置に形成される交差位置形成部と、交差位置形成部から第1の方向の異なる種類の上層電源配線側に張り出した張出部と、を有するビア位置変換接続用配線24A,24Bを有し、配線接続部は、上層配線と交差位置形成部との間と、張出部と下層配線との間と、をビア21A,23A,25A,21B,23Bを介して接続する。

(もっと読む)

半導体デバイスおよび半導体デバイスの製造方法

【課題】シリコン貫通ビア(TSV)を用いて半導体ダイ接続部を作製するシステムおよび方法を提供する。

【解決手段】隣接するダイ501、505、507同士の間のダイ接続部に対して低抵抗経路を確立するとともに、複数のダイの間の貫通チャネルに対して低抵抗経路を提供するために、ビアファーストのTSV401およびビアラストのTSV403の両方を用いて半導体ダイが製造される。

(もっと読む)

半導体集積回路装置の製造方法

【課題】ニッケル系メタル・シリサイドとコンタクト用メタル間でのコンタクト抵抗の低抵抗化がホールの微細化に伴って、困難になるという問題がることが、本願発明者の検討により明らかとなった。

【解決手段】本願の一つの発明は、ニッケル系メタル・シリサイドによりソース・ドレイン領域等のシリサイデーションを施したMISFETを有する半導体集積回路装置の製造方法において、プリ・メタル絶縁膜に設けられたコンタクト・ホールにバリア・メタルを形成する前に、シリサイド膜の上面に対して、窒素水素間結合を有するガスを主要なガス成分の一つとして含む非プラズマ還元性気相雰囲気中で、熱処理を実行するものである。

(もっと読む)

半導体装置の製造方法

【目的】従来よりも比抵抗の低いW膜のプラグ或いは配線が得られる半導体装置の製造方法を提供することを目的とする。

【構成】本発明の一態様の半導体装置の製造方法は、基体上に絶縁膜を形成する工程(S104)と、前記絶縁膜に開口部を形成する工程(S106)と、前記開口部の少なくとも底面に、ルテニウム(Ru)膜を形成する工程(S112)と、前記Ru膜が形成された前記開口部内に、水素(H2)還元による化学気相成長(CVD)法によりタングステン(W)膜を埋め込む工程(S114)と、を備えたことを特徴とする。

(もっと読む)

被処理体の成膜方法及び処理システム

【課題】線幅やホール径が小さな凹部や高アスペクト比の凹部に対して十分な埋め込みを行うことが可能な成膜方法を提供する。

【解決手段】凹部6を有する絶縁層4が表面に形成された被処理体Wに対して薄膜を形成する成膜方法において、前記凹部内の表面を含めて前記被処理体の表面にTiを含むバリヤ層12を形成するバリヤ層形成工程と、前記バリヤ層上にRuを含むシード層16を形成するシード層形成工程と、前記シード層上に前記シード層に対する導通性を補助するためにCuを含む補助シード層164を形成する補助シード層形成工程とを有する。

(もっと読む)

Cu膜の成膜方法および記憶媒体

【課題】平滑で高品質のCVD−Cu膜を成膜することができるCu膜の成膜方法を提供すること。

【解決手段】チャンバー内にウエハを搬入し、安定化させた後、ウエハを加熱しつつチャンバー内にCu錯体からなる成膜原料を気相状態で導入してウエハ上にCVD法によりCu膜を成膜し、成膜後、チャンバー内をパージして残留ガスを除去し、その後、チャンバーから基板を搬出するCu膜の成膜方法を実施するにあたり、パージの際に、ウエハへの入熱をCu膜成膜の際よりも低下させる。

(もっと読む)

Cu膜の成膜方法および記憶媒体

【課題】平滑で高品質のCVD−Cu膜を下地に対して高い密着性をもって成膜することができるCu膜の成膜方法を提供すること。

【解決手段】チャンバー1内にCVD−Ru膜を有するウエハWを収容し、チャンバー1内に、成膜中に発生する副生成物であるCu(hfac)2の蒸気圧がその蒸気圧よりも低いCu錯体であるCu(hfac)TMVSからなる成膜原料を気相状態で導入して、ウエハWに形成されたCVD−Ru膜上にCVD−Cu膜を成膜するにあたり、チャンバー1内の圧力をCVD−Ru膜表面に吸着したCu(hfac)2の脱離および拡散が進行する圧力に制御する。

(もっと読む)

Cu膜の成膜方法および記憶媒体

【課題】平滑で高品質のCVD−Cu膜を成膜することができるCu膜の成膜方法を提供する。

【解決手段】ウエハW上の絶縁膜にビアホールとトレンチを形成し、この上にバリア層としてCVD−Ru膜を成膜する。チャンバー1内にウエハWを収容し、チャンバー1内に1価Cuβジケトン錯体であるCu(hfac)TMVSと、これを還元するアンモニア、還元性Si化合物、カルボン酸などの還元剤とを気相状態で導入して、ウエハW上にCVD法によりCu膜を成膜する。

(もっと読む)

成膜方法及びプラズマ成膜装置

【課題】ステップカバレジを向上させることができ、これによりスループットも高く維持することが可能な成膜方法及びプラズマ成膜装置を提供する。

【解決手段】真空排気が可能になされた処理容器22内へ凹部6を有する絶縁層4が表面に形成された被処理体Wを収容すると共に前記処理容器内へ原料ガスを供給してプラズマCVD法により前記被処理体に対してチタンを含む薄膜を形成する成膜方法において、前記薄膜の形成時の前記処理容器内のプロセス圧力を230〜630Paの範囲内に設定する。これにより、ステップカバレジを向上させることができ、スループットも高く維持することが可能となる。

(もっと読む)

成膜方法及びプラズマ成膜装置

【課題】全体としてのコンタクト抵抗を小さく維持しつつバリヤ性の高い薄膜の成膜方法及びプラズマ処理装置を提供する。

【解決手段】凹部6を有する絶縁層4が表面に形成された被処理体Wに対して薄膜を形成する成膜方法において、前記凹部内の表面を含む前記被処理体の表面にプラズマCVD法を用いて窒化チタン膜10の薄膜を形成する薄膜形成工程と、窒化ガスの存在下でプラズマを用いた窒化処理を行うことにより前記薄膜を窒化する窒化工程と、を有することを特徴とする成膜方法である。これにより、抵抗を小さく維持しつつバリヤ性の高い薄膜を形成する。

(もっと読む)

カーボンナノチューブ及びその製造方法

【課題】 CoWP上でのカーボンナノチューブ作製方法を提供する。

【解決手段】 本発明のカーボンナノチューブ配線構造の製造方法は、Cu配線上のCoを含むめっき層をプラズマ処理するプラズマ処理工程と、前記プラズマ処理工程の前又は後に前記Coを含むめっき層に、カーボンナノチューブ成長用の助触媒を付与する助触媒付与工程と、前記プラズマ処理工程及び助触媒付与工程より後に前記Coを含むめっき層及び前記Coを含むめっき層に付与された前記助触媒を加熱処理する加熱処理工程と、前記加熱処理工程より後に、プラズマCVD法によるカーボンナノチューブ成長工程とを備えたことを特徴とする。

(もっと読む)

金属層間誘電体による拡散防止バリヤ層を有する集積回路およびその製造方法。

【課題】ライン間キャパシタンスを減少できる構造を有する集積回路および不純物が多層集積回路構造の次の層に存在する導電性要素に対し破壊的反応を起こすのを防止できる集積回路の製造方法を提供する。

【解決手段】低誘電率材料中での不純物の移動を防止できるキャップ層あるいはバリヤ層により、不純物が多層集積回路構造の次の層に存在する導電性要素に対し破壊的反応を起こすのを防止する。集積回路は第一の誘電体層と集積回路のより上層の導電層間に拡散防止バリヤ層を堆積して製造される。拡散防止バリヤ層はその次の金属層で不純物を含む誘電体層へその場で形成され、さらに、研磨を含む処理が多層誘電体構造に対してなされる。キャップ層あるいはバリヤ層にその場堆積は不純物を含む層を雰囲気にさらすのを防止し、そしてキャップ層あるいはバリヤ層により、水分、水素あるいはそのたのものにより、層が汚染されるのを防止することができる。

(もっと読む)

高アスペクト比プラグの充填方法

【課題】高アスペクト比を有するプラグを充填する方法を提供する。

【解決手段】高アスペクト比を有するプラグを充填する本発明の方法においては、核形成層を、バイアの側壁上ではなく、バイアの底に形成する。プラグ充填はバイアの底からトップへの方向であり、側壁から内側へではない。得られるプラグは、無ボイドであり、継ぎ目無しである。

(もっと読む)

半導体装置及びその製造方法

【課題】絶縁膜の寄生容量を低減させて、配線の微細化させた半導体装置を効率よく製造できる方法を提供する。

【解決手段】有機材料からなる低誘電率絶縁膜3を形成した後、電子ビームを照射して低誘電率絶縁膜3の表面側にメチル基の濃度が相対的に低く、親水性を有する改質層31を形成する。さらに、エッチングによって低誘電率絶縁膜3に配線やコンタクトホールなどの溝パターン6を形成し、Cuからなるめっき層10を析出させる。CMP法による研磨で改質層31の少なくとも一部を研磨し、Cuからなる配線や導電性プラグといった導電性パターン11を形成する。

(もっと読む)

誘電ライン・バイアのエレクトロマイグレーション耐性が向上した界面層を有する相互接続構造およびその製造方法

【課題】 相互接続構造内にガウジング・フィーチャを導入することなくエレクトロマイグレーション耐性を向上させる相互接続構造を提供する。

【解決手段】 この構造は、バイア開口の底部に存在する金属界面層(または金属合金層)を含む。バイア開口は、第1の導電材料が埋め込まれた第1の誘電材料の上に位置する第2の誘電材料内に位置する。バイア開口の底部に存在する金属界面層(または金属合金層)は、第1の誘電体内に埋め込まれた下にある第1の導電材料と第2の誘電材料内に埋め込まれた第2の導電材料との間に位置する。また、エレクトロマイグレーション耐性が向上した相互接続構造を製造する方法も提供する。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】溝の交差部分の中央部に窪みが形成されることを抑制でき、かつ半導体装置の歩留まりが低下することを抑制できる半導体装置の製造方法を提供する。

【解決手段】この半導体装置の製造方法は、基板100に第1の溝110及び第1の溝110と交差する第2の溝120を形成する工程と、基板100に対して成膜処理を行うことにより、第1の溝110内及び第2の溝120内に膜200を埋め込む工程と、基板100上に位置する膜200を除去する工程とを備える。そして第1の溝110及び第2の溝120を形成する工程において、第1の溝110と第2の溝120の交差部分130に、平面視において交差部分130の角の一つから交差部分130の中央に向けて延伸する凸部140を形成する。

(もっと読む)

電子デバイスの製造方法

【課題】成膜時に生じる反りを緩和しうる電子デバイスの製造方法を提供する。

【解決手段】まず、4H−SiC基板10の第1面10aの上に、第1タングステン膜11を堆積する。堆積は、基板温度を400℃〜600℃に保持した状態で、スパッタによって行われる。スパッタ後に室温まで冷却すると、基板全体が上方に凹になるように反る。その後、4H−SiC基板10の第2面10bの上に、同じ材質、厚さの第2タングステン膜12を堆積する。4H−SiC基板10に対する,第1,第2タングステン膜11,12の収縮による応力が互いに釣り合い、反りがなくなる。その後、平坦な基板上にレジスト膜Reを形成して、第1タングステン膜11から注入マスク11aを形成する。正確な注入マスク11aを用いて、高い精度で不純物拡散領域15を形成する。

(もっと読む)

電子デバイス及びその製造方法

【課題】塗布プロセス(印刷やIJ)により製造が可能であって、電磁波照射による異常放電がなく、生産効率及び生産安定性が高く、かつキャリア移動度及びon/off比が向上した電子デバイス及びその製造方法を提供することにある。

【解決手段】基板上に、電極を有し、少なくとも1部に熱変換材料または熱変換材料を含むエリアと、前記熱変換材料または熱変換材料を含むエリアに隣接もしくは近接して電磁波吸収能を持つ物質または電磁波吸収能を持つ物質を含むエリアを配置し、電磁波を照射して、該電磁波吸収能を持つ物質が発生する熱により、熱変換材料を機能材料に変換する電子デバイスの製造方法において、前記電極の辺が形成する角が全て90°より大きく180°より小さい、または、曲面であることを特徴とする電子デバイスの製造方法。

(もっと読む)

81 - 100 / 289

[ Back to top ]